根据基于802.11a协议的OFDM发射物理层基带数据处理(part1)-优快云博客补充用户数据来源。

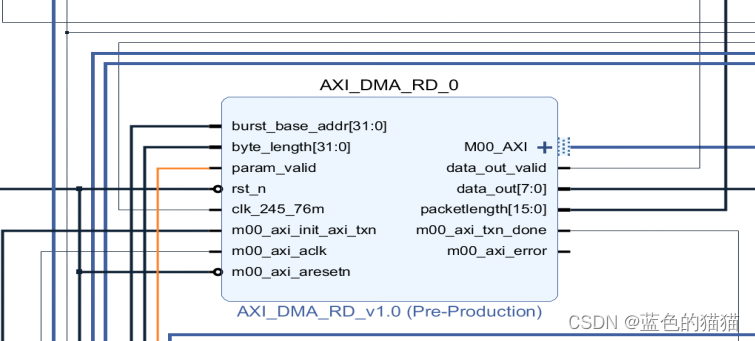

模块实现功能:带有AXI接口的DMA读模块,从内存中读取用户数据作为OFDM调制TX模块数据输入,(内设FIFO实现跨时钟(100M转245.76M)、数据位宽转换(64bit转8bit)。

AXI接口配置:突发数据长度配置256,数据位宽是64位。单次突发传输2048个字节。

输入信号说明:

1、输入:burst_base_addr:输入要从内存读取首个字节的突发地址,AXI总线输出读地址时(记得加上读取从机DDR的基地址,与PS端配置一致)。

2、输入:param_valid:开始读内存数据的控制信号。

3、输入:packetlength:控制输出数据长度。

AXI输出信号说明:主要控制的AXI的读地址通道,和读数据通道;

1、输出M_AXI_ARADDR:从机基地址+burst_base_addr。

2、输出M_AXI_ARVALID(检测到param_valid后拉高,直到读地址通道完成匹配,输入M_AXI_ARREADY为高时,拉低)

3、M_AXI_RREADY 输出读ready信号,检测到读地址通道匹配成功(即ready和valid同时为高)后拉高,从内存中读取的数据达到突发长度(这里设置256)后,拉低,等待再次触发param_valid。

内部FIFO控制:(写100M,64bit 读245.76M,8bit)

本文介绍了一个带有AXI接口的DMA模块,用于在FPGA中实现PS与PL数据交互。模块包括DMA读模块,读取DDR内存数据供OFDM TX模块使用,以及DMA写模块,将OFDM RX模块处理后的数据写回DDR。AXI接口配置为突发长度256,数据位宽64位,通过FIFO实现跨时钟域和数据位宽转换。模块通过检测信号控制AXI读写地址和数据通道,确保数据的连续传输。此外,文章还讨论了AXI总线协议和相关时序,以及DMA在高速数据传输中的作用。

本文介绍了一个带有AXI接口的DMA模块,用于在FPGA中实现PS与PL数据交互。模块包括DMA读模块,读取DDR内存数据供OFDM TX模块使用,以及DMA写模块,将OFDM RX模块处理后的数据写回DDR。AXI接口配置为突发长度256,数据位宽64位,通过FIFO实现跨时钟域和数据位宽转换。模块通过检测信号控制AXI读写地址和数据通道,确保数据的连续传输。此外,文章还讨论了AXI总线协议和相关时序,以及DMA在高速数据传输中的作用。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3453

3453

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?