前言

DFT技术中有一种成为at-speed的技术,可以用来测试电路正常工作的时序是否有问题,进而确定电路能否正常工作。这种技术测试的故障叫做transition fault,同样这种技术也叫transition fault test。

想要实现这种技术,一对测试pattern(V1, V2), 需要应用到测试电路当中(Circuit Under Test, CUT)。 V1用来初始化电路,或者叫给整个电路的所有触发器赋上一个初值,V2作为触发一个0到1,或者1到0的翻转,然后在一个时钟后进行捕获结果。注意,这里的时钟周期需要和正常功能模式下的时钟周期保持一致,以获得最接近实际的测试效果。

整个过程需要三个周期:

- 初始化,Initialization Cycle(IC),即对整个电路初始化需要的一个时钟周期

- 发射,Launch Cycle(LC),在目标触发器启动一个指定的翻转

- 捕获,Capture Cycle(CC),捕获经过组合逻辑的计算结果

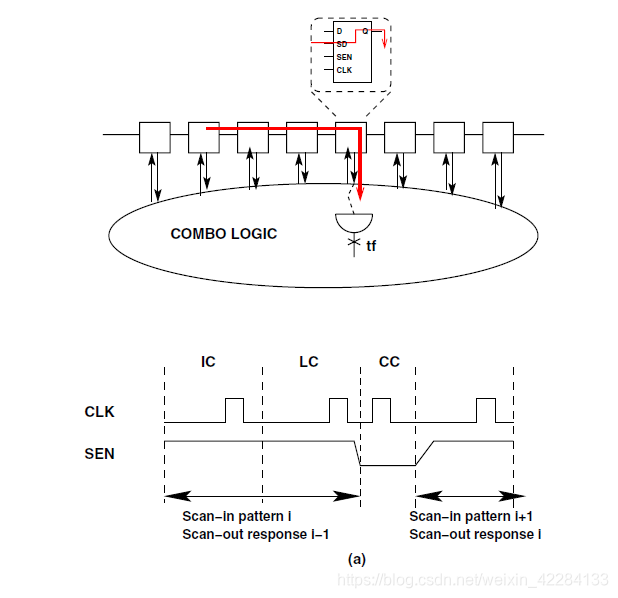

Launch Off Shift (LOS)

又叫Skewed-Load,如下面的时序图所示,LOS测试的时候,scan enable的低电平会维持一个时钟脉冲。这样,launch发生在最后一次shift的那个周期,通过SD-Q传入组合逻辑,经过组合逻辑之后在下一个时钟上升沿被采样,即捕获,然后再将其依次shift出去。

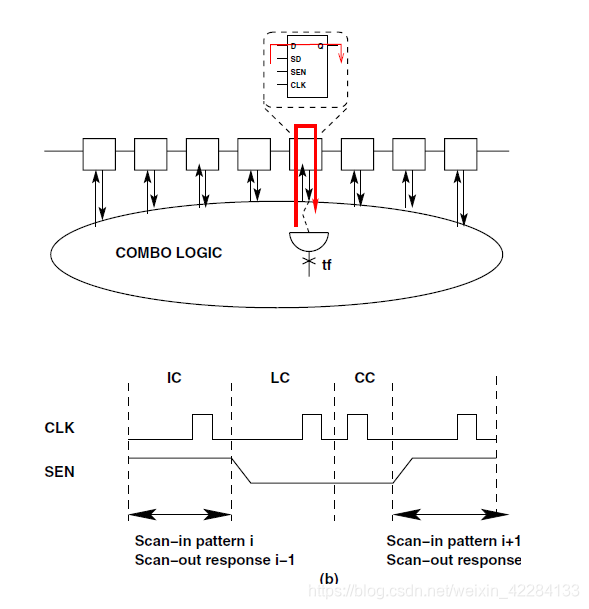

Launch Off Capture (LOC)

又叫Broad-Side, 如下面的时序图所示,LOC测试的时候,scan enable的低电平会维持两个时钟上升沿。这样第二个时钟沿的采样过程就更加接近电路实际工作的情况,数据从前一级的D-Q进入组合逻辑,然后再被捕获。

222

222

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?