HMC7044和LMK0482x芯片是配合ADC/DAC常用的芯片,这两颗芯片都可以国产化了。常规的设计我们在此就不提了,主要是关键要注意的点:

1.输入时钟信号的功率

CLKINx、RFSYNC 和OSCIN 内部都有差分100欧电阻,单端50欧(软件需要配置)匹配;因为输出共模电压为2.1V,故最大信号不超过3.3V。那么输入的功率最大为+5dBm。

2.时钟输出对的选择

同1组时钟,且同1组电源:各组时钟输出偏斜最小,但是隔离度也最差。故将连续时钟输出的信号隔离在不同的电源域中。物理上距离最远的电源对应时钟组,隔离度最大。

3.sync信号同步

PLL2的SYNC FSM 建议开启(SYNC_enable),等PLL1和PLL都输出后,给一个SYNC 高脉冲信号,复位通道分频器相位,进行多片HMC7044同步。通过SPI 发送同步请求(置位Reseed_request 位),对齐通道分频器输出信号相位。

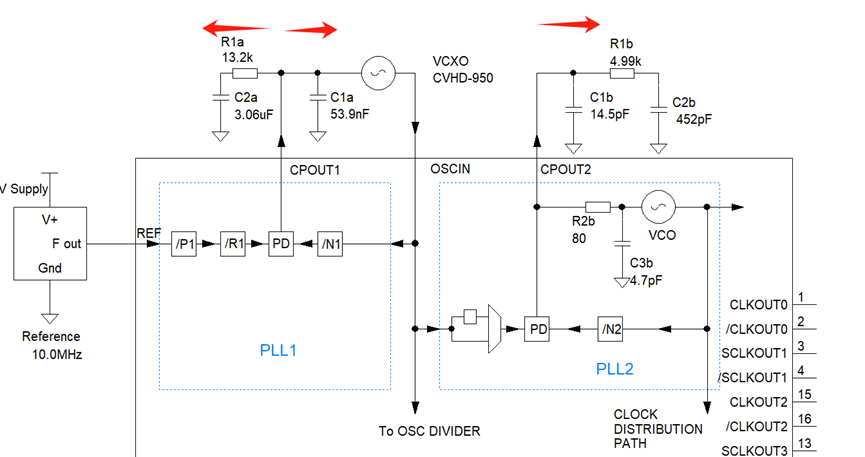

4.PLL1的设置

PLL1 为窄带系统(20Hz~500Hz)。PLL1 噪声曲线通常取决于环路带宽、输入参考噪声和 VCXO 特性。设置PFD1的鉴相频率(一般为几MHz~10MHz)位于PFD2的环路带宽之外, 从而提高7044的输出噪声性能。

5.PLL2的设置

PLL2是把VCXO的频率倍频到VCO频率,典型环路带宽为100kHz~700kHz,提高鉴相位频率,每个VCO的性能不一样;

6.占空比可能对性能有影响

LMK04828输出要选择占空比校正 (DCC)参数。A/D时钟为VCO频率时,可分别对比DCLKoutX_MUX=0、1和2的性能指标差异。

7.PLL环路配置案例:外参考10MHz,VCXO 100MHz,VCO为2400MHz:

优数科技的LAN-402(短波、超短波)、FMC-702(2路1.25Gsps收,2路12Gsps发)、FMC-704(2路3Gsps收,2路12Gsps发)等板卡上,可以用来调试HMC7044。在FMC-708(2路3Gsps收,2路12Gsps发)上,可以用来调试LMK04828

4154

4154

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?