一、单位宽信号跨时钟域处理

1.1 采用xpm_cdc_single原语实现(推荐)

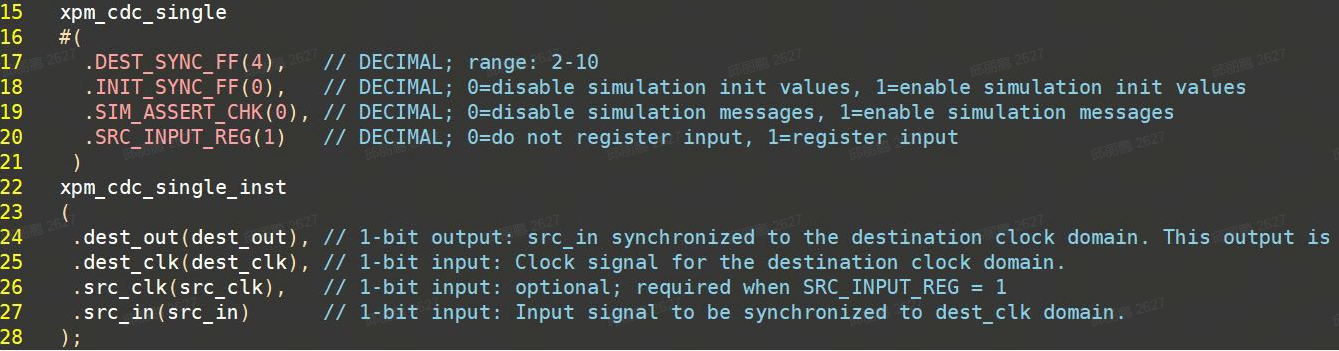

- DEST_SYNC_FF参数:级联触发器的个数,取值范围为2~10;

- INIT_SYNC_FF参数:仿真初始值;

- SIM_ASSERT_CHK参数:仿真检查;

- SRC_INPUT_REG参数:对输入信号寄存器打拍(源时钟域);

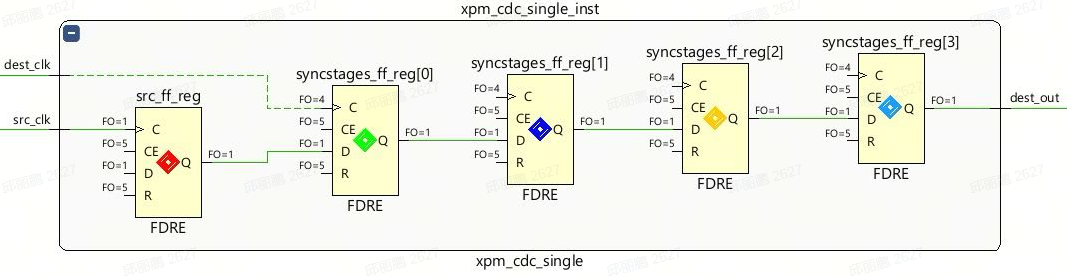

按照上图参数例化,综合电路如下:

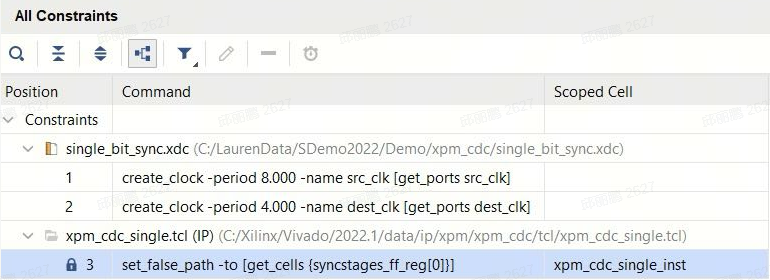

从结果上看,第一个触发器FDRE是在src_clk(源时钟域)下,后续4个触发器是在dest_clk(目标时钟域)下。同时,xpm_cdc_single自带约束,将红色标记触发器到绿色标记触发器之间的路径,设置为伪路径(set_false_path)。

1.2 采用源码实现

PS:以下源码,仅支持单脉冲有效的信号跨时钟域处理,突发数据信号的跨时钟域处理请使用异步FIFO。

- 低频率跨到高频率(

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?