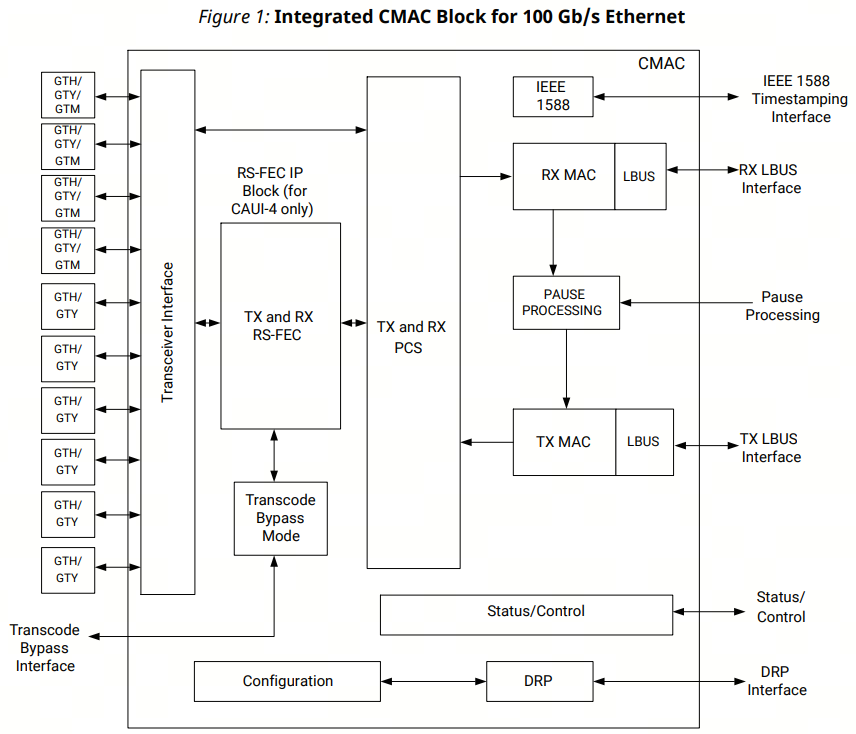

一、结构框图

二、工作原理

2.1 高速串行收发器

SERDES(Serializer/Deserializer,串行器/解串器)是高速数据传输中常用的接口技术,用于将并行数据转换为串行数据(减少I/O引脚数量),并在接收端恢复为并行数据。GTH、GTY、GTM是Xilinx(赛灵思)公司针对不同FPGA/SoC器件家族推出的高速SERDES收发器系列,主要差异在于支持的速率、工艺节点、协议灵活性及应用场景。以下是具体说明:

2.1.1 GTH(Gigabit Transceiver High-Speed)

器件家族:主要用于Xilinx 7系列FPGA(如Virtex-7、Kintex-7、Artix-7)。

速率范围:支持1.25 Gbps到12.5 Gbps的串行速率(部分器件可达到13.1 Gbps)。

主要协议:支持PCIe 3.0(8 Gbps)、10G Ethernet(10.3125 Gbps)、SATA 3.0(6 Gbps)、CPRI(Common Public Radio Interface,通用公共无线电接口)等。

应用场景:中高速数据传输场景,如企业级网络设备(交换机、路由器)、工业控制、医疗影像、测试测量设备等。

特点:性价比高,适合对速率要求较高但无需极致性能的应用,是7系列FPGA的主流高速接口方案。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1757

1757

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?