一、设计需求

- 晶振频率25MHz

- 支持16个1G口

- 支持4个10G口

- 1G口用户侧AXI接口数据总线8bit,接口频率125MHz

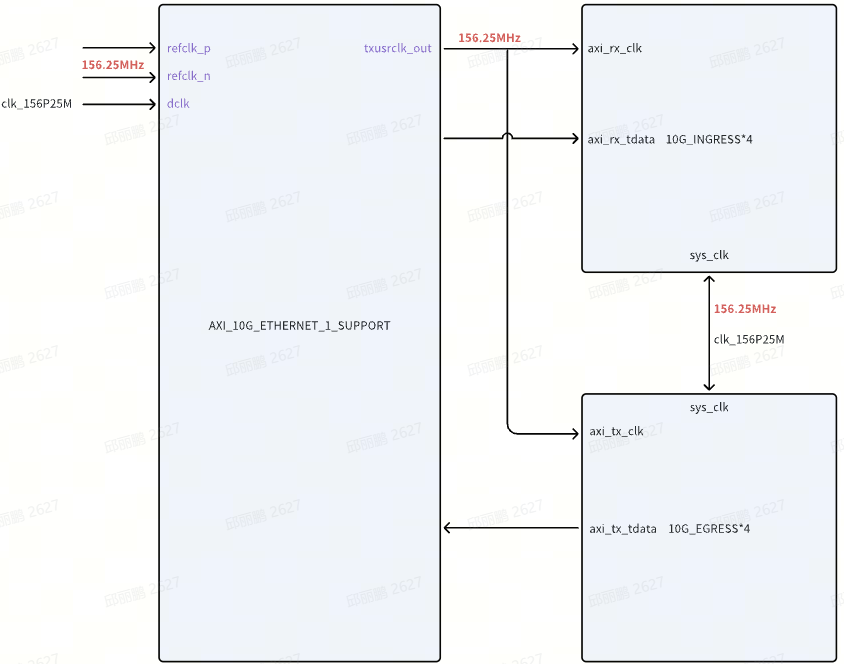

- 10G口用户侧AXI接口数据总线64bit,接口频率156.25MHz

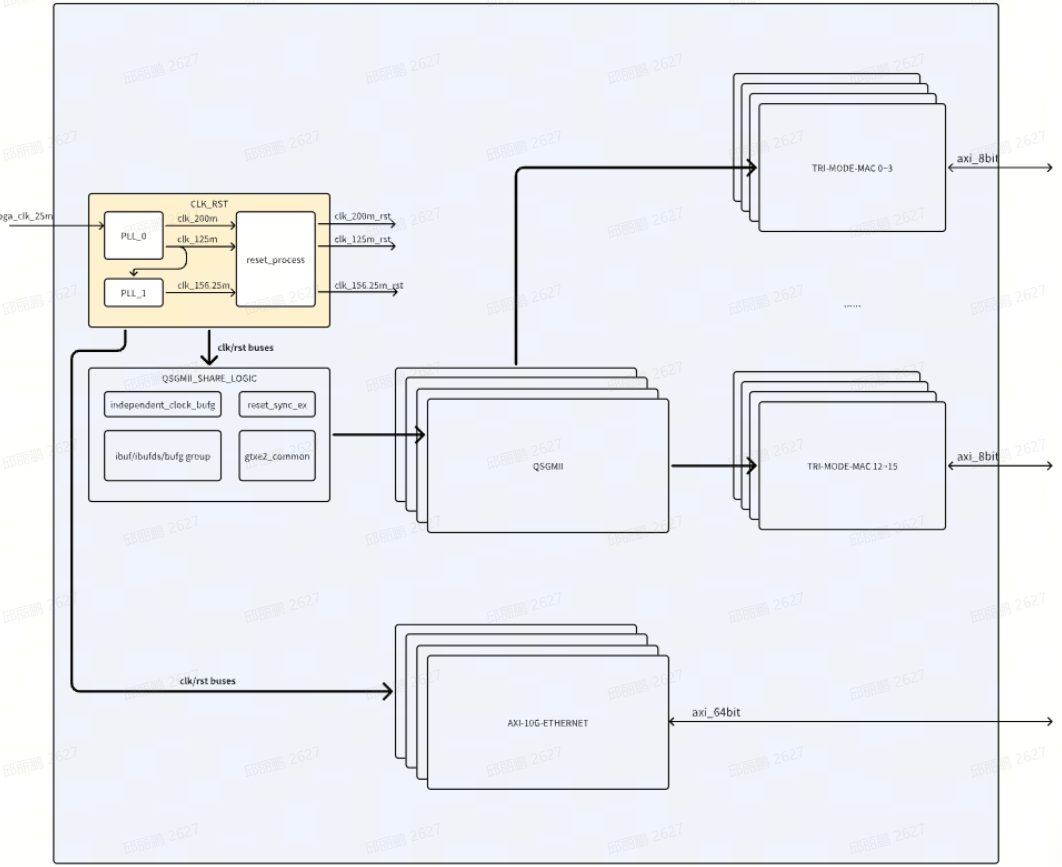

二、设计框图

图1 总体框图

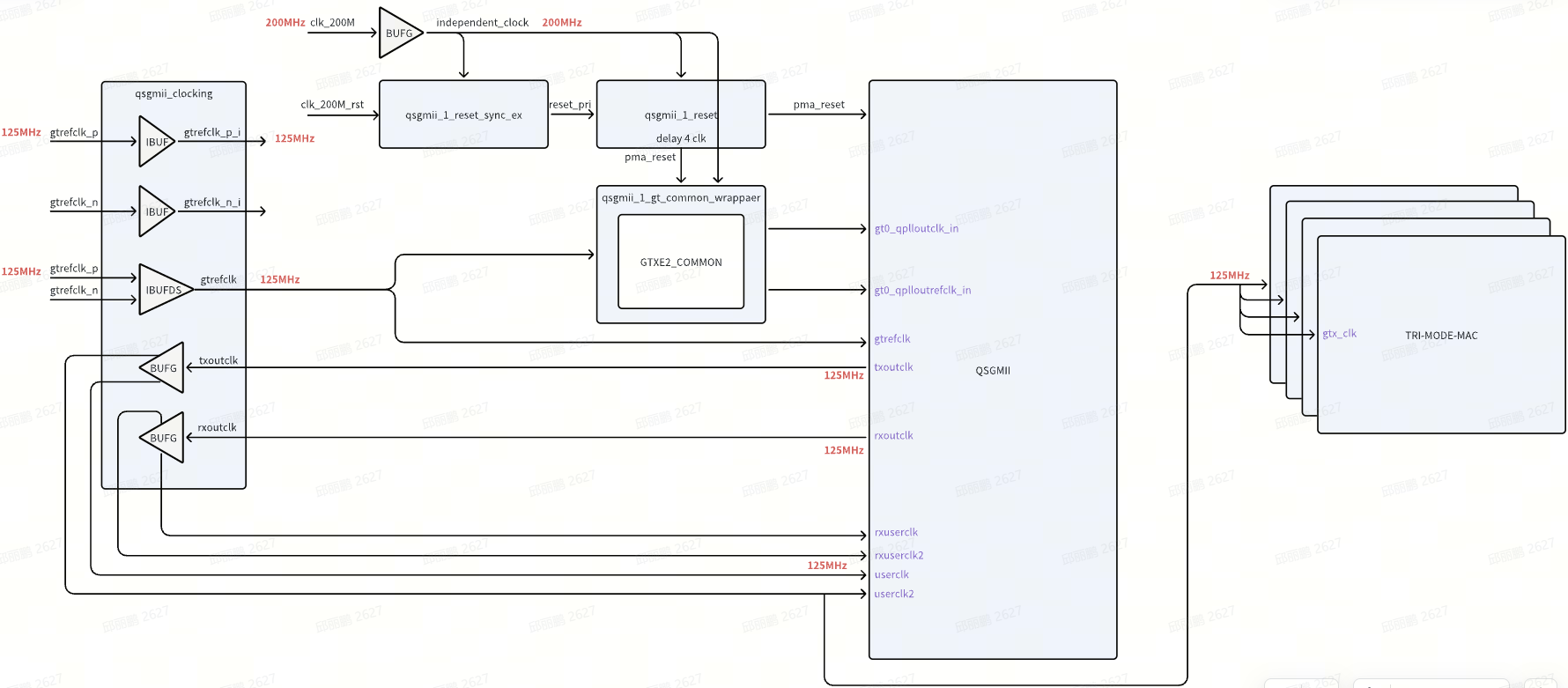

图2 1G接口时钟网络(1*QSGMII+4*Tri-mode-mac)

图5 10G接口设计

三、设计说明

3.1 CLK_RST模块

输入外部晶振时钟25MHz,例化2组PLL。其中,PLL_0产生clk_200m和clk_125m时钟,PLL_1产生clk_156p25m时钟。reset_process组件分别产生三个时钟域下的复位信号。

clk_200m时钟用于QSGMII作为independent_clock时钟输入,产生pma_reset。

clk_125m时钟用于产生QSGMII的gtrefclk参考时钟。

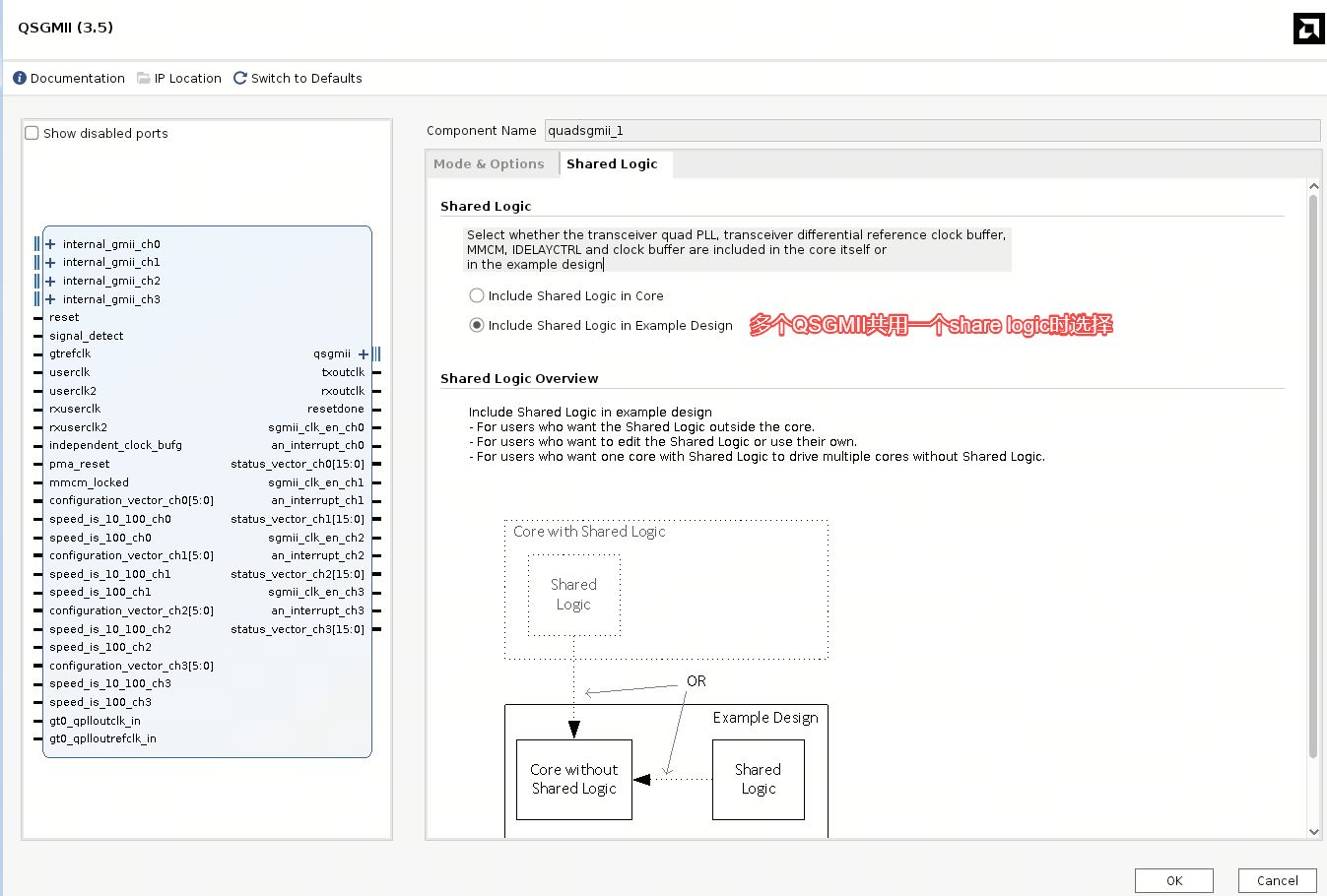

3.2 QSGMII SHARE LOGIC模块

从QSGMII IP Core独立出来的共享逻辑,产生的gtrefclk、gt0_qpllout_clk、gt0_qplloutrefclk为4个QSGMII IP共用,以减少GTXE2_COMMON、IBUFDS_GTE2、BUFGCTRL等资源消耗。注意:共用资源的4个QSGMII serdes管脚在分配IO时,必须在同一个QUAL(相邻),否则nets将可能无法routing导致design_opt阶段编译失败。

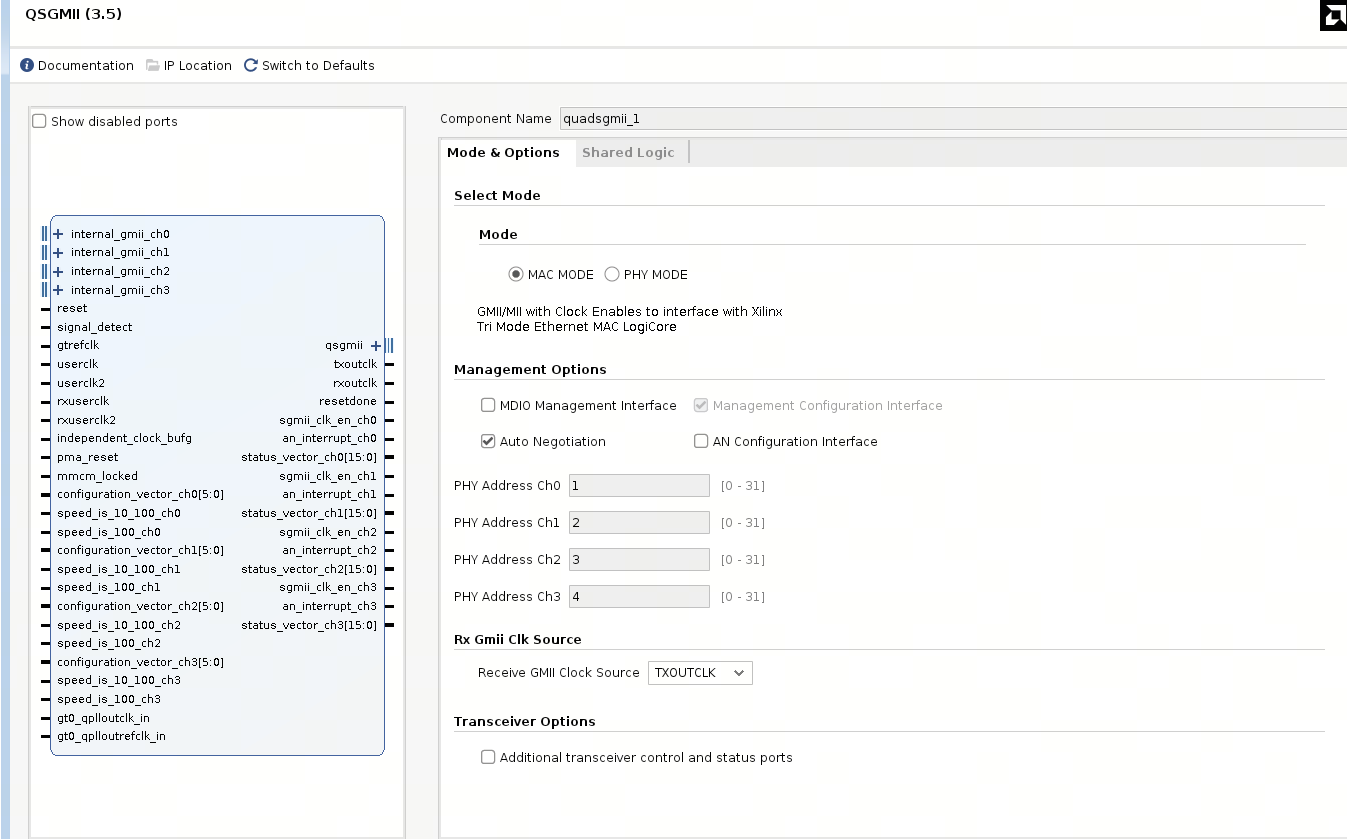

3.3 QSGMII

本设计采用4组QSGMII,每组QSGMII外接4个TRI-MOD-MAC(10/100/1000M 三速MAC),配置如下:

其他功能配置,参见Xilinx PG029文档。

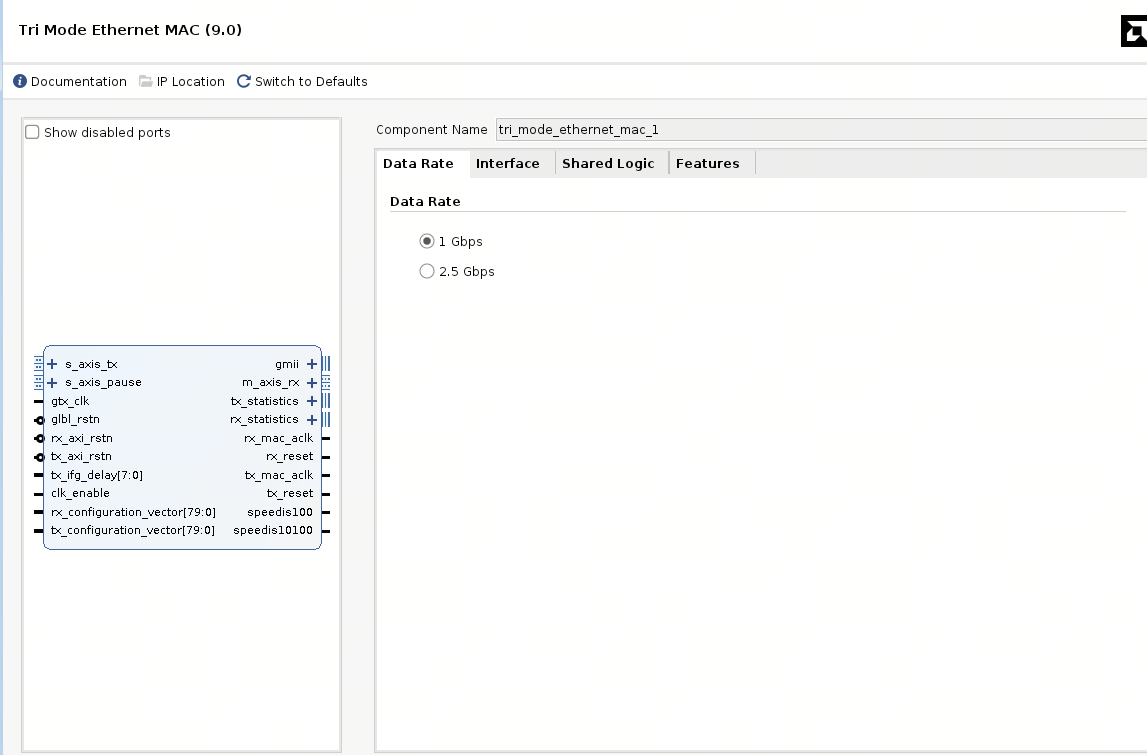

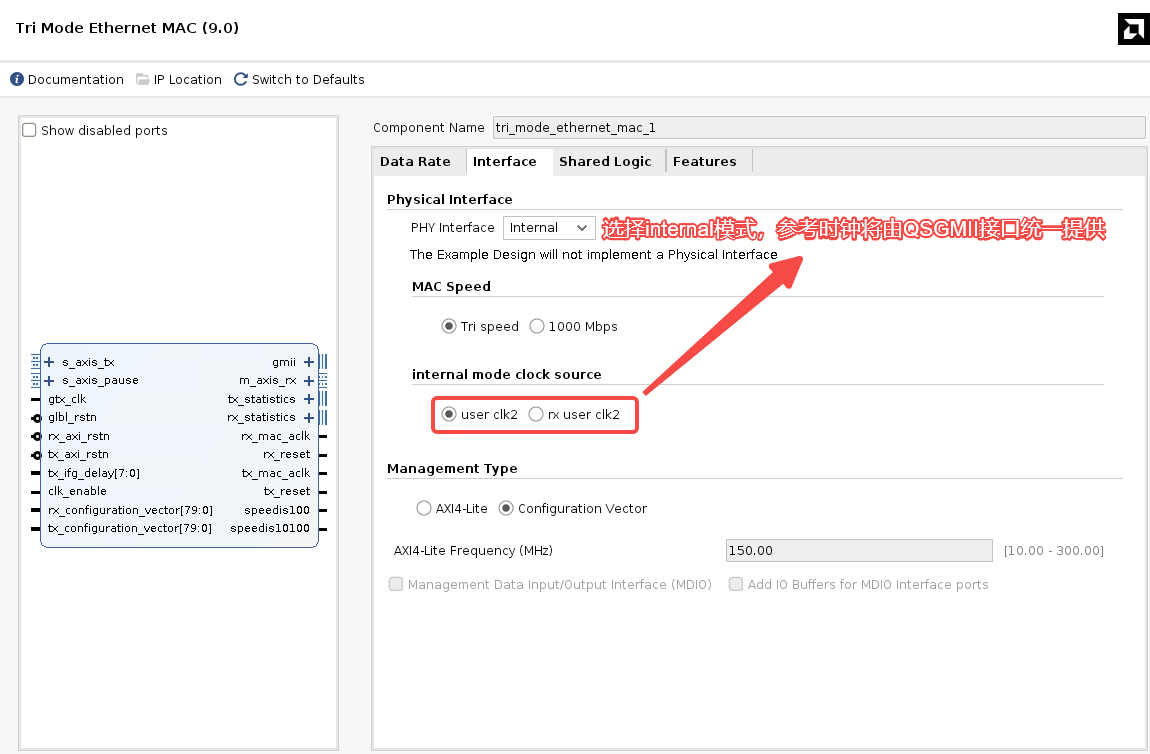

3.4 TRI-MODE-ETHERNET-MAC

本设计采用16组10/100/1000M 三速MAC IP,每组QSGMII连接4组MAC。配置如下:

其他功能配置,参见Xilinx PG029文档。

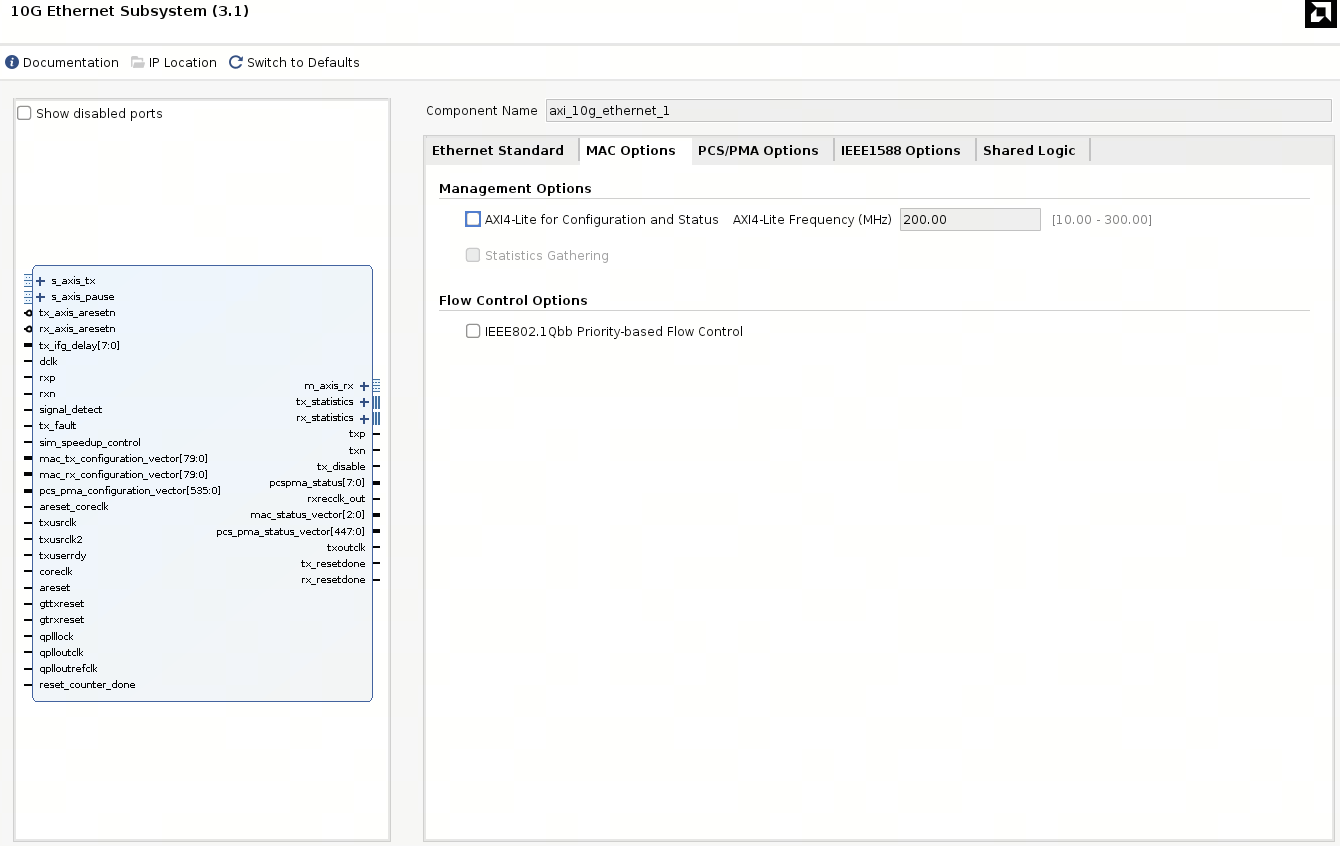

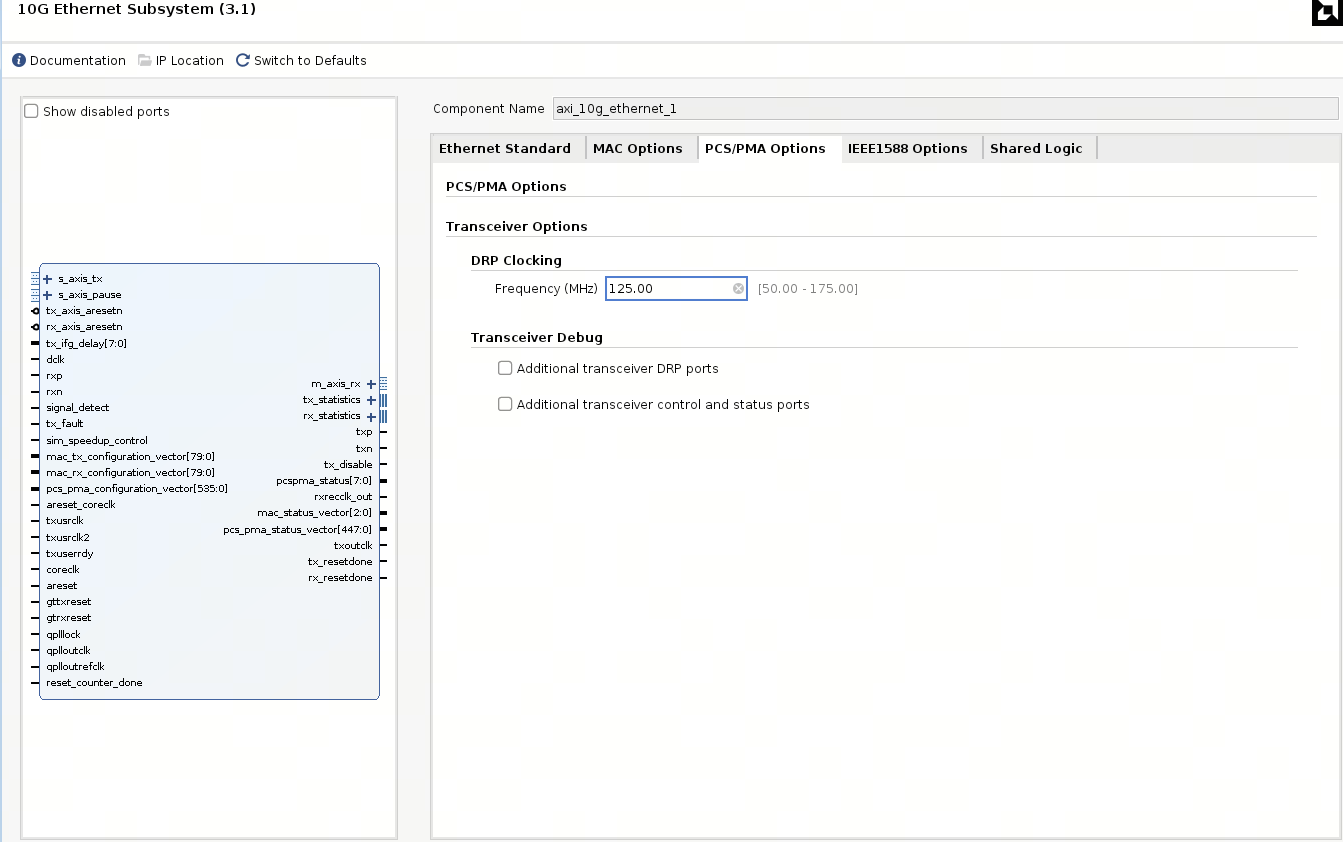

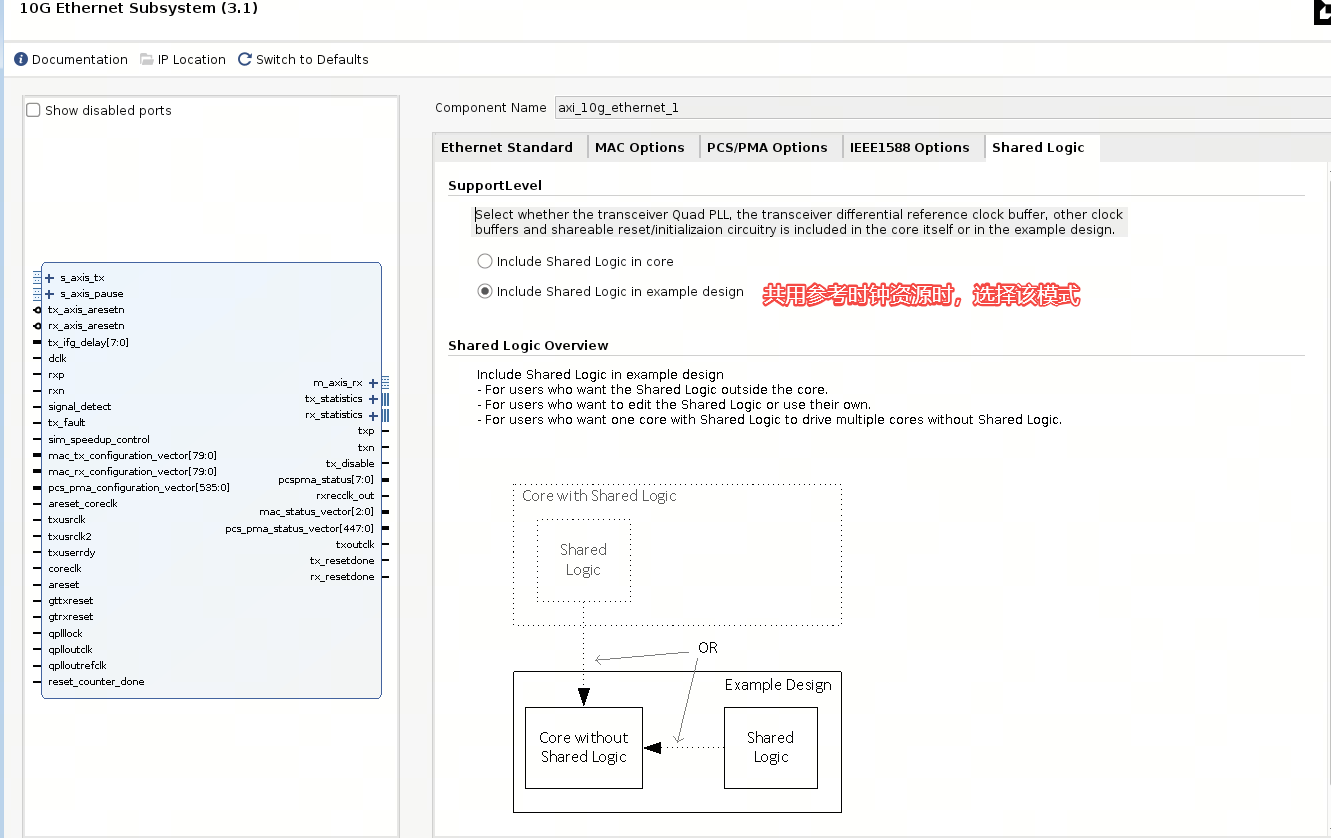

3.5 AXI-10G-ETHERNET

本设计采用4组10G MAC IP,配置如下:

741

741

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?