一、对DDR中Bank(逻辑Bank)、Rank(物理Bank)的整理

首先,在DDR的内部,数据是以阵列的形式存储的,通过指定的行和列就可以对目标数据进行读/写。

(1)Bank

DDR中的逻辑Bank就是指DDR中指存储阵列的个数,DDR中一般有多个存储阵列。由于制造工艺的原因,存储阵列的规模一般不会做的太大, 并且数据位宽一般是4/8/16。一个时钟周期内只允许DDR对一个逻辑BANK进行操作,而不是对内存芯片内所有逻辑BANK同时操作,因为芯片的位宽就是逻辑BANK的位宽。逻辑BANK的地址线是通用的,只要再有一个逻辑BANK编号加以区别就可以了。

(1)Rank

物理Bank(Rank) 是多个芯片组成的内存条上出现的概念,由于处理器的数据位宽一般是32/64bits,而单个芯片的位宽等于其内部单个存储阵列的位宽4/8/16,所以需要多个芯片组合起来才能提供CPU需要的数据。一个Rank里的芯片组合起来后刚好等于数据总线位宽,当内存条中所有芯片提供的位宽超过了数据总线的位宽,发生富余时才会出现多个Rank。CPU一个周期只能访问一个Rank。

二、 DDR型号的识别

以镁光1Gb ddr2为例:1Gb ddr2有三种型号:

MT47H256M4 – 32 Meg x 4 x 8 banks

MT47H128M8 – 16 Meg x 8 x 8 banks

MT47H64M16 – 8 Meg x 16 x 8 banks

例如:MT47H64M16 – 8 Meg x 16 x 8 banks

8Meg: ddr中的存储bank的深度为8M的存储大小,也就是8x1024x1024的大小

中间的16:代表每个bank的读写位宽为16bit

8banks:代表这个ddr的型号有8个bank

总上所属:该ddr2的型号含义为:有8个读写位宽为16bit,读写深度为8M的Bank,存储总容量计算为:8M x 16bit x 8 =1Gb。

三、 DDR三种频率

内存颗粒的核心频率是固定的,一些常见的内存颗粒核心频率如下。

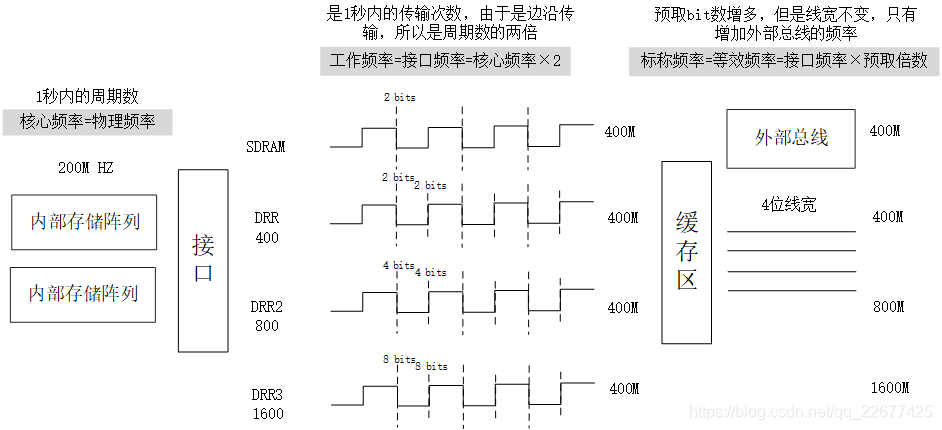

DDR、DDR2、DDR3他们相同之处就在于改进了SDRAM的在一个周期内只能在上升沿的时候进行数据传输的弊端,他们都可以在升和降两个阶段进行数据传输,所以工作频率扩大一倍。

但是他们不同的在于他们的预读取的能力不相同,DDR预读取2bit,DDR2预读取4bit,DDR3预读取8bit,所以在内存颗粒的核心频率相同的时候,DDR的等效频率是核心颗粒频率的2倍,DDR2是四倍,DDR3是八倍。

也就是说DDR系列的内存有两个地方提升了频率,第一、一个时间周期内进行两次数据传输提升了工作频率。第二、增加了预读取技术提升了等效频率,

三种频率的关系如上图所示,接口处DDR技术获得两倍的传输速率,随着预取技术的提高,多读取出的数据需要放到缓存区,由外部总线分多次取走

所以外部总线的频率=接口频率 ×(单周期内从端口发出的数据÷总线位宽)

四、 DDR带宽计算

内存带宽计算公式1:

带宽=内存核心频率×倍增系数×(内存总线位数/8)

内存带宽计算公式2:

带宽=标称频率×线宽÷8

五、参考博客

关于DDR存储容量的问题

内存条的逻辑BANK和RANK(物理BANK)概念

DDR工作时序与原理

如有不妥烦请指出

本文详细介绍了DDR内存中的Bank(逻辑Bank和物理Bank Rank)的概念,以及DDR型号的识别方法,包括DDR的不同频率类型和带宽计算。通过对DDR的工作原理和组织结构的解析,帮助读者深入理解DDR内存的运作机制。

本文详细介绍了DDR内存中的Bank(逻辑Bank和物理Bank Rank)的概念,以及DDR型号的识别方法,包括DDR的不同频率类型和带宽计算。通过对DDR的工作原理和组织结构的解析,帮助读者深入理解DDR内存的运作机制。

1万+

1万+