使用环境:虚拟机+Ubuntu16.04

软件版本:vivado 2019.1

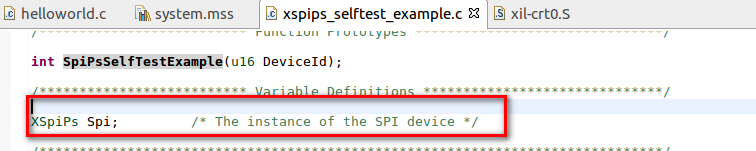

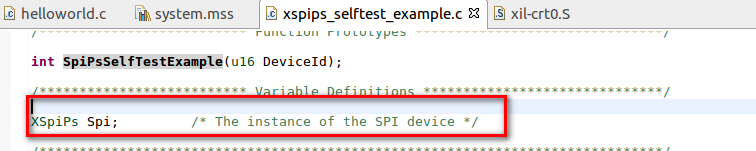

现象描述:ps端SPI例程测试,运行 SpiPsSelfTestExample例程,一开始运行成功打印,Successfully ran SPI Selftest Example;

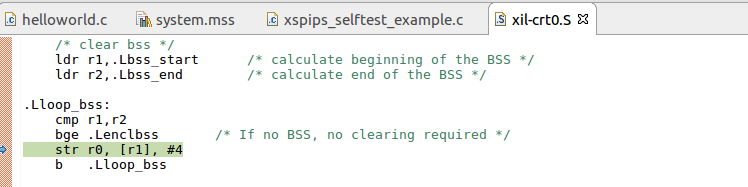

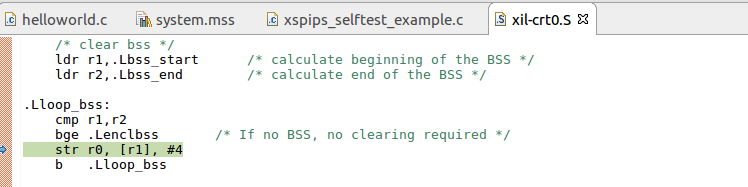

添加代码后再调试无法进入main,将代码还原到例程,调试仍然无法进入main,一直在初始化汇编中跳不出来!

现象消失:

将全局变量放到main里面,就能正常调试了。原因不明

使用环境:虚拟机+Ubuntu16.04

软件版本:vivado 2019.1

现象描述:ps端SPI例程测试,运行 SpiPsSelfTestExample例程,一开始运行成功打印,Successfully ran SPI Selftest Example;

添加代码后再调试无法进入main,将代码还原到例程,调试仍然无法进入main,一直在初始化汇编中跳不出来!

现象消失:

将全局变量放到main里面,就能正常调试了。原因不明

8400

8400

808

808