已完成:

EEPROM(IIC协议):长期保存,小容量

UART串口(RS-232、RS-485)

待学习:

DDR:高速,断电丢失

SD卡

FLASH缓存(SPI协议):大容量,快速访问,常用于程序存储

FT232H(USB to FIFO/JTAG/SPI/IIC)

SPI

端口:

NSS(Nagetive Slave Select) :从机选择引脚,可配置为硬件/软件

MISO(Master Input Slave Output):主机输入端口/从机输出端口

MOSI(Master Output Slave Input):主机输出端口/从机输出端口

SCK(Serial Clock):串口时钟

SPI的工作原理:在主机和从机都有一个串行移位寄存器,主机通过向它的SPI串行寄存器写入一个字节来发起一次传输。串行移位寄存器通过MOSI信号线将字节传送给从机,从机也将自己的串行移位寄存器中的内容通过MISO信号线返回给主机。

这样,两个移位寄存器中的内容就被交换。外设的写操作和读操作是同步完成的。如果只是进行写操作,主机只需忽略接收到的字节。反之,若主机要读取从机的一个字节,就必须发送一个空字节引发从机传输。

SPI的传输方式:SPI总线具有三种传输方式:全双工、单工以及半双工传输方式。

全双工通信,就是在任何时刻,主机与从机之间都可以同时进行数据的发送和接收。

单工通信,就是在同一时刻,只有一个传输的方向,发送或者是接收。

半双工通信,就是在同一时刻,只能为一个方向传输数据。

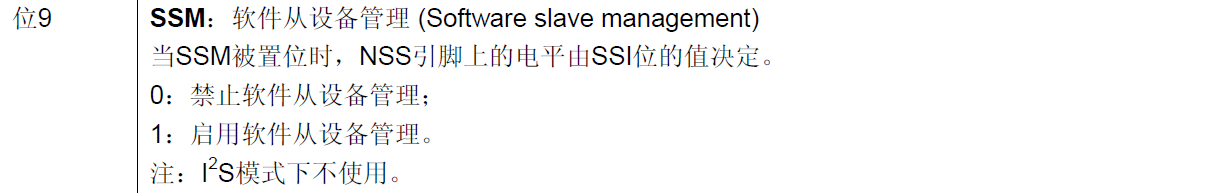

STM32中的SPI_CR1寄存器的SSM位和SSI位用于控制NSS引脚工作模式:

![]()

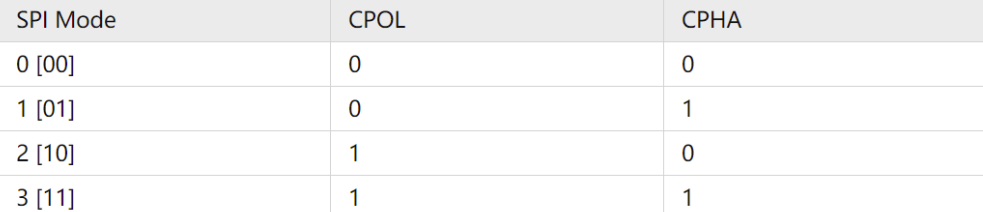

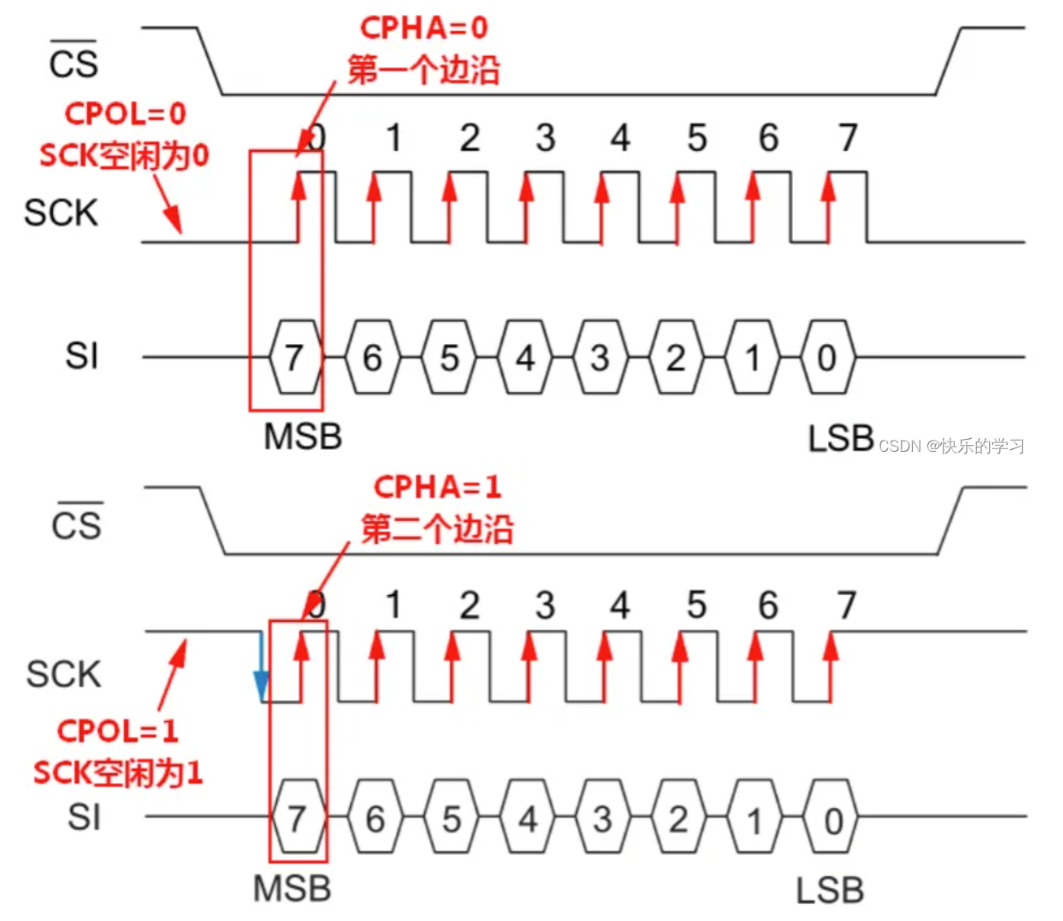

SPI模式设置:

CKP/CPOL(Clock Polarity):时钟极性,空闲时时钟线电平(高/低)

CKE/CPHA(Clock Phase):时钟相位 (Edge),在时钟变化的第几个沿进行信号采集(即上升沿、下降沿)

SPI连接方式:

多从机模式(多个NSS接口,每个从机连接一个NSS接口)

菊花链模式(Daisy Chain,每个从机MISO口连接下一个从机MOSI接口,直至最后一个从机MISO接口连接回主机)

数据发送方式:

一般为高位优先(MSB),有的也可以设置为低位优先(LSB)

//stm32 HAL库示例 g_spi2_handler.Init.FirstBit = SPI_FIRSTBIT_MSB; g_spi2_handler.Init.FirstBit = SPI_FIRSTBIT_LSB;

UART串口

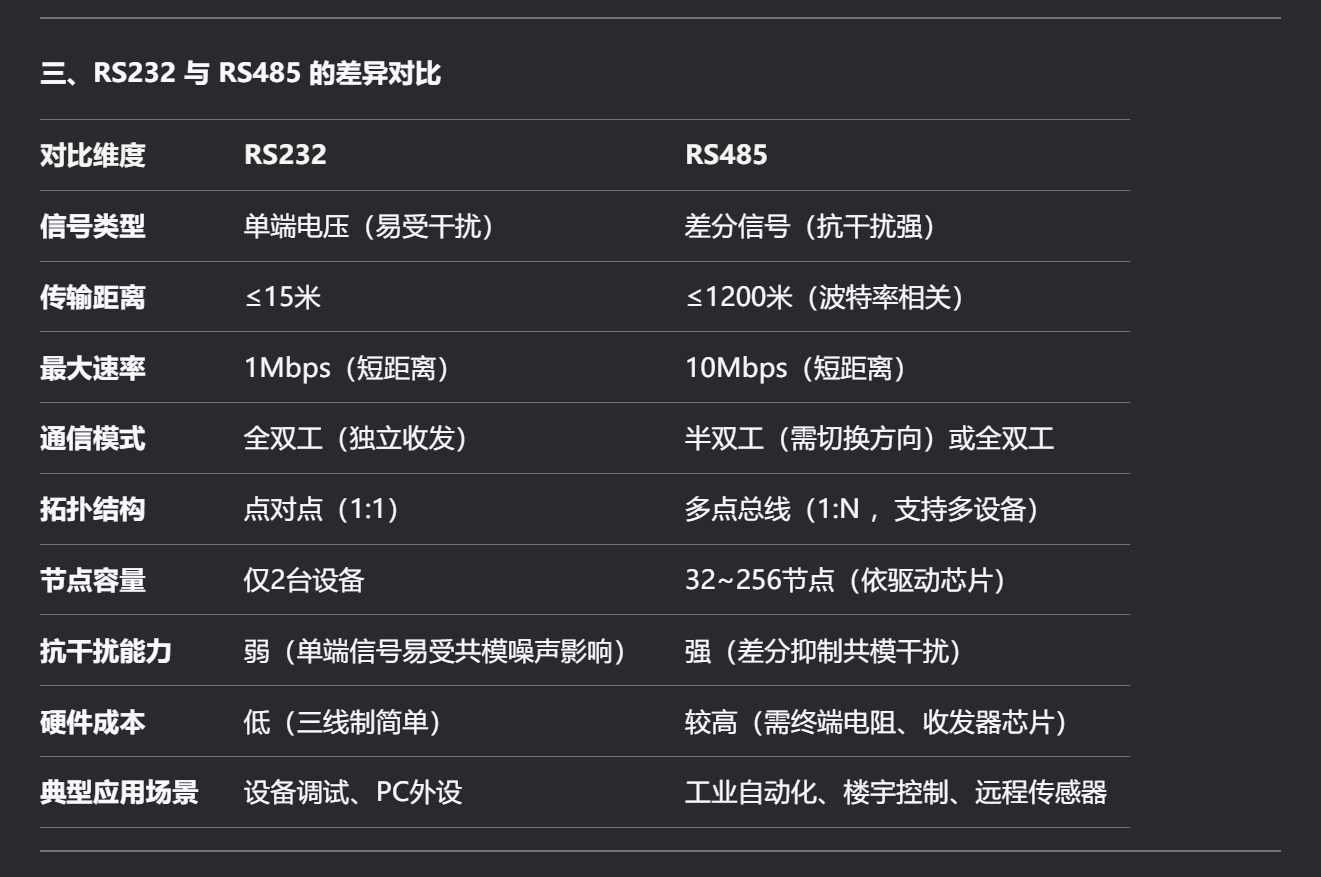

物理层电平标准(RS232/RS485)

除去UART最常使用的TTL电平外(逻辑“1”为高电平(通常为 3.3V 或 5V),逻辑“0”为低电平(0V)),还可转换为以下标准进行传输:

RS232 为全双工,单端传输,容易产生共模干扰,通信距离短(15m),只允许一对一通信

逻辑“1”为-3V至-15V,逻辑“0”为+3V至+15V

RS232 转换芯片:如 MAX232、SP3232

RS485 为半双工,差分传输,抗噪声干扰性好,通信距离长(最高3km),允许连接多个收发器

差分信号传输,逻辑由A/B线电压差决定(±200mV阈值),A>B

RS485 转换芯片:如 MAX485、SN65HVD72

单端传输是指在发送或接收过程中,用信号线对地线的电压值来表示逻辑“0”和“1”。

差分传输使用两根信号线来传输一路信号,这两根信号线上传输的信号幅值相等,极性相反,用它们的差值来表示逻辑“0”和“1”

UART串口(TTL电平,可通过芯片转换为RS232/RS485)

UART需要两根信号线来实现,一根用于串口发送(TX, transmit),另外一根负责串口接收(RX, receive)(对于器件自己来说)。

如下图所示,需要交叉连接。此外由于使用单端传输,还需要一根地线。

奇偶校验:

接收UART 读取数据帧后,将计数值为1 的位,检查总数是偶数还是奇数。

如果奇偶校验位为0(偶数奇偶校验),则数据帧中的1 (逻辑高位)总计应为偶数。

如果奇偶校验位为1(奇数奇偶校验),则数据帧中的1 (逻辑高位)总计应为奇数。

当奇偶校验位与数据匹配时,UART 认为传输未出错。

数据发送从低到高依次发送。

波特率即每秒传输的位数(bit),常见的有有9600,19200,115200等。常用符号“Baud”表示,其单位为“波特每秒”(Bps)

使用verilog实现时序图:

接收模块:(时钟域同步>起始信号>起始位>数据为0>...>数据位7>停止位(1))

每次接收数据在一个数据周期的中间,这时信号最稳定

发送模块:(起始信号>起始位(0)>数据为0>...>数据位7>停止位(1))

IIC

IIC协议:Inter-Integrated Circuit(集成电路总线)

由Philips 半导体公司(现在的NXP 半导体公司)设计

由数据线SDA 和时钟线SCL 构成通

被控器件均并联在总线上,通过器件地址(SLAVE ADDR,具体可查器件手册)识别。

IIC 器件一般采用开漏结构与总线相连,I2C_SCL 和I2C_SDA 均需接上拉电阻

当总线空闲时,这两条线路都处于高电平状态;连到总线上的任一器件输出低电平,都将使总线拉低

I2C 总线支持多主和主从两种工作方式

起止时序:当SCL为高电平时拉低SDA表示开始或结束传输

整体时序图:

当SDA被拉低之后,SCL会以一定频率在0,1之间切换,即时钟

串行时钟线SCL 为低电平状态时,SDA 允许改变传输的数据位(1 为高电平,0 为低电平)

在SCL 为高电平状态时,SDA 要求保持稳定,相当于一个时钟周期传输1bit 数据

经过8 个时钟周期后,传输了8bit 数据,即一个字节(Byte)

第八个时钟末,主机释放SDA,等待从机应答

如果在第9个周期内拉低则应答成功,否则视为发送失败

第九个周期末,从机释放总线,继续等待主机拉低

从机地址发送:

每个I2C 器件都有一个器件地址,有些I2C 器件的器件地址是固定的,而有些I2C 器件的器件地址由一个固定部分和一个可编程的部分构成

进行数据传输时,主机首先向总线上发出开始信号,对应开始位S

然后按照从高到低的位序发送器件地址,一般为7bit

第8bit 位为读写控制位R/W,该位为0 时表示主机对从机进行写操作,当该位为1 时表示主机对从机进行读操作,然后接收从机响应

数据地址发送:

发送完第一个字节(7 位器件地址和一位读写控制位)并收到从机正确的应答后,就开始发送字地址(Word Address),根据容量,可能需要一个或两个字节

数据收发

读写控制位R/W为0:主机读取(read)本地数据,发送给从机并写入

单次写:

连续写:

只有部分I2C 设备支持页写操作

不能发送超过一页的单元容量的数据(如AT24C64 的一页的单元容量为32Byte)

读写控制位R/W为1:向主机写入(write)数据,从机读取数据并发送

读数据有三种方式:当前地址读、随机读和连续读

当前地址读:指在一次读或写操作后发起读操作

随机读:先进行一次虚写(Dummy Write)操作写入地址,再重新发送起始信号进行当前地址读操作

连续读:(当前地址连续读&随机地址连续读)从机发送数据后主机进行应答(拉低SDA),告诉从机继续发送数据

当前地址连续读:

随机地址连续读:

2130

2130

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?