SETP6:检查一下UART_CLOCK.SCHDOC这个文件。

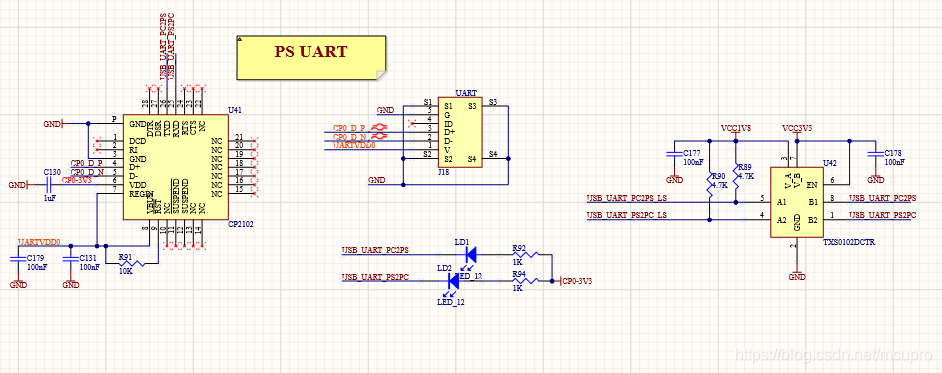

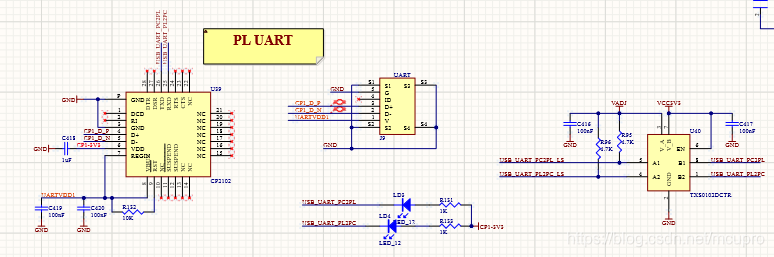

内有两路USB转串口芯片,无论原件还是是封装都是现成的,因此这部分比较有把握。

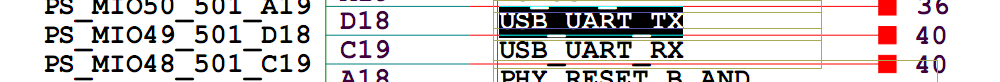

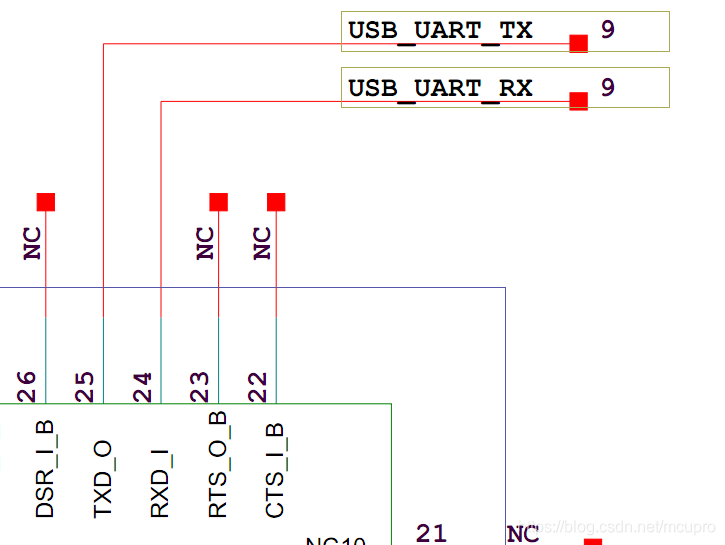

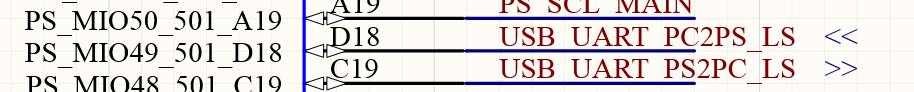

PS_UART部分接的PS的MIO必须严格对应,

我们用PS2PC来表示从PS为输出,PC也就电脑,是输入,则看到MIO48是PS2PC,同理可以MIO49是PC2PS。

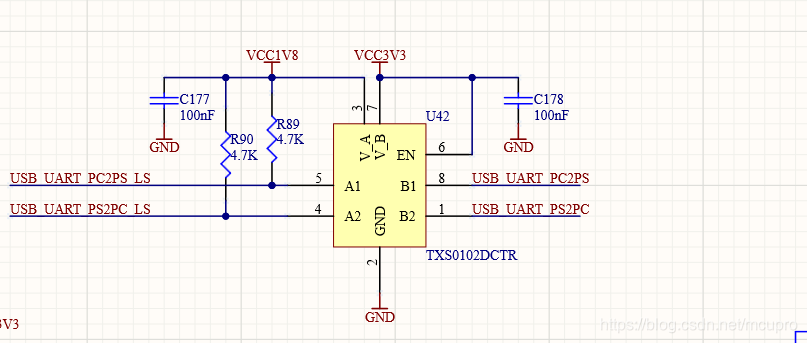

经过确认没有问题。其实这里发现ZC706官方板子用的是CP2103这芯片,而咱们新的板子用的是CP2102,差别就在CP2103的IO可以通过VIO这个脚设置。我们用CP2102不得不加上一个电压转换芯片:

再次做新产品时候可以考虑使用上CP2103这个芯片。

检查PL UART 也没有问题。

LED接用CP2102输出的3.3V来驱动是经过验证无误的。

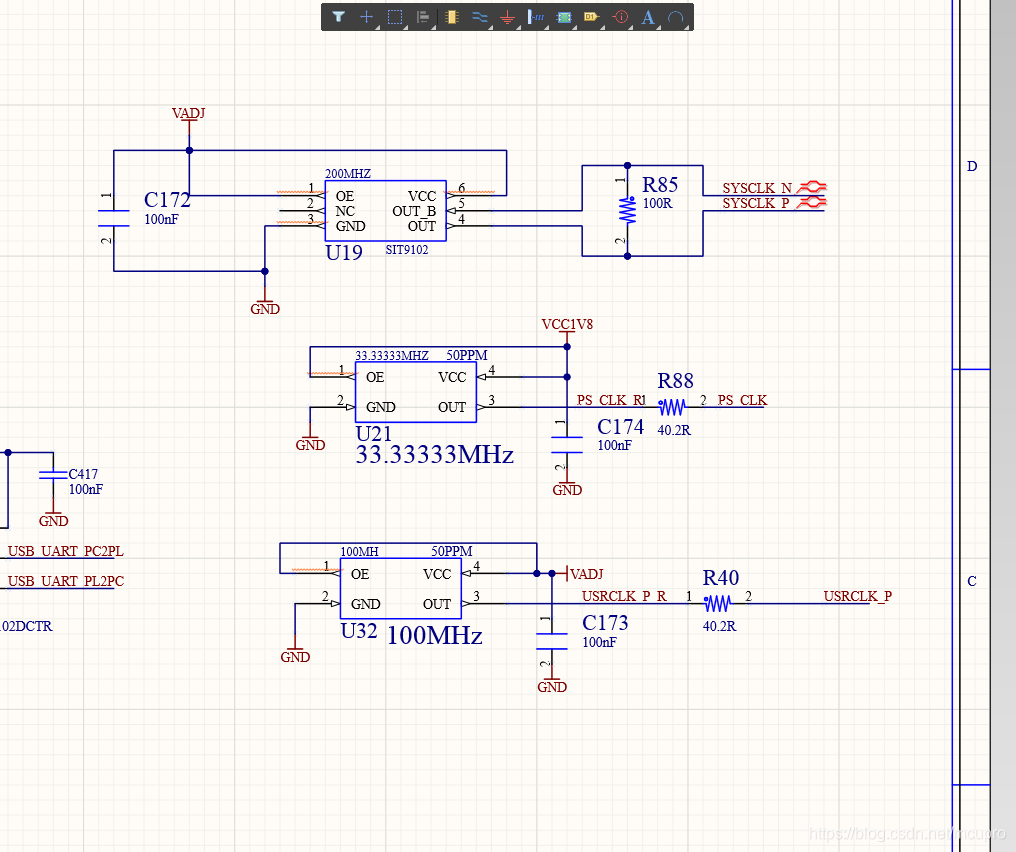

接下来看时钟部分:

其中33.333MHZ和100MHZ单端时钟用的是3528封装,并且供电电压是1.8V,实际上绝大多有源晶振是支持1.8V电压的。200M的差分有源晶振是5032封装的。

这里要确保一下晶振的PCB封装。

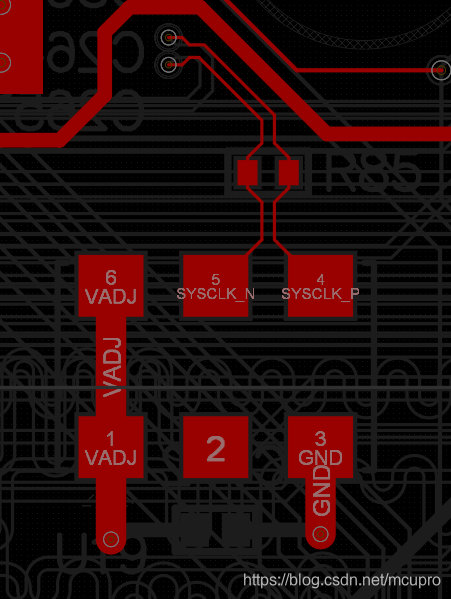

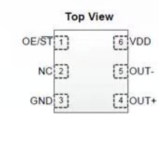

以上小的图是从ZEDBOARD的PCB里面拷贝的封装,下面就使我们板子的封装。可见引脚定义是一样的。其中4脚可以悬空或者接电源。

接下来看5032封装的有源差分晶振

从晶振的介绍网页里面确确认了一下封装定义无误。采购时候注意详细型号是SIT9102-231N-18E-200.00MHZ

之后查看时钟信号是否接在FPGA对应的引脚上。

此篇原理图检查完毕。

本文详细检查了ZC706开发板的UART接口配置,包括USB转串口芯片的选择(CP2102与CP2103),以及MIO引脚的正确连接。同时,深入探讨了时钟部分的设计,特别是33.333MHz、100MHz和200MHz晶振的使用及其PCB封装,确保信号正确连接到FPGA引脚。

本文详细检查了ZC706开发板的UART接口配置,包括USB转串口芯片的选择(CP2102与CP2103),以及MIO引脚的正确连接。同时,深入探讨了时钟部分的设计,特别是33.333MHz、100MHz和200MHz晶振的使用及其PCB封装,确保信号正确连接到FPGA引脚。

2598

2598

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?