SODIMM 简介

SODIMM 接口DDR3适配额外的内存条才能满足数据缓存的需求,这种需求一般用于高端项目,DDR3 SDRAM 常简称 DDR3, 是当今较为常见的一种储存器, 在计算机及嵌入式产品中得到广泛应用,特别是应用在涉及到大量数据交互的场合。

MIG配置流程

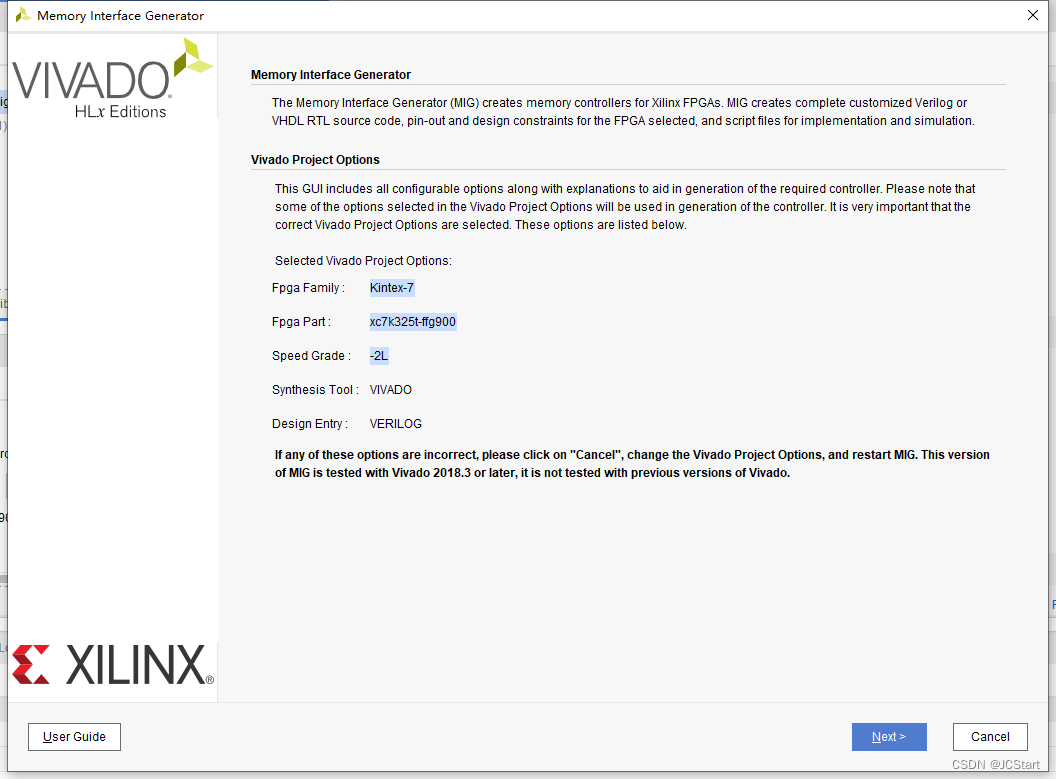

本文以XC7K325T-FFG900-2L为例,记录MIG的配置过程,进入IP配置界面后,第一个界面是 Memory Interface Generator 介绍页面, 如下图所示。默认的器件家族(FPGA Family)、器件 型号(FPGA Part)、速度等级(Speed Grade)、综合

工具(Synthesis Tool)和设计输入语言(Design Entry)都和创建工程是保持一致。

注意点

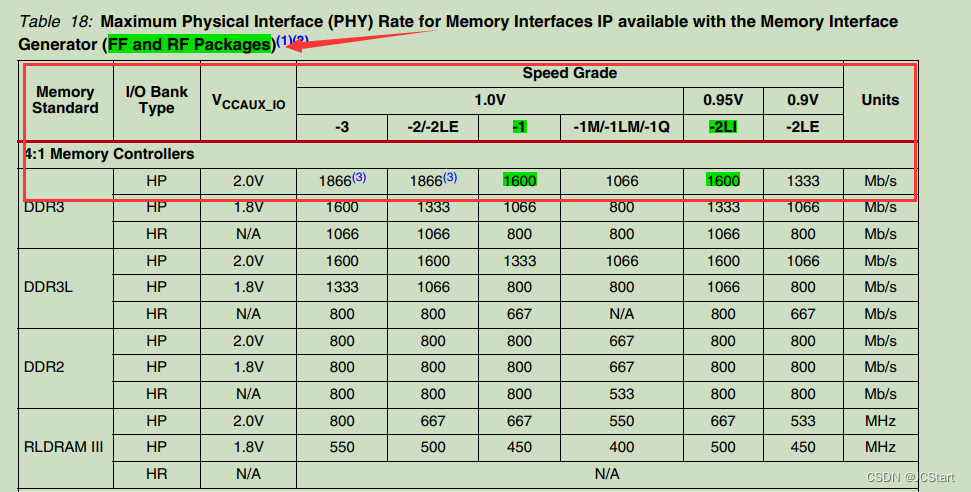

这里的速度等级和封装都要选准确,速度等级将会影响后续的可配置的最大速率,参考DS182

点击 Next 到 MIG Output Options 配置页面中, 如下图所示。 勾选“Create Design”,默认名称(Component Name)为“mig_7series_0”,用户可对其进行修改,这里保持默认。选择控制器数量(Number of Controllers)为 1,本次 MIG IP 的用户接口使用 AXI 协议接口,勾选 AXI4 Interface。

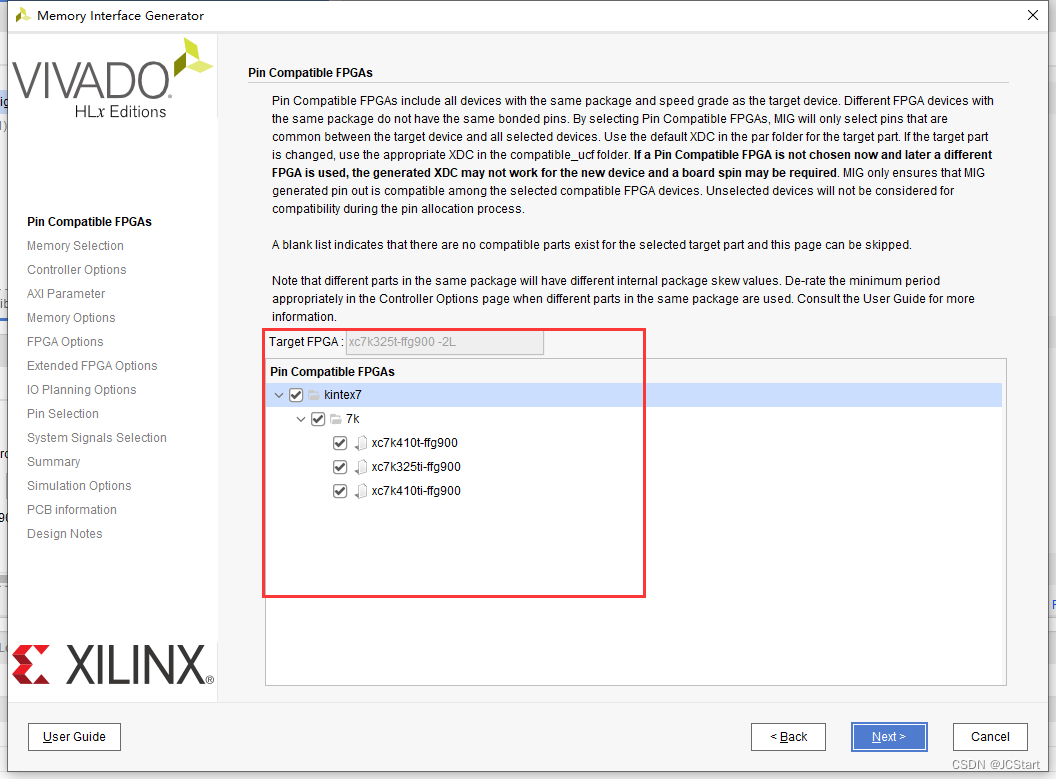

点击 Next 到 Pin Compatible FPGAs 配置页面,如下图所示该界面可用于配置选择和当前所设定的唯一器件型号做引脚兼容的其它 FPGA 型号。本次办卡设计需同时兼任XC7K410对此而言,这个功能是很实用的。

点击 Next 进入到如下图所示的 Memory Selection 配置页面,这里选择“DDR3 SDRAM” 即可。

文章阐述了SODIMMDDR3在项目中的应用和MIG配置步骤,涉及速度等级、接口选择、时钟周期调整等内容,旨在帮助读者理解高级内存配置技巧。

文章阐述了SODIMMDDR3在项目中的应用和MIG配置步骤,涉及速度等级、接口选择、时钟周期调整等内容,旨在帮助读者理解高级内存配置技巧。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

732

732

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?