一种面向物联网设备的新型电路设计框架:结合电荷回收的无线能量收集

摘要

有限的能量是物联网设备面临的一个重大挑战,因为频繁更换电池并不可行。此前已提出多种能量收集技术以缓解这一挑战。本文开发了一种新的电路设计技术,可显著提高现有无线能量收集方法的功率效率。与传统方法不同,该方法无需整流和稳压模块,而是利用电荷回收电路理论直接将收集到的信号用于为物联网设备供电。所提出的方法除了具有更高的能量效率外,还减小了外形尺寸,从而降低了物联网设备的成本。该方法采用45纳米CMOS技术进行评估,与传统方法相比,功耗降低了约五倍。

一、引言

物联网(IoT)正作为一种新型计算范式兴起,将全球网络空间与日常物理世界连接起来。该范式适用于交通、医疗保健、智能环境和社会关系等多个领域[1]。推动物联网发展的关键因素是先进的识别、感知、逻辑计算和无线通信设备的发展与集成。

现有的物联网设备由于电池寿命有限而面临挑战,因为定期更换数十亿个设备的电池并不现实。即使是无源RFID标签,也因全波整流器和电压稳压器电路[2]导致更高的能量损耗和更大的面积。因此,外形尺寸和能效是未来物联网设备的主要问题。

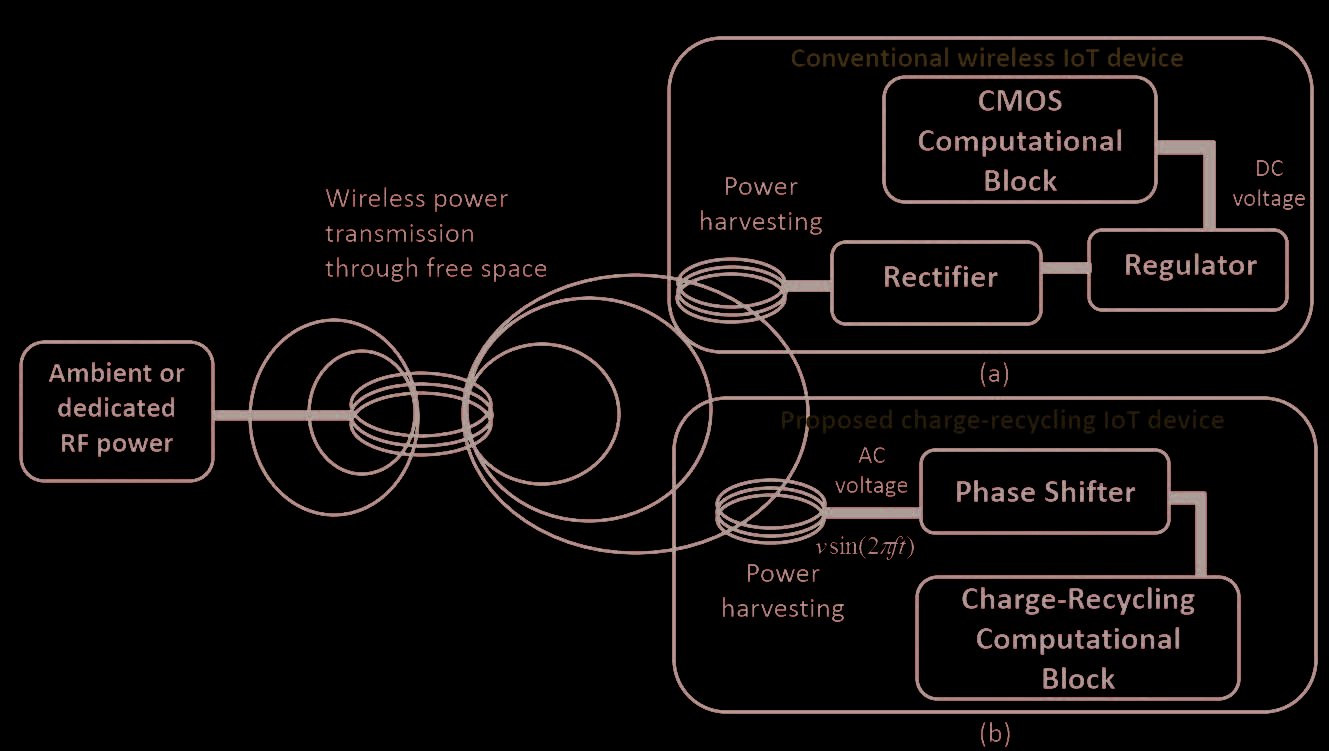

受这些基本问题的灵感启发,本文提出了一种新型的无线供电电路,如图1所示。在此框架中,利用现有的电荷回收理论,直接使用从无线能源获取的交流信号为设备内的计算模块供电。因此,消除了传统方法中的整流和稳压步骤,提高了能量效率并降低了外形尺寸。

本文的其余部分组织如下。第二节总结了物联网设备的现有无线能量收集方法。第三节描述了提出的方法。第四节展示了仿真结果,以证明提出的方法的功能性和能量效率。最后,第五节对全文进行了总结。

II. 背景

已提出多种能量收集方法(如光伏、静电或压电、热电以及射频或感应式换能器),以减轻物联网设备对电池的强烈依赖[3]。前三种换能器高度依赖相应能源的存在。

相比之下,考虑到各种无线电信号的广泛存在,射频无线能量收集通常能够提供更稳定的能源。传统的射频能量收集器通过天线(或耦合线圈)接收传播的电磁波,并将交流电能转换为稳定的直流电压,以驱动物联网设备[4]。

该过程通常包括全波整流器、倍压器和稳压器。当收集到的射频信号被转换为直流供电电压时,由于整流过程的功率效率较低,会造成显著的能量损失。在稳压步骤中还会进一步损失额外的功率[5]。即使采用最先进的射频‐直流转换器,在此阶段至少也会损失30%的功率[4]。

III. 提出的方法

在提出的方法中,通过利用现有的电荷回收电路理论,将采集的交流信号(以正弦波形式)直接用于计算。在电荷回收电路中,功耗显著降低的原因在于:1)通过电压差较小的晶体管引导电流;2)逐步回收存储在寄生电容中的部分能量[6]。该方法早在20世纪90年代中期就被提出,作为静态CMOS操作的一种替代计算方法[7]。其适用性

然而,由于从直流电源电压生成所需交流(或梯形)信号的效率低下,牺牲了大部分功率节省,因此这一方法一直受到严重限制[8]。

或者,在所提出的应用中,能量以交流信号的形式被无线收集,从而消除了这一众所周知的限制。因此,无线供电的物联网设备为电荷回收电路提供了一个独特的应用领域,本文对此进行了论证。

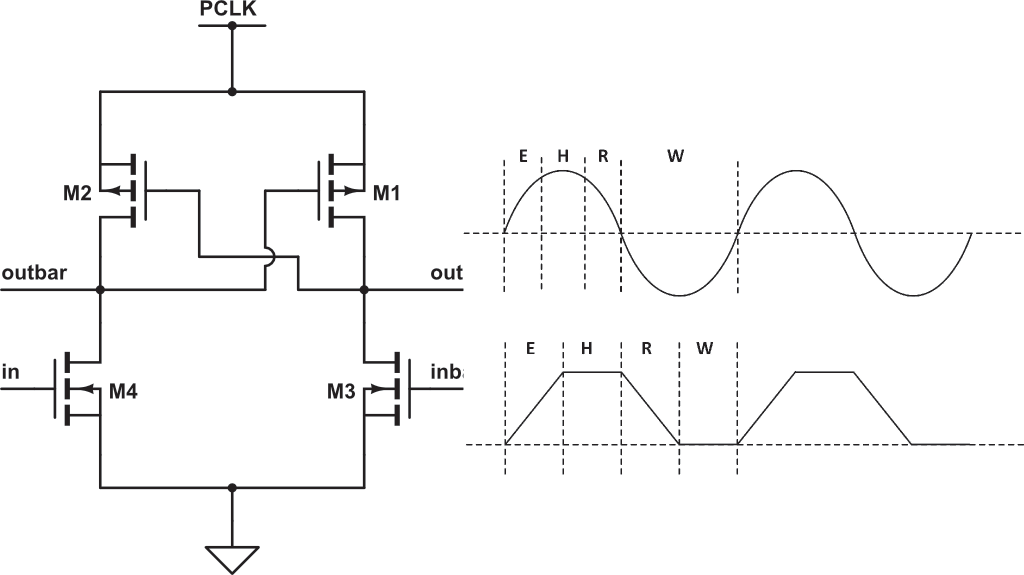

高效电荷回收逻辑(ECRL)被选为逻辑家族,其由四相交流信号(称为功率时钟信号)供电,如图2[7]所示。

功率时钟信号通常为梯形波形,包含四个相位:评估(E)、保持(H)、回收(R)和等待(W)。如图2所示,一个ECRL逆变器包含两个交叉耦合的PMOS晶体管,用于预充电/评估和回收相位,以及两个NMOS晶体管用于实现功能。当PCLK信号达到M1的阈值电压时,outbar开始跟随PCLK信号,假设输入信号in处于高电平(因此outbar处于低电平)。在保持相位期间,输出电压保持稳定,以便下一级能够正确进行评估。在回收相位期间,PCLK逐渐下降,将负载电容上存储的电荷进行回收。为了对称性,插入一个等待相位以完成四相PCLK操作。相邻门的PCLK信号之间存在90◦相位差,需要四个PCLK信号。因此,ECRL逻辑本质上是流水线化的。

在提出的方法中,由于交流信号是通过无线方式获取的,因此得到的是正弦PCLK信号,而非传统的梯形波形。

提出的方法的三个组成部分(无线链路、移相器和电荷回收计算模块)将在以下小节中进行描述。

A. 无线链路

基于射频识别标签和某些生物医学植入设备中使用的无线能量收集技术,目标物联网设备通过电感耦合[9]获得供电电压。如图1所示,初级线圈由射频功率放大器驱动,以发射专用的无线电波。目标无线设备通过次级线圈(电感耦合)收集电磁能量。

次级线圈提取的能量百分比可以从耦合系数k进行评估,该系数在空气中可经验表示为[10],

$$

k = \frac{r_1^2 r_2^2}{\sqrt{r_1 r_2 (\sqrt{x^2 + r_2^2})^3}}

$$

其中r1和r2分别为初级和次级线圈的半径,x表示两个线圈之间的距离。该弱耦合拓扑可以用RLC电路和一个理想变压器精确建模,如图3所示。在此电路模型中,理想变压器的L1和L2代表两个独立的线圈,Rp表示前端采集电路中的寄生电阻损耗,Ct则是用于提升线圈电压水平的调谐电容。变压器内部的比率N由[10]给出。

$$

N = k \sqrt{\frac{L_2}{L_1}}

$$

所提出方法的无线链路参数列于表I中。这两个电感器实现在电路板上。注意,次级耦合电路中的两个电感器配置成使得两个采集的射频信号具有180◦相位差,从而为ECRL逻辑提供所需的第一个和第三个PCLK信号。剩余两个相位由下一部分所述的相位偏移电路获得。

表I 无线链路规格

| 参数 | L1 | L2 | Rp | Ct | N |

|---|---|---|---|---|---|

| 228.4nH | 3.656μH | 1Ω | 330pF | 3 |

B. 移相电路

移相器通过由特定频率的电磁波驱动的传输线产生固定相位角。开关低通和高通拓扑常用于单片微波集成电路中,以实现180◦相位偏移[11]的平坦带。受此拓扑结构启发,从开关线移相器中提取低通支路以生成四相PCLK信号。所提出的相位偏移电路可建模为π‐LC低通网络,如图4所示。对于θ相位偏移,模型中的电感(L)和电容(C)的值由以下方式确定

$$

L = \frac{Z_0 \sin\theta}{\omega} \quad \text{and} \quad C = \frac{1 - \cos\theta}{\omega Z_0 \sin\theta}

$$

其中Z0是并联阻抗,用于缓解变化的负载阻抗的影响。

所提出的移相器的设计参数列于表II中。电阻器和电感器均实现在电路板上。如前所述

表II 移相器规格

| 参数 | L | C | Z0 |

|---|---|---|---|

| 796μH | 100fF | 100kΩ |

上一节中,0◦和180◦ PCLK信号来自次级耦合电路。因此,当这两个信号通过所提出的90◦相位移器时,生成第三和第四PCLK信号,以完成ECRL计算模块的完整操作,如下一节所述。

C. 电荷回收4位进位Ripple加法器

选择了一个4位加法器来演示计算模块的功能,该模块使用无线收集的交流信号工作。考虑到ECRL逻辑固有的流水线特性,输出信号应仔细同步。具体而言,从输入到输出的每个输出路径上的ECRL门电路总数应相同。这种行为要求在某些输出路径上插入ECRL缓冲器。

一个由四个级联的1位全加器组成的4位进位Ripple加法器需要4个周期(假设每个1位全加器需要1个周期)来完成一次加法操作,前提是采用基于标准单元的加法器设计。相反,如图5所示,进位Ripple加法器利用了propagate和generate信号。此外,与门和或门被合并

电压 参考

整流器 稳压器

Vin

Vout

0.0 1.0x10-6 2.0x10-6 3.0x10-6 4.0x10-6

0.00 0.33 0.66 0.99 0.00 0.33 0.66 0.99 -3.0 -1.5 0.0 1.5 3.0

Vreg (V)

时间(秒)

Vrec (V)

无线链路输出

稳压器输出

Vwl(V)

整流器输出

将其整合为一个复杂的ECRL门,称为ECRL组PG单元[7]。

最后,由于固有的流水线结构,插入缓冲器以同步每个输出。实现了1.25个周期的逻辑深度。该4位ECRL进位ripple加法器可用作构建高位ECRL加法器的基本模块。

IV. 仿真结果

为了研究和量化所提出方法的优势,采用45纳米技术设计了传统方法和提出的方法。传统方法对采集的交流信号进行整流和稳压,而提出的方法则基于相同的无线链路,如第三节-A所述,其传输频率为13.56兆赫。需要注意的是,这是基于硅的物品级射频识别的标准频率[12]。

对于常规方法,设计了一种高效且低复杂度的整流器和稳压器,如图6所示。整流和稳压的功能在图7中进行了说明,其中显示了无线链路、整流器和稳压器的输出信号。输出电压被调节至约1伏特。该电压为工作在13.56兆赫的常规4位进位Ripple加法器供电。所有主输入和主输出都被锁存到触发器中。

或者,对于提出的方法,第三节-B中描述的移相器被设计用于生成四个具有90◦相位差的PCLK信号,如图8所示。这些正弦PCLK信号用于驱动ECRL加法器,

在第三节-C中进行了描述。注意,图8所示PCLK波形的峰值幅度并不完全相同,存在约100 mV的变化。这种变化是由于每个PCLK信号所见的负载阻抗略有不同所致。然而,该差异不会影响ECRL加法器的正常工作,因为峰值电压高于阈值电压。当提供循环输入数据模式 Cin= 11110000, Ai= 01010101, Bi= 11001100(其中 i= 1, 2,3, 4)时,由无线收集的交流信号驱动的ECRL加法器的输出信号如图9所示。从输出信号可以看出,ECRL加法器能够准确且可靠地利用采集的交流信号工作,其中逻辑高电平足够可区分。

为了比较能耗,对传统设计(无线链路、整流器、稳压器和在13.56兆赫下运行的基于静态CMOS的4位加法器)和提出的方法(无线链路、移相器以及在四个采集的交流信号下运行的基于ECRL的4位加法器,每个信号频率为13.56兆赫)均进行了4 μs的仿真,并分析了消耗的能量,如表III所列。根据该表,提出的方法所消耗的总能量是传统设计的五分之一。

表III 所提出方法与传统方法的能量损耗比较

| 模块 | 能量损耗 (fJ) | 模块 | 能量损耗 (fJ) |

|---|---|---|---|

| 4位加法器 | 5958 | 4位加法器 | 500 |

| 整流器和稳压器 | 70502 | 移相器 | 11490 |

| 总计 | 76460 | 总计 | 16490 |

即使两个系统都在相同的13.56兆赫频率下运行,其能耗也低于传统方法。此外,随着计算模块的增大,能耗的降低预计将进一步增加,因为电荷回收加法器的能耗比静态CMOS加法器大约低十一倍。因此,随着逻辑规模的增大,移相器带来的开销会进一步减少。

五、结论

针对物联网设备,提出了一种新的电路设计框架。该方法通过将现有的电荷回收理论应用于无线能量收集,使其重新焕发活力。尽管电荷回收电路在传统系统中存在众所周知的局限性,但在所提出的应用中,由于无线收集的信号本身即为交流信号,电荷回收可实现显著的功率节约。

已针对无线链路、移相器、整流器和稳压器建立了相应的电气模型和电路。提出了一种综合分析方法以实现公平比较。基于45纳米技术的仿真结果表明,该提出的方法可将总能量降低约五倍。

749

749

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?