一. 概述

将RTL源代码转换成门级网表,将HDL语言描述的电路转换为工艺库器件构成的网络表的过程。在综合过程中,优化进程尝试完成库单元的组合,是组合成的电路能最好的满足设计的功能、时序和面积的要求。

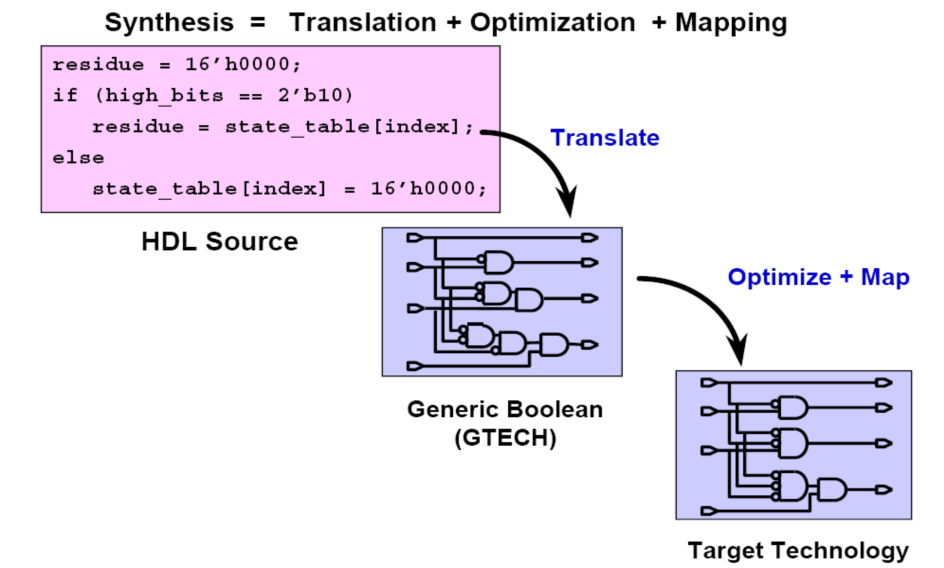

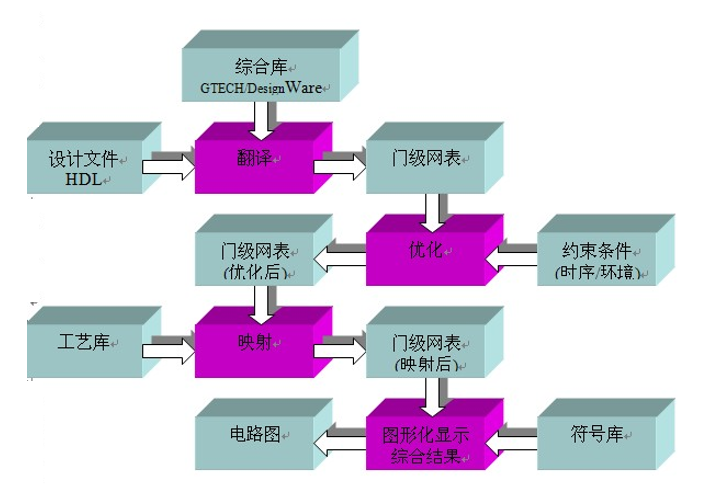

电路的逻辑综合一般由三个步骤组成,即 综合=转化+逻辑优化+映射。

(Synthesis=Translation+Logic Optimization+Mapping)

转化:首先将 RTL 源代码转化为通用的布尔等式。

逻辑优化:利用设计的约束对电路进行逻辑综合和优化,使电路能满足设计的目标或者约束。

映射:使用目标工艺库的逻辑单元映射成门级网表。

在综合过程中,优化进程尝试完成库单元的组合,使组合成的电路能最好地满足设计的功能、时序和面积的要求 综合是约束驱动(constraint driven)的,给定的约束是综合的目标。

约束一般是在对整个系统进行时序分析得到的,综合工具会对电路进行优化以满足约束的要求。综合以时序路径为基础进行优化。

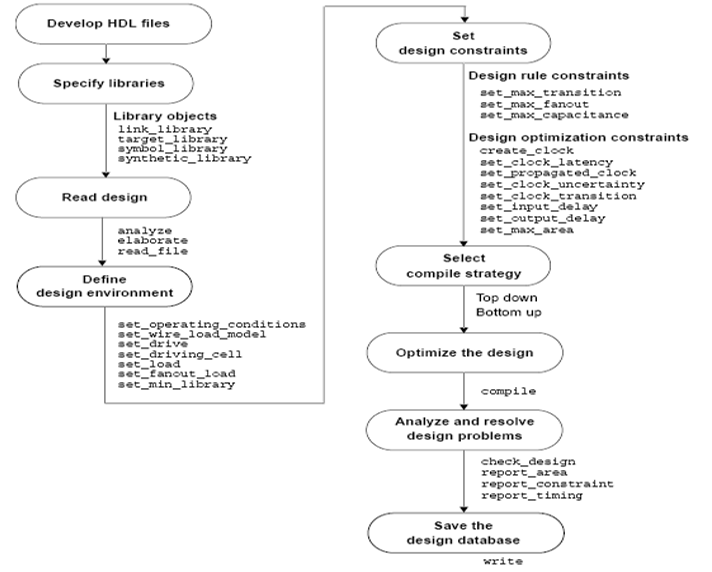

综合的基本流程:

1.准备RTL代码:RTL代码经过前端仿真后才能用于综合。

2.定义库:设定好所需要用到的综合库等多种库。

3.读入设计:综合工具读入RTL代码并进行分析。

4.定义设计环境:设定设计的工作环境、端口的驱动和负载,线负载模型等。

5.设置设计约束:这是综合的一个极其重要的环节,设定好正确的约束才能得到正确的综合结果。约束要适当,不能过紧或过松。主要是定义时钟和I/O的约束。

6.设置综合策略:有top-down和bottom-up两种策略,各有所长,对于不同的设计要具体分析。

7.优化设计:综合工具可以根据约束对电路进行优化,也可以人为地加入命令,改变优化方法。

8.分析和解决设计的问题:在设计综合(compile)后,根据报告来分析设计中出现的问题,进而修订所出现的问题。

9.保存设计数据:综合完成后,保存各种数据,以供后续的布局布线使用(需先通过验证)。

综合流程图:

二. 工具概述

2.1 工具环境

Design Compiler有两种界面供用户使用,一种是命令界面,一种是图形界面。在Linux命令行下分别执行以下命令可以分别进入上述两种界面:

Linux% dc_shell-t (命令界面)

Linux% design_vision (图形界面)

DC启动时会先启动.synopsys_dc.setup文件,它里面设定了综合所需要的工艺库的信息以及一些对于工具的设定命令。 启动时,DC会以下述顺序搜索并装载相应目录下的启动文件:

1)、DC的安装目录;

2)、用户的home目录;

3)、当前启动目录。

注意:后装载的启动文件中的设置将覆盖先装载的启动文件中的相同设置。

2.2 .synopsys_dc.setup文件

.synopsys_dc.setup文件主要包括各种库的设定,变量的设定等。下面具体介绍各种库的意义及如何设定。(实例)

搜寻路径(search_path):指定各种库的路径,可以将所用的库的路径放入search_path中,在设定target_library和link_library时就不必加上库的绝对路径,DC会自动在search_path中寻找所用到的库的路径从而读入该库。

目标库(target_library):是DC在做编译(compile)的时候来构成电路图的,将电路映射到具体的单元上。例如 set target_library my_tech.db

链接库(link_library):是将设计连接到对应的库上,一般包含目标库、宏单元、IP核等。例如: set link_library “* my_tech.db”。其中“*”指明当链接设计时,DC先搜寻内存中已有的库,然后再搜寻变量link_library中制定的其它库。

符号库(symbol_library) :定义了单元显示的图形库,当用design_vision来查看图形的时候使用。

综合库(synthetic_library):是由Synopsys公司提供的DesignWare库即为 Designware library ,名字上翻译是综合库,但却常称之为IP库,而不是直译。特殊的 Designware library 是需要授权的(比如使用多级流水线的乘法器),默认的标准 Designware 由 DC 软件商提供,无需指定。包含了许多IP核及运算单元,用于实现verilog描述的运算符,为电路的优化起着重要的作用。

2.3 系统层次的划分与基本概念

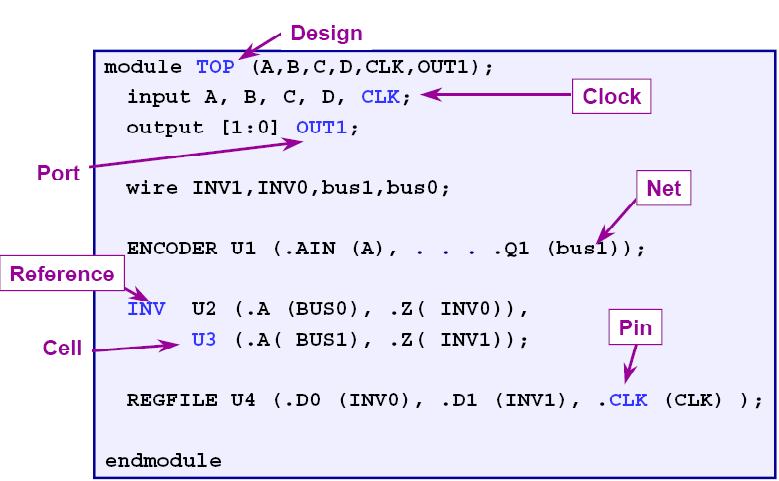

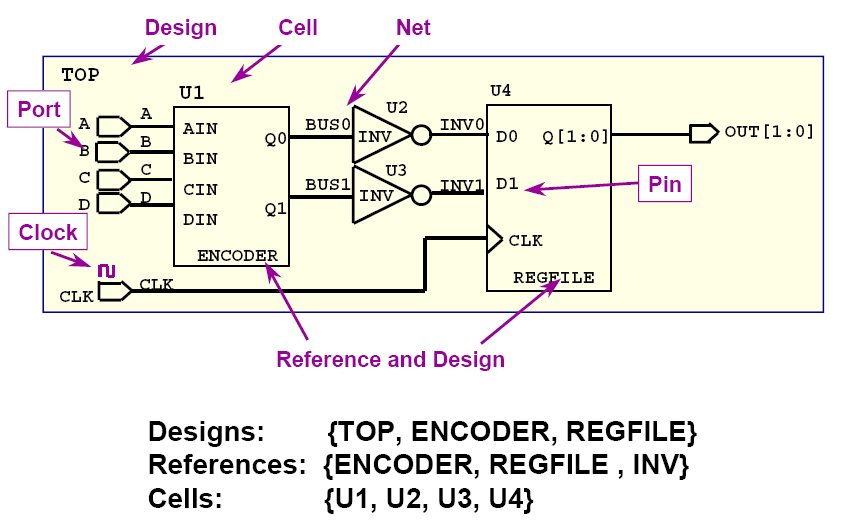

在DC中,每个设计由6个设计物体组成,它们分别是design,cell,port,pin,net和clock。其中clock是特别的端口,它存在DC内存中,是用户自己定义的物体。

DC在综合过程中会将电路划分为以下的处理对象。

- Design:整个需要综合的电路,即我们待综合的对象

- Port:最外部的端口,一般是电路与外部交互的IO口

- Clock:由于时钟上的任何问题都会对电路造成重要的影响,所以时钟需要单独处理

- Cell:被例化的模块

- Reference:例化模块的原电路

- Pin:Cell自身的引脚,注意与Port的区别

- Net:内部连线

当前设计为TOP。Port和Pin是与当前设计有关的一对概念,如果当前设计改变,相应的port和pin也会不同。

三. 设计读入

可以用以下命令读入设计:

1.analyze和elaborate命令:这是两个不同的命令,它使得设计人员可以在建立设计通用逻辑之前先对设计进行语法错误和RTL转换分析。

analyze -library <库名称> -format <文件类型> <文件名列表>

elaborate <设计名> -library <库名称> -architecture <构造体名> -parameters <参数列表> -update

2.read_file命令:

如:read_file –format verilog sd_clk.v

3.read_verilog或read_vhdl命令,这些是从read_file中分离出来的命令。

如:read_verilog sd_clk.v 读入代码后用命令current_design和link将读入的设计和综合库连接起来。

四. 设计环境

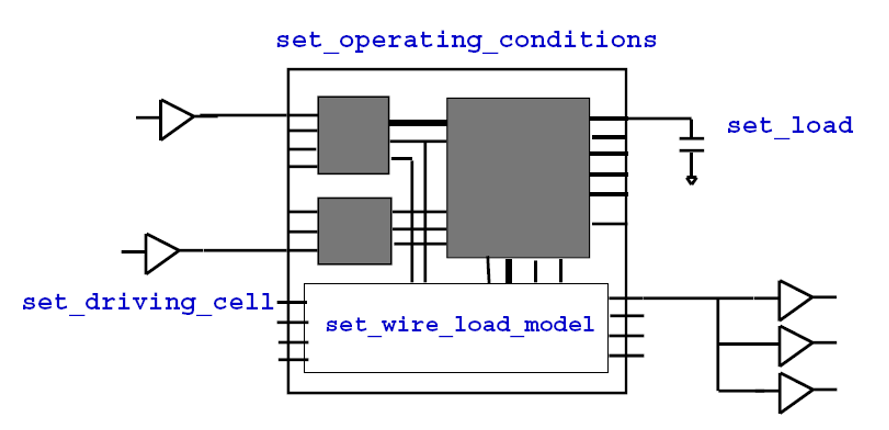

设计环境,通过环境约束的设计,将设计所处的真实环境因素包含进去,使得设计可以正常工作在真实环境下。环境约束如下图所示:

定义环境的约束条件

主要包括 : 设置环境条件: set_operating_conditions。

设置线负载模型 : set_wire_load_model。

设置驱动强度: set_drive set_driving_cell。

设置电容负载 : set_load。

设置扇出负载: set_fanout_load。

五. 设置电路的工作环境

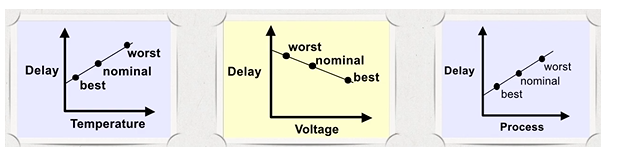

set_operating_conditions描述了设计的工艺、电压及温度条件。 它们的工作条件分别是slow(WORST),typical(TYPICAL)和fast(BEST)。工作条件包括温度、电压和工艺参数。晶圆厂提供的单元库中单元延时是在一个标准条件下得到的,比如温度为25℃,工作电压为1.8V,工艺参数为1.0。

一旦工作条件发生了改变,电路的时序特性也必将受到影响。以上三者对时序的影响如下

WORST情况通常用于综合阶段,由于在逻辑综合阶段以最大化建立时间为目标,所以工作条件通常设为最坏情況。而BEST情况通常用于修正保持时间违规。

有时可能同时用WORST和BEST情况同时优化设计,这时使用命令: set_operating_conditions -max slow -max_library slow -min fast -min_library fast 可以用set_min_library指定best和worst两种库,在设计中所用到的库都可以指定。

如: # 为综合用的sram库指定最佳情况可最坏情况

set_min_library sram_slow.db –min_vision sram_fast.db

六. 设置连线负载

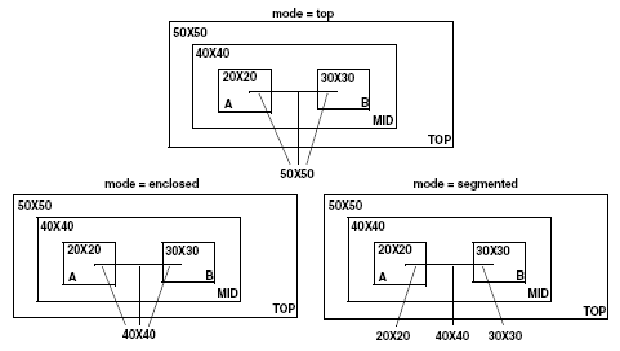

set_wire_load_model命令为DC提供估计的线负载信息,反过来DC使用线载信息把连线延迟建模为负载的函数,Synopsys工艺库里提供了多种线载模型,每个模型代表一个特定大小的模块。设计人员需要准确地选择线载模型。

设置线载模型命令如下: set_wire_load_model –name smic18_wl10 –library slow

set_wire_load_mode定义了三种同建模线负载模型相关的模式,分别是top,segmented和enclosed,如下图所示:

七. 约束设置

set_driving_cell和set_drive用于设置模块输入端口的驱动能力。set_drive命令用于指定输入端口的驱动强度,它主要用于模块或芯片端口外驱动电阻。值越小表示驱动能力越大 。

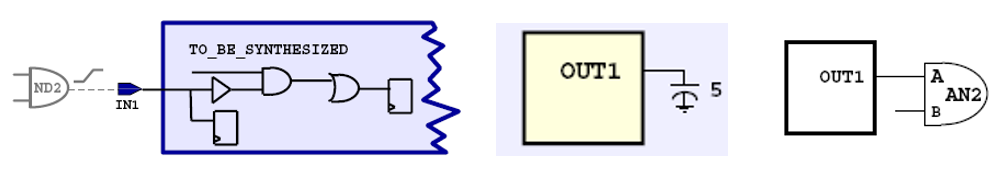

set_driving_cell用于对输入端口的驱动电阻进行建模,这一命令将驱动单元的名称作为其参数并将驱动单元的所有设计规则约束应用于模块的输入端口。 set_driving_cell –lib_cell and2a0 [get_ports IN1] \ –library slow set_drive 10 [get_ports Data_in_0]

set_load将工艺库中定义的单位(通常为pf)上的容性负载设置到设计的指定连线或端口,设置输出端口的负载。 set_load 5 [get_ports OUT1] set_load [load_of my_lib/and2a0/A] [get_ports OUT1]

7.1 drive与load

DC综合是基于路径的,每个路径上都有Cell和net,所以基于路径的综合就是计算路径上的delay和rc(DC是使用互连线模型进行估算)。

在了解delay和rc的计算时,我们要先了解一下一个cell对于drive(前级)和driven(后级)所用到的模型是什么。

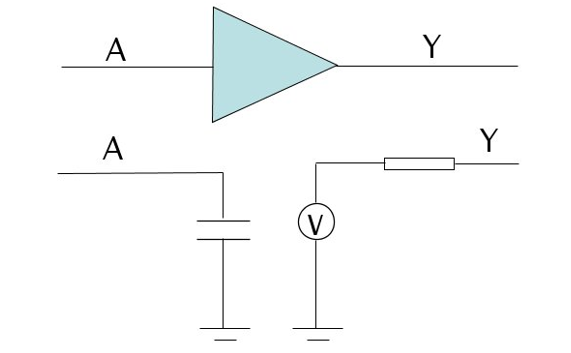

如图,一个buffer,从前级看过来是一个load(capacitance,想获得这个load,可以通过load_of buffer/a获得),从后级看来是一个drive(resistance)。

电路的的驱动能力是上一级的1/R,即电阻的倒数,驱动能力大,说明看过去的电阻小,也说明这个器件比较大(大器件有较大的驱动能力)。

电路的负载能力是下一级的load(即电容)总和,负载能力大,说明能驱动下级的器件就很多。

大器件是大电容,小电阻,而小器件是小电容,大电阻。理解这些,对于dc综合以及后端APR版图都有很好的操作。

7.2 时钟

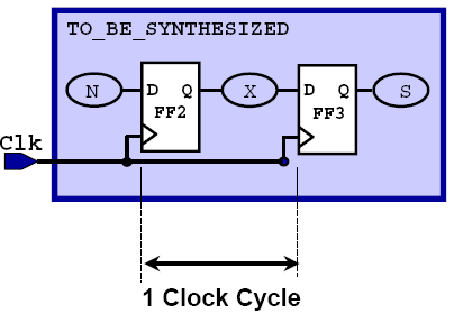

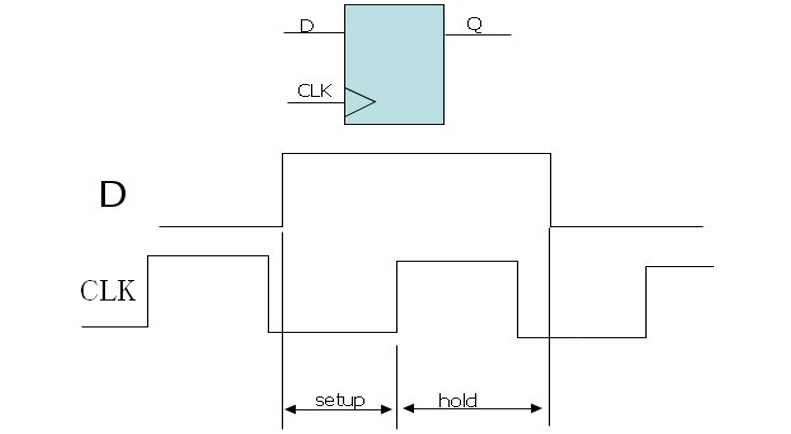

单周期同步设计的时序要求 DC默认的时序电路是单周期的,如下图所示。假设FF3的建立时间为Tsetup,保持时间为Thold,触发器FF2的时钟端到Q端的延迟为Tclk-q。

setup time即建立时间,也就说数据在时钟到来之前保持稳定所需要的时间。

hold time 即保持时间,也就是说在时钟到来之后数据需要保持稳定的时间。

Slack用于表示设计是否满足时序:正的Slack表示满足时序(时序裕量),负的Slack表示不满足时序(时序的欠缺量)。

定义时钟 create_colck –period 10 [get_port clk] 对于时钟(除了虚拟时钟)的定义来说,时钟周期和时钟源(port或pin)是必不可少的,还可以定义时钟的占空比,时钟名等。定义虚拟时钟时,不必定义时钟源。

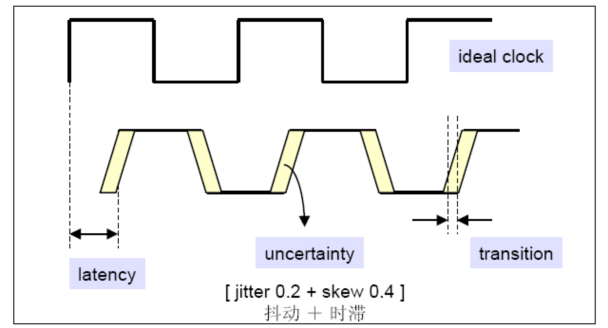

设定时钟的uncertainty、latency和transition,其中uncertainty是用来模拟时钟的skew和jitter,latency设定时钟的延迟,transition设定时钟的转换时间。通过这些设定让时钟更加接近实际情况,更有利于综合的准确性,但过分约束会使得综合起来比较困难。

由于时钟一般是高扇出(high fanout)的,DC不会对高扇出的连线做设计规则(DRC)的检查和优化。DC默认的时钟网络是理想的。在综合时不对时钟的高扇出做处理,而是留在后续的布局布线中做时钟树综合(CTS)。

set_dont_touch_network,由于时钟信号是驱动大负载的。在综合的时候综合工具会对负载进行估 计,从而在该网络上加上一些有足够驱动能力的 buffer 或者反相器,以使得电路的上升时间和下降时间能够满足要求。而前端工具无法知道连线的走向和长度,在估计时钟网络的负载时不准确,而且 floorplan 的结果将会 影响连线的长度,从而影响连线的负载,因此,前端工具不对大负载的网络进行处理,而把这个工作留到后端。所以在综合的时候需要告诉综合工具不对时钟网络进行处理。

dc_shell-t> create_clock -period 10 [get_ports Clk]

dc_shell-t> set_dont_touch_network [get_clocks Clk]

create_clock定义了一个时钟,set_dont_touch_network给时钟定义了一个 dont_touch 属性,即综合的时候不对Clk信号行优化。如果不设置dont_touch,DC会根据Clk的负载自动对他产生Buffer,而在实际的电路设计中,时钟树(Clock Tree)的综合有自己特别的方法,它需要考虑到实际布线后的物理信息,所以 DC不需要在这里对它进行处理,就算处理了也不会符合要求。

set_clock_uncertainty命令让用户定义时钟扭斜信息。基本上此命令用于给时钟的建立时间和保持时间增加一定的余量。由时钟的抖动(jitter)可扭斜(skew)组成,如下图: set_clock_uncertainty 0.6 [get_clocks CLK]

set_clock_transition命令让用户定义时钟的转换时间。

如下图:set_clock_transition 0.45 [get_clocks CLK]

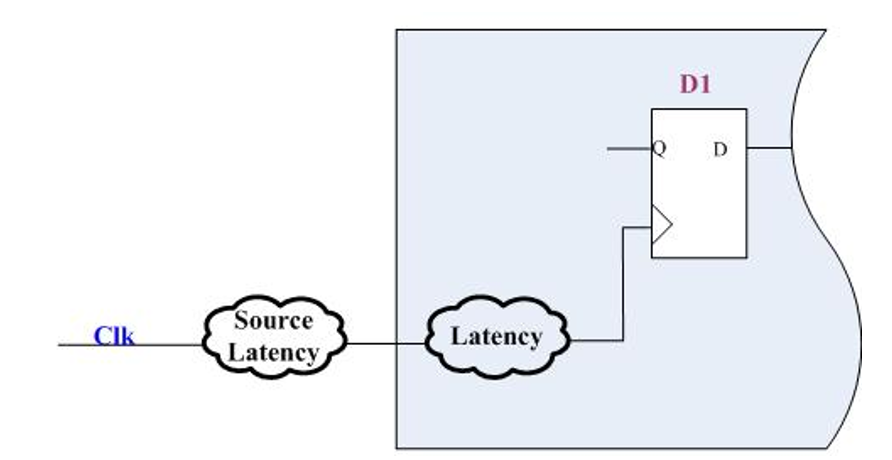

7.3 latency约束

latency,一般Latency指的是时钟端口到内部时序器件的时钟管脚的延迟。

set_clock_latency命令用于定义时钟网络的延迟,包括source_latency和network_latency。

source_latency是从时钟源到时钟定义位置的延迟,network_latency是时钟定义位置到触发器时钟输入端的延迟。

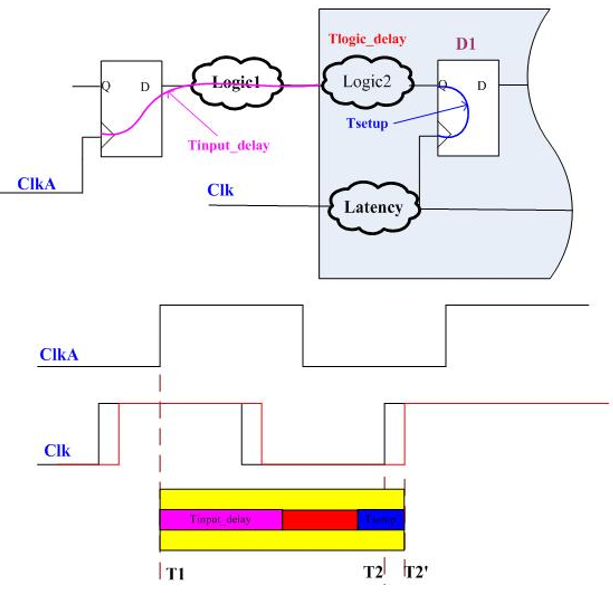

latency对于内部逻辑的影响

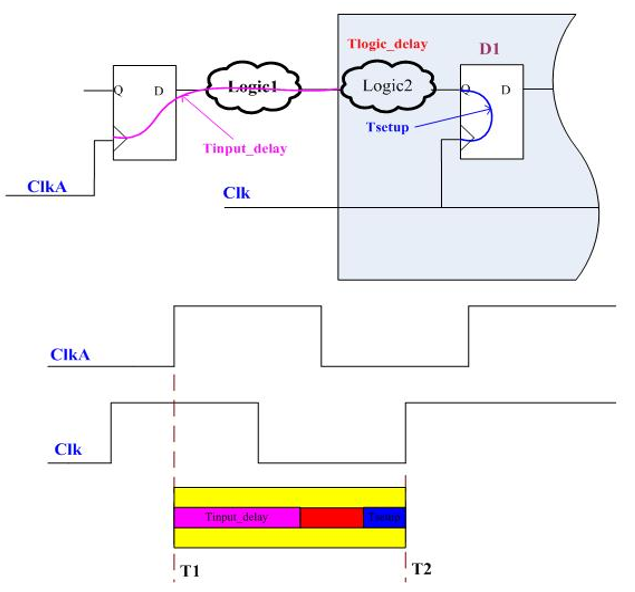

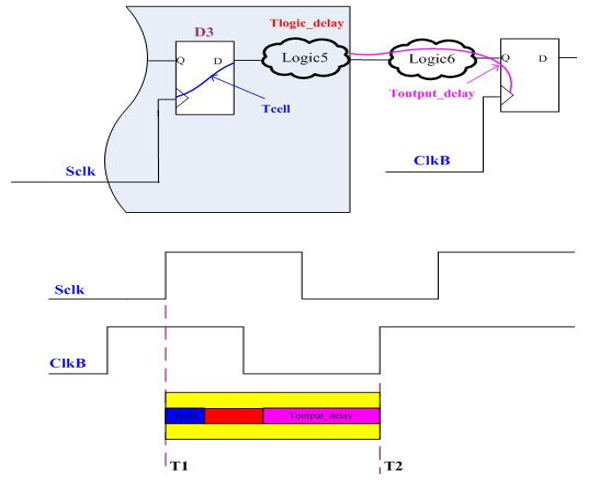

下图是不考虑latency的情况,内部逻辑延迟的限度为: T2-T1-Tinput_delay-Tsetup

当考虑了latency的时候,那么留给内部逻辑的最大延迟为:T2’(T2+Tlatency)-T1-Tinput_delay-Tsetup。会发现留给内部逻辑的延迟会变大,那么会给DC更大的空间来综合。

7.4 I/O的约束

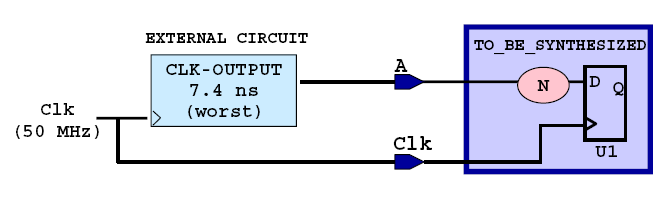

I/O的约束,input_delay是设置外部信号到达输入端口的时间,dc会用它来计算留给内部逻辑的空余时间是多少。

之所以让ClkA和Clk的时钟周期不一致,主要是用来说明上图中黄色部分的。黄色部分的确认是很重要的。这是DC用来确定时间余量(slack)的关键。

如上图所示,黄色部分已经确实是最小相位差。那么根据input_delay时间以及库中触发器的setup建立时间,可以知道留给内部逻辑的延迟时间是红色部分。

Tlogic_delay=Tmin-Tinput_delay-Tsetup

综合过程中,dc会优化Logic2的时序,以使他达到时序要求。

根据外部逻辑的延迟设定输入延迟

#创建时钟

create_clock –period 20 –name Clk [get_ports Clk]

#将时钟设置为dont_touch_network

set_dont_touch_network [get_clocks Clk]

#设置输入延迟 ,外部逻辑延迟最大值为7.4,加入-max选项

#用于setup分析(setup分析采用最慢的路径延迟)

set_input_delay 7.4 –max –clock Clk [get_ports A]

输入延时指的是被综合模块外的寄存器触发的信号在到达被综合模块之前经过的延时,在图中就是外围触发器的clk-q的延时加上M电路延时。

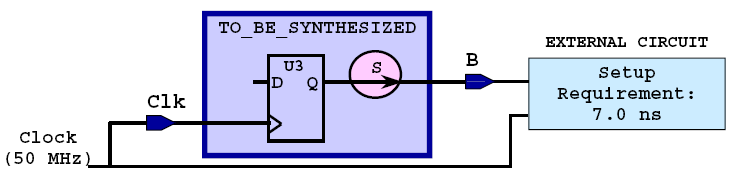

set_output_delay,set_output_delay是设置输出端口到数据采集处的延迟。 DC会根它来计算留给内部逻辑的时间。

根据外部逻辑的延迟设置输出延迟

#创建时钟

create_clock –period 20 –name Clock [get_ports Clock]

#将时钟设置为dont_touch_network

set_dont_touch_network [get_clocks Clock]

#设置输入延迟 ,外部逻辑setup要求为7.0,即为setup分析设

#定输出延迟

set_output_delay 7.0 –max –clock Clock [get_ports B]

信号在被综合模块的触发器U3里触发,被外围的一个触发器接收。对外围电路而言,它有一个T电路延时和外围触发器的建立时间。当确定了他们的延时之后,被综合模块内部的输出路径延时范围也就确定下来了 。

7.5 DRC约束

DRC即Design Rule Constraints,设计规则约束指为保证最终电路可以正常工作,而由工艺库定义的必须遵守的规则,也称隐含约束。一般用于限制在电容、翻转时间、扇出等因素影响,下一个单元可以和多少个其他单元相连,这些规则是必须遵守的,且比其他规则具有更高的优先级。设计规则约束由 set_max_transition、set_max_fanout和set_max_ capacitance组成。(工艺库本身制定了,但是可以根据需求,人为指定,更加严苛或者宽松。)

#为当前设计设定最大电容值为0.5pf

set_max_capacitance 0.5 [current_design]

#为当前设计设定最大转换时间为2.0ns,在整个设计上施加最

#大转换时间延迟可以帮助防止在上连线上出现长的转换时间,

#也可以约束单元的输出端的转换时间以减少其功耗

set_max_transition 2.0 [current_design]

#在当前设计的所有单元的输出引脚上设置max_fanout

set_max_fanout 10 [current_design]

在DC优化时,DRC约束具有最高的优先级,DC会先让电路满足DRC,然后才是时序约束。

7.6 面积约束

面积是主要的成本因素,电路面积要尽可能小,速度要尽可能快,但速度越快面积就要大。

我们用set_max_area来设定面积约束。例如:

current_design top

set_max_area 1000

set_max_area 0

上面的例子给topP的设计施加了一个最大面积1000单位的约束。1000 的具体单位是有 Foundary 规定的,定义这个单位有三种可能的标准:面积的单位由工艺库定义,可以是:

1. 2输入与非门

2. 晶体管数目

3. 平方微米

设定了面积约束,DC会尽量优化到所设定的面积;当没有设定面积约束时,DC会做最小限度的面积优化;若设定为0,则DC会对面积做优化直到再继续优化也没有大的效果,这样可以使得面积优化最小,但运行时间较长。 可用命令report_area报告面积。

7.7 时序报告和时序问题的诊断

DC中,常用report_timing命令来报告设计的时序是否满足目标。

report_timing命令的默认行为是报告每个时序路径理的关键路径。可以设置各种选项以查看不同的类型时序或不同路径的时序。具体用法可在dc_shell使用man命令来查看report_timing命令的详细介绍。

report_timing 查看具体的setup/hold时序信息。

report_area 查看综合后得到的面积。

report_reference

report_cell

report_constraint

report_power

check_design 检查设计中是否存在其他隐患问题

7.8 数据的保存

在DC综合完成后,要保存好相应的数据,输出相应的网表,SDC(设计约束文件),SDF(时序文件),供给后续的布局布线工具使用,也可以供给PT读入,检查时序是否满足。综合结果要经过PT分析满足时序要求,经过验证工具(如Formaility)的验证满足后才能提供给布局布线工具使用。 还可以保存ddc格式的文件,以便DC下次启动的时候读入,ddc文件保存了上次DC运行的各种数据。具体的命令有:

write –f verilog –hierarchy –output my_design.v 写出综合后的网表文件给后端

write –f ddc –hierarchy –output my_design.ddc 保存当前综合的数据data base。下次可以直接load后查看结果。不需要重新综合

write_sdc my_design.sdc

write_sdf my_design.sdf

电路综合完成之后,可以用 report 命令将电路的一些信息 report 出来分 析,阅读报告时主要需要注意几个部分:

-

看看报告中的综合库、线负载模型、工作条件等是不是你所要求的。

-

看看报告的路径是最大路径还是最小路径,即看报告中的 Path type 为 max,该路径是为了满足 library 中 FF 的 setup time 的要求。

-

看路径中是否有很大延迟的单元,或者输入/输出延迟是否很大

-

看关键路径上是否有 slack

-

这样综合完成之后,对于最差工作环境下的库如果没有问题,对于最好的工作情况,可能会出现 Hold time violation. 这时可用

set_fix_hold [all_clocks],之后再compile, 来让 DC 对电路中的 hold time violation 进行 处理。 -

如果在综合之后发现电路中出现 violation,即电路的时序不能满足要求,

当出现的 slack 比较小时,可以使用一些综合的选项来减小这些 slack; 如果 slack 比较大,通过综合的这些选项无法解决,则需要返回重新写 HDL 源代码。 一般在综合时 violation 较小时,可以用compile –inc –map high来减小路 径的延迟

八.设计综合(优化)

电路模块设计规划(以利于更好的进行约束),Design Compiler综合优化的过程(三大优化阶段,结构级,逻辑级,门级),时序分析的具体过程等综合过程中的一些详细信息。

1567

1567

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?