1. 面积与功耗约束

面积与功耗约束包括为面积和功耗提供指导的命令,其中设计必须适合面积和功耗要求要达到最优。 时序、功耗和面积是IC设计中最基本的矛盾面,很多时候都是得到这个就要牺牲另一个,比如为了时序更好就要插入流水线增加面积。

| set_max_area | create_voltage_area |

| set_level_shifter_threshold | set_max_dynamic_power |

| set_level_shifter_strategy | set_max_leakage_power |

1.1 set_max_area

set_max_area命令用于设置当前设计的最大面积(设置了输入端口的max_area属性),这是一种优化约束(Optimization Constraint),Design Compiler在综合的门级优化阶段的最后会尝试确保设计的总面积不超过设置的最大面积(优先级小于设计规则约束(Design Rule Constraint)和时序约束等其他优化约束,即不能以设计规则违例、时序违例为代价修复面积违例),如果不设置该约束,Design Compiler只会执行有限的单元尺寸下调和面积清理步骤。如果想要移除最大面积,使用remove_attribute命令。

area_value是一个非负的面积值,代表了需要设置在当前设计上的最大面积,它的单位要与工艺库中的面积单位一致。

1.2 create_voltage_area

在多电压域的设计中,需要根据UPF的设计创建不同的电压域,例如在UPF中创建了3个power domain,所以在PR中也需要创建3个voltage area,分别对应PD_domain,PD_PAD_domain和TOP_domain。由于工具默认会有一个DEFAULT_VA,范围是整个core area,因此我们只需要创建2个voltage area即可,分别是PD_domain和PD_PAD_domain。

create_voltage_area -power_domains PD_domain -region {{x1 y1} {x2 y2} {x3 y3} {x4 y4}}

create_voltage_area -power_domains PD_PAD_domain -region {{x1 y1} {x2 y2} {x3 y3} {x4 y4}}

上面的命令分别为power domain创建了voltage area,这样每个cell应该放在哪个位置就确定了。

1.3 set_level_shifter_threshold

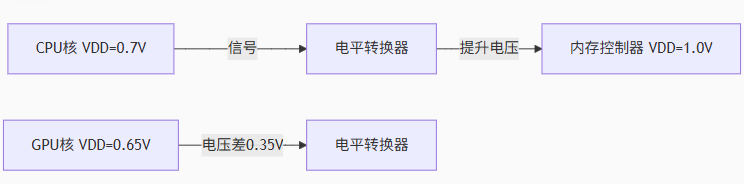

其作用是为电平转换器(Level Shifter)的自动插入设置电压阈值规则。当信号跨越不同电压域(Voltage Domain)且电压差 超过设定阈值 时,工具自动插入电平转换器电路,确保信号完整性。

# 示例:设置电压差阈值为0.3V

set_level_shifter_threshold -voltage_diff 0.3

电平转换器阈值通常与电压差和驱动强度相关。比如当两个电压域相差0.5V以上时就需要插入。这个命令允许设计者精确控制插入条件,平衡面积和性能。

电平转换器的功能:

| 场景 | 问题 | 电平转换器作用 |

|---|---|---|

| 低压→高压域信号传输 | 高压域无法识别低压逻辑电平 | 提升电压幅值 |

| 高压→低压域信号传输 | 过压导致器件击穿 | 钳位电压至安全范围 |

| 不同电源关断域间传输 | 浮空节点导致漏电路径 | 提供隔离和电压适配 |

多电压系统中电平转换器的系统使用。

1.4 set_level_shifter_strategy

set_level_shifter_strategy 是低功耗设计流程(如UPF/CPF)中的关键命令,用于控制电平转换器(Level Shifter)的插入策略和实现方式。

# 示例:设置策略为"面积优先"

set_level_shifter_strategy -strategy area_optimized

1. 方向控制

# 设置特定方向的策略

set_level_shifter_strategy -from VDD_LOW -to VDD_HIGH -strategy performance_first

2. 位置约束

# 限制LS插入位置

set_level_shifter_strategy -boundary {A B} # 仅在模块A/B边界插入

3. 单元选择

# 指定库单元类型

set_level_shifter_strategy -cell_list {LSH2L_HD LS_L2H_HD}

可以用来和它相合作的相关命令。

| 命令 | 协同效果 |

|---|---|

set_level_shifter_threshold | 定义电压差阈值触发策略 |

set_isolation | 联合实现信号隔离+电平转换 |

create_power_switch | 电源关断域自动应用power_centric策略 |

1.5 set_max_dynamic_power

set_max_dynamic_power 是一个关键的低功耗设计命令,主要用于约束动态功耗的优化目标,指导EDA工具在物理实现阶段(如综合、布局布线)主动降低电路的动态功耗。

set_max_dynamic_power 15.0 -unit mW [current_design] # 设置最大动态功耗为15mW

与多场景多模式(MCMM)分析结合,针对不同工作模式(如高性能模式、待机模式)设置差异化的功耗约束

set_scenario_options -dynamic_power true -scenario perf_mode # 在特定场景启用动态功耗优化

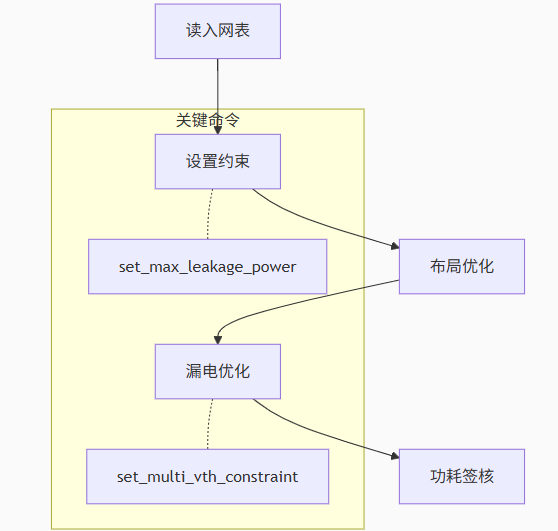

1.6 set_max_leakage_power

set_max_leakage_power 是低功耗设计流程的核心命令,专门用于约束和优化静态功耗(漏电功耗)。

set_max_leakage_power 2.0 -unit mW [get_cells SOC_CORE] # 设置模块最大静态功耗2mW

-

物理意义:强制工具将漏电功耗控制在目标值内

-

优化驱动:触发EDA工具自动应用漏电优化技术

漏电功耗公式:

P_{leak} = \sum (I_{leak,cell} \cdot V_{DD})

与实际设计阶段的协同:

| 设计阶段 | 命令作用 |

|---|---|

| 综合 | 驱动多阈值电压(Multi-Vt)单元选择 |

| 布局布线 | 指导高阈值单元(HVT)的物理摆放策略 |

| 签核 |

作为静态功耗签核的验收标准 |

命令在实际设计中的作用。

2.设计规则约束

设计规则约束包括一些为目标技术的一些特定要求提供约束指导的命令。

| set_max_capacitance | set_min_capacitance |

| set_max_transition | set_max_fanout |

2.1 set_max_capacitance

set_max_capacitance 是约束信号线最大负载电容的关键命令,直接影响时序收敛、信号完整性和功耗优化。

限制互连线和单元输入端的最大电容值,确保信号能在指定时间内完成稳定切换。

set_max_capacitance 0.2 [get_nets clk_net] # 设置clk_net最大电容0.2pF

违例情况:

| 问题类型 | 物理机制 | 芯片级影响 |

|---|---|---|

| 时序违例 | RC延迟增大(tdelay∝RCtdelay∝RC) | 建立时间/保持时间违例 |

| 信号畸变 | 上升/下降时间(Transition Time)过长 | 时钟抖动增大,数据采样错误 |

| 功耗激增 | 动态功耗 Pdyn∝C⋅V2⋅fPdyn∝C⋅V2⋅f | 局部过热,EM风险上升 |

| 串扰增强 | 高电容网络更易受相邻信号耦合影响 | 逻辑功能错误 |

实际应用中需联合 set_max_transition 和 set_max_fanout 实现多维约束优化。

2.2 set_min_capacitance

set_min_capacitance 是确保电路可靠性和信号完整性的关键约束命令,其作用与 set_max_capacitance 形成互补,共同保障设计鲁棒性。

强制信号网络保持最小负载电容,防止因负载过轻导致电路异常:

设置命令:

set_min_capacitance 0.02 [get_nets critical_net] # 设置最小电容0.02pF

产生违反的结果:

| 问题类型 | 物理机制 | 芯片级影响 |

|---|---|---|

| 信号振荡 | 高阻抗节点易受耦合噪声影响 | 逻辑状态翻转错误 |

| 电荷共享 | 动态节点电荷泄放过快 | 保持时间违例(Hold Violation) |

| 天线效应 | 小电容金属线更易积累工艺电荷 | 栅氧击穿风险上升 |

| 驱动过冲 | 低容性负载导致信号过冲 | 电磁干扰(EMI)增强 |

2.3 set_max_transition

set_max_transition 是约束信号跳变时间(Transition Time)的核心命令,直接影响时序收敛、功耗优化和信号完整性。

实际设置:

set_max_transition 0.1 [get_clocks clk_core] # 时钟信号跳变时间≤0.1ns

工具与约束之间的关系。

| 优化手段 | 实现方式 | 效果 |

|---|---|---|

| 驱动单元升级 | 替换为高驱动强度单元(BUFX4→BUFX8) | 驱动能力↑,Transition↓40% |

| 缓冲器插入 | 在长走线中插入Buffer分割RC负载 | Transition↓50-60% |

| 走线层优化 | 将高速信号分配到低电阻层(如Top Metal) | RC延迟↓30% |

| 扇出拆分 | 高扇出网络复制驱动单元 | 单路负载电容↓ |

分层约束方法 :

# 全局默认约束(宽松)

set_max_transition 0.3 -all# 关键网络严格约束

set_max_transition 0.08 [get_clocks *] # 时钟信号

set_max_transition 0.12 [get_nets -hier *rst*] # 复位信号

set_max_transition 0.15 [get_nets -hier *data*] # 数据总线

2.4 set_max_fanout

set_max_fanout 是约束信号最大扇出负载数量的核心命令,对时序收敛、信号完整性和功耗优化具有决定性影响。

set_max_fanout 32 [get_cells clk_buffer] # 限制时钟缓冲器最多驱动32个负载

fanout对设计可能会造成的问题以及带来的影响。

| 问题类型 | 物理机制 | 芯片级影响 |

|---|---|---|

| 时序恶化 | 驱动能力不足,跳变时间(Transition)延长 | 建立/保持时间违例概率↑300% |

| 信号畸变 | 远端负载接收信号不同步 | 数据采样错误率↑25% |

| 动态功耗激增 | 大负载电容充放电电流增大 | 局部功耗密度↑40%,EM风险↑ |

| 布线拥塞 | 高扇出网络集中占用布线资源 | 绕线完成率↓15-30% |

在工具优化的过程中针对fanout的优化情况与一般效果。

| 优化手段 | 实现方式 | 效果 |

|---|---|---|

| 驱动链插入 | 插入多级缓冲器(Buffer Tree)分散负载 | 单路扇出↓70%,Transition↓50% |

| 逻辑重组 | 复制驱动单元(Cell Replication) | 物理分散负载,拥塞↓40% |

| 层次化优化 | 自动识别高扇出网络(HFS),优先优化 | 关键路径延迟↓35% |

| 时钟树综合 | 专用CTS引擎重构扇出结构(H-tree/Fishbone) | 时钟偏斜↓80% |

3.接口约束

接口约束包括为假想设计提供指导的命令,此设计需要构造电路结构,同时这些

电路单元与子系统,芯片或SOC相互连接与之交互。

| set_drive | set_driveing_cell | set_input_transition |

| set_load | set_fanout_cell | set_port_fanout_number |

| set_input_delay | set_output_delay |

3.1 set_drive

set_drive,指定驱动器等效电阻,它所提供的值实际上是电阻值与驱动能力成倒数,电阻越高驱动能力越弱,过渡时间也会随之变长。

-rise或-fall用于指定驱动信号上升还是下降。当不使用-rise和-fall时,指定值同时适用于上升输入与下降输入。

3.2 set_driveing_cell

指定驱动单元的命令,-lib_cell开关用于指定驱动引脚的单元。如果在set_driving_cell没有使用到这个开关,就不知道实际的驱动单元。

当设计需要为输入引脚的上升过渡指定一个驱动单元,为输入引脚的下降过渡指定另一个驱动单元的时候,应该使用-rise/-fall限定符号。如果没有使用限定符,那么上升和下降过渡使用相同的驱动单元。

3.3 set_input_transition

set_input_transition指定过渡时间只用于特定端口,对于扇出锥中其他节点可以计算过渡时间。对于上升和下降、最小和最大过渡时间是不同的。因此,set_input_transition经常使用这些限定符为上升、下降、建立分析、保持分析指定不同的过渡时间。

3.4 set_load

当外部负载用标准负载表示时,工具把扇出值转换成了等效电容负载。表示外部负载的一个更常用的方法是直接指定外部电容值而不是扇出。-min/-max 限定符的含义和前面相同。-min用于保持分析,-max值用于建立分析。

布线完成之后,可以提取每个网络的有效净电容,对于时序分析工具,使用set_load命令能在每个网络上标注电容值。它允许使用工具提取净电容。

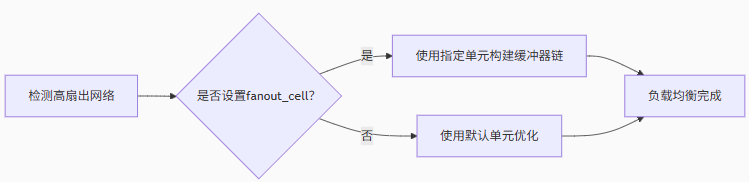

3.5 set_fanout_cell

set_fanout_cell 是高扇出网络(High Fanout Net, HFN)优化的核心命令,专门用于指定在扇出负载优化过程中使用的特定驱动单元类型。

set_fanout_cell {BUFHD12 BUFHD16} [get_nets clk_global] # 指定时钟网络使用高驱动缓冲器

命令优化的方式:

| 优化方式 | set_max_fanout通用约束 | set_fanout_cell精准控制 |

|---|---|---|

| 工作层级 | 约束驱动能力上限 | 指定物理单元实现 |

| 优化精度 | 粗粒度(仅限制数量) | 细粒度(控制单元类型/尺寸) |

| 适用场景 | 全局通用 | 关键网络定制优化 |

优化的机制:

3.6 set_port_fanout_number

set_port_fanout_number命令用于设置端口的外部扇出数量(设置了端口的fanout_number属性),正如下面关于set_load命令的博客所说,线网的互连电容总量由与其连接的端口、引脚和线网三者的互连电容组成。

直接约束设计端口的最大负载数量,为关键接口提供精准负载控制。

set_port_fanout_number 8 [get_ports clk_in] # 限制clk_in端口最多驱动8个负载单元

端口约束与网络级约束的作用。

| 约束对象 | set_max_fanout(网络级) | set_port_fanout_number(端口级) |

|---|---|---|

| 作用范围 | 芯片内部网络 | 设计输入/输出端口 |

| 优化阶段 | 布局布线阶段 | 综合阶段即介入 |

| 约束精度 | 全局/网络分组约束 | 单端口独立控制 |

| 典型应用 | 内部高扇出信号 | 关键时钟/复位/接口信号 |

4.特定模式和配置约束

假设分析的约束包括一些命令,这些命令帮助设计人员对端口和引脚的允许值做出假设。通过在特定工作模式或任意工作模式下明确排除不可能出现的情况,这些命令有助于对特定模式的设计进行更好地优化。

| set_case_analysis | set_logic_dc |

| set_logic_zero | set_logic_one |

4.1 set_case_analysis

指定一个端口或接脚在常数逻辑值1或0.案例分析是一种方法,指定一个给定的模式,而无需改变网表结构。对于当前时序分析进程,你可以指定一些信号在常数值或仅某一种转变去做验证。但你指定案例分析为常数值时,常数值通过网络进行传播,只要通过逻辑的控制值是常数值。

set_case_analysis 是静态时序分析(STA)的核心命令,用于定义电路的工作模式或特定信号状态,直接影响时序路径的分析精度和完整性。

强制指定信号在特定模式下的固定逻辑值,简化时序分析场景。

# 模块内部信号固定(需get_pins)

set_case_analysis 1 [get_pins u_ctrl/state_reg[2]] # 固定状态机bit2=1

配置DFT模式隔离。

# 功能模式分析:屏蔽扫描链

set_case_analysis 0 [get_ports scan_en]

set_case_analysis 0 [get_ports test_mode]# 测试模式分析:激活扫描链

set_case_analysis 1 [get_ports scan_en]

set_case_analysis 1 [get_ports test_mode]

4.2 set_logic_dc

set_logic_dc 是静态时序分析(STA)的关键命令,用于精确控制未连接或无关信号的状态,确保时序分析的完整性和准确性。

强制指定未连接(floating)信号为逻辑"无关"(Don't Care)状态,消除无效时序路径分析:

set_logic_dc [get_pins u_unused_module/input_pin] # 标记未使用模块输入为DC

4.3 set_logic_zero&set_logic_one

set_logic_zero 和 set_logic_one 是静态时序分析(STA)的关键命令,用于精确控制信号逻辑状态,确保时序分析的完整性和电路可靠性。

命令作用:

| 命令 | 功能 | 典型应用场景 |

|---|---|---|

set_logic_zero | 强制指定信号为逻辑0(低电平) | 未使用输入引脚接地 |

set_logic_one | 强制指定信号为逻辑1(高电平) | 未使用控制信号上拉 |

# 示例代码:

set_logic_zero [get_ports unused_in] # 悬空输入固定为0

set_logic_one [get_pins u_ip/tie_high] # IP核高电平绑定引脚

实现电气连接的物理意义。

| 逻辑状态 | 物理实现方式 | 防漏电机制 |

|---|---|---|

| 逻辑0 | NMOS下拉至GND | 阻断PMOS通路 |

| 逻辑1 | PMOS上拉至VDD | 阻断NMOS通路 |

5.设计约束异常

设计异常约束,该类约束包括帮助设计人员放宽要求的命令,此命令是由其他命令所规定的,从而提供了约束放宽的适用范围。(*标注的命令也有可能导致提供额外的收紧)

| set_false_path | set_multi_cycle_path | set_disable_timing |

| set_max_delay* | set_min_delay* |

用于指定路径上某些独特的要求或者提供宽松的附加条件,这样的约束称为时序异常。一般有三种时序异常:

1.虚假路径--它们是不需要满足任何时序要求的路径,实现工具在受约束时忽略此种路径上的时序。

2.多周期路径--它们是需要多个时钟周期来传递数据的路径,实现工具放宽此种路径上的时序。

3.最大延迟和最小延迟--它们是具有特殊要求的最大延迟和最小延迟的路径,并且在设计人员想要覆盖推测的建立和保持要求时指定的。

5.1 set_false_path

如你所知,删除特定路径的时序约束不影响电路控制。set_false_path可以禁止最大延迟(建立)检查和最小延迟(保持)检查。使用-from、-through和-to选项可以指定要声明为虚假路径的路径。该规格可以包括一个或者多个上述选项。-from和-to最多只能为每个命令指定一次,但是, -through可以在同一个命令中多次指定。

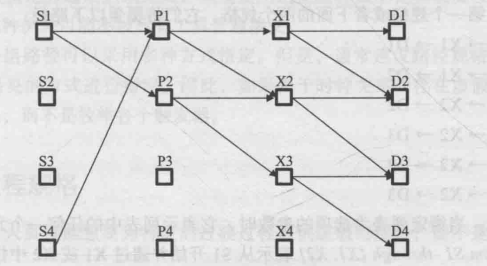

以方块代表电路图形。

图中的每一个点都代表设计中的一个元器件。(即S1,S2,S3,S4,P1,P2,P3,P4,X1,X2....)

连接线代表连接两个元器件之间的线网。

set_false_path -from S1 //表示从S1开始的所有唯一路径

set_false_path -through P1 //表示所有覆盖通过P1的所有路径

set_false_path -from S1 -through X1 //表示所有开始与S1并通过X1的所有路径

set_false_path -to D1 //表示所有终止在D1的所有路径

set_false_path命令禁止从路径起点、途径点到终点的时序。路径起点是输入端口或寄存器时钟接脚。路径途径点可以是单元、接脚或端口。路径终点是寄存器的数据接脚或输出端口。

实际上,在-from和-to中指定时钟可以提供一种简单的方式来覆盖更多的时序电路元器件。即为:set_false_path -from CLK1。可表示为:

1.所有由于CLK1触发的时序电路元件。

2.相对于CLK1约束的所有输入端口。

5.2 set_disable_timing

要禁止当前设计中一个特定单元的时序,使用set_disable_timing。这会从单元时序图上删除特定的时序弧。如此,路径上经过这些弧的路径就无法通过了。set_false_path命令仍然允许通过这些路径,只不过它们的时序约束被删除了。

set_disable_timing -from B -to ZI1 //实例中的I1从B到Z的时序弧将从时序分析中移除。

5.2 set_multi_cycle_path

set_multi_cycle_path 是静态时序分析(STA)的核心命令,用于精准管理需要多个时钟周期才能稳定的时序路径。

多周期路径指定了以下主要内容:

1.作为多周期的确切路径。

2.作为多周期路径内的过渡过程。

3.建立或保持多周期关系。

4.额外的周期时依据启动时钟还是捕获时钟。

放宽特定路径的时序约束,允许信号在多个时钟周期内稳定,避免对非关键路径的过度约束:

set_multicycle_path 2 -setup -from [get_pins data_gen*] -to [get_pins data_capture*]

多周期路径的本质。

| 路径类型 | 建立时间检查点 | 保持时间检查点 | 典型场景 |

|---|---|---|---|

| 单周期路径 | Launch clk edge N | Launch clk edge N | 寄存器到寄存器直连 |

| 多周期路径 | Launch clk edge N | Capture clk edge N+M | 跨时钟域/复杂计算 |

复杂计算单元。

# 32位乘法器(需要3周期完成)

set_multicycle_path 3 -setup -from [get_cells mult32*]

set_multicycle_path 2 -hold -from [get_cells mult32*]

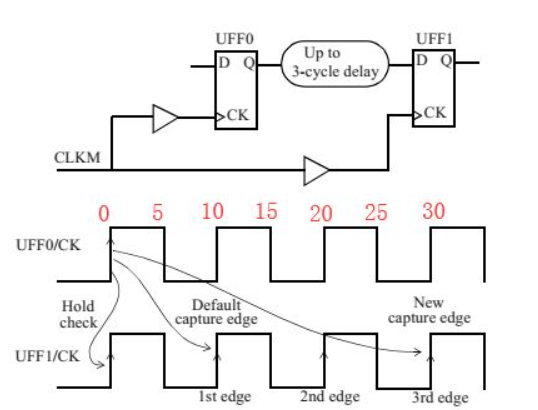

通常情况下,两个同步的 reg 进行 timing check 时,组合逻辑的 delay 必须在一个时钟周期内到达,才能满足 setup 的时序。但在某些情况下,从一个寄存器输出到另外一个寄存器的 data 端需要不止一个 cycle 的时间,而且又不影响逻辑的功能。此时,我们可以将这样的 path 约束为 multicycle path。 一个 3cycle 的 multicycle path 的电路结构图。

我们可以用下面的命令来定义约束:

create_clock -name CLKM -period 10 [get_ports CLKM]

set_multicycle_path 3 -setup -from [get_pins UFF0/Q] -to [get_pins UFF1/D]

当 UFF0/CK 作为 launch clock 时(T=0ns 时),在 T=10ns 时 UFF1/CK 采集到前一级过来的数据 。

命令设置了 3 个 cycle 的 multicycle path 的约束之后,launch clk 的沿推到了 T=30ns。因此,两个寄存器之间那段组合逻辑的 delay 要求就放松到了近三个时间 cycle。

6.其他命令

其余的SDC约束,一般是对工作条件,线负载模型,单位和时序约束版本提供约束。主要介绍几个核心的SDC约束命令。

| set_wire_load_model | set_wire_load_min_block_size |

| set_wire_load_selection_group | sdc_version |

| set_units | set_operating_condition |

6.1 set_wire_load_model

set_wire_load_model 是逻辑综合阶段的关键命令,用于在缺乏物理布局信息时估算互连线寄生效应。

set_wire_load_model

-name model_name

[-library lib]

[-min] [-max]

[object_list]

//注:该命令的选项和参数顺序任意

指定线负载模型名

-name选项用于指定一个线负载模型名,模型所在的逻辑库必须已加载到内存(这里需要注意,link_library变量或local_link_library属性(两者统称为link_path)指定的逻辑库会在必要时自动加载)。

指定搜索库。

-library选项用于指定搜索库,如果不指定-library选项,Design Compiler会在link_path指定的逻辑库中从左至右搜索指定的线负载模型(如果一个逻辑库被加载到内存,但不在link_path中,想使用其中的线负载模型时必须使用该选项);如果在-library选项中指定了多个逻辑库,则Design Compiler首先在这些指定的逻辑库中从左至右搜索指定的线负载模型,如果没有搜索到则会在link_path指定的逻辑库中从左至右搜索指定的线负载模型。

指定最大、最小条件。

-max选项用于指定线负载模型作用于最大延迟分析(一般情况下,如果不开启on_chip_variation,这指的是建立时间检查),-min选项用于指定线负载模型作用于最小延迟分析(一般情况下,如果不开启on_chip_variation,这指的是保持时间检查),如果仅指定了最大条件下的线负载模型,最小条件分析时将使用相同的线负载模型。

6.2 set_operating_condition

set_operating_conditions是静态时序分析(STA)的核心命令,用于定义芯片工作的物理环境条件(PVT:Process-Voltage-Temperature),用于设置设计的工作环境,工作环境包括温度、电压、工艺等,它们的变化会显著影响电路性能,因此所有工艺库的数据都是在一个特定的工作环境下得到的,这个环境被称为特征化环境,并根据选择的工作环境进行相应调整。确保设计在真实场景中的可靠性。

指定时序分析的工艺角、电压和温度组合,模拟芯片在真实世界的工作环境。

set_operating_conditions //通过命令指定工作模式

[condition]

[-max max_condition] [-max_library max_lib]

[-min min_condition] [-min_library min_lib]

[-library lib]

[-object_list objects]

[-analysis_type bc_wc | on_chip_variation]set_operating_conditions -name "WCCOM" \

-voltage 0.72 \ # 工作电压(V)

-temp 125 \ # 结温(℃)

-process "worst" # 工艺角

PVT对时序分析的影响。

| 参数 | 延迟变化趋势 | 数学关系 |

|---|---|---|

| 电压↓ | 单元延迟↑ | tpd∝1/Vtpd∝1/V |

| 温度↑ | 单元延迟↑ | tpd∝Ttpd∝T |

| 工艺慢 | 单元延迟↑ | tpd↑30%tpd↑30% |

1460

1460

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?