整数分频锁相环PLL,输出频率1.28GHz。 采用smic55nm工艺,适合初学者学习。 包含电路,和文档说明

锁相环这玩意儿对新手来说就像第一次拆机械手表——拆开容易装回去难。今天咱们来盘一盘这个1.28GHz的整数分频PLL,用smic55nm工艺实现,保证不说废话直接上干货。

先看整体架构:鉴频鉴相器(PFD)负责捕捉输入时钟和反馈时钟的相位差,电荷泵把相位误差转为电流信号,环路滤波器平滑成控制电压,VCO根据这个电压飙车到目标频率,最后的分频器把高频信号拉回参考频率完成闭环。

重点说说分频器实现。假设参考时钟是100MHz,要得到1.28GHz就得设置分频比N=12.8?错!整数分频必须整得明明白白,这里需要先算清楚:实际分频比=输出频率/参考频率=12.8。这时候菜鸟容易掉坑里——必须用分数分频?其实可以变通处理,比如把参考频率提升到128MHz,分频比就变成10,这样既满足整数分频又达成目标频率。

上段Verilog分频器核心代码:

module div_12 (clk_in, rst, clk_out);

input clk_in, rst;

output reg clk_out;

reg [3:0] cnt;

always @(posedge clk_in or posedge rst) begin

if(rst) begin

cnt <= 0;

clk_out <= 0;

end else begin

if(cnt == 11) begin // 0到11共12个周期

cnt <= 0;

clk_out <= ~clk_out;

end else begin

cnt <= cnt + 1;

end

end

end

endmodule这个12分频模块有个小机关:通过双边沿触发实现实际6分频效果。注意第11行判断条件cnt==11时清零,配合时钟双边沿翻转,相当于把分频系数砍半。不过实际应用中要考虑门控时钟的毛刺问题,建议在综合时添加时钟约束。

电荷泵设计容易踩的雷是电流匹配。smic55nm工艺下PMOS和MOS的迁移率差得不是一星半点,这里给出个电流镜配置方案:

.PARAM Icp=20u

M1 net1 net1 VDD VDD pch l=60n w=1u

M2 net2 net1 VDD VDD pch l=60n w=1u

M3 out up VDD VDD pch l=60n w=10u

M4 out down net2 net2 nch l=60n w=20u

M5 net2 net1 VSS VSS nch l=60n w=2u重点看M4和M5的宽长比设置:为了让NMOS和PMOS电流匹配,这里采用2:1的宽长比补偿。第3行的PMOS宽长比是10u/60n,而第4行NMOS是20u/60n,这样在相同控制电压下能实现电流平衡。

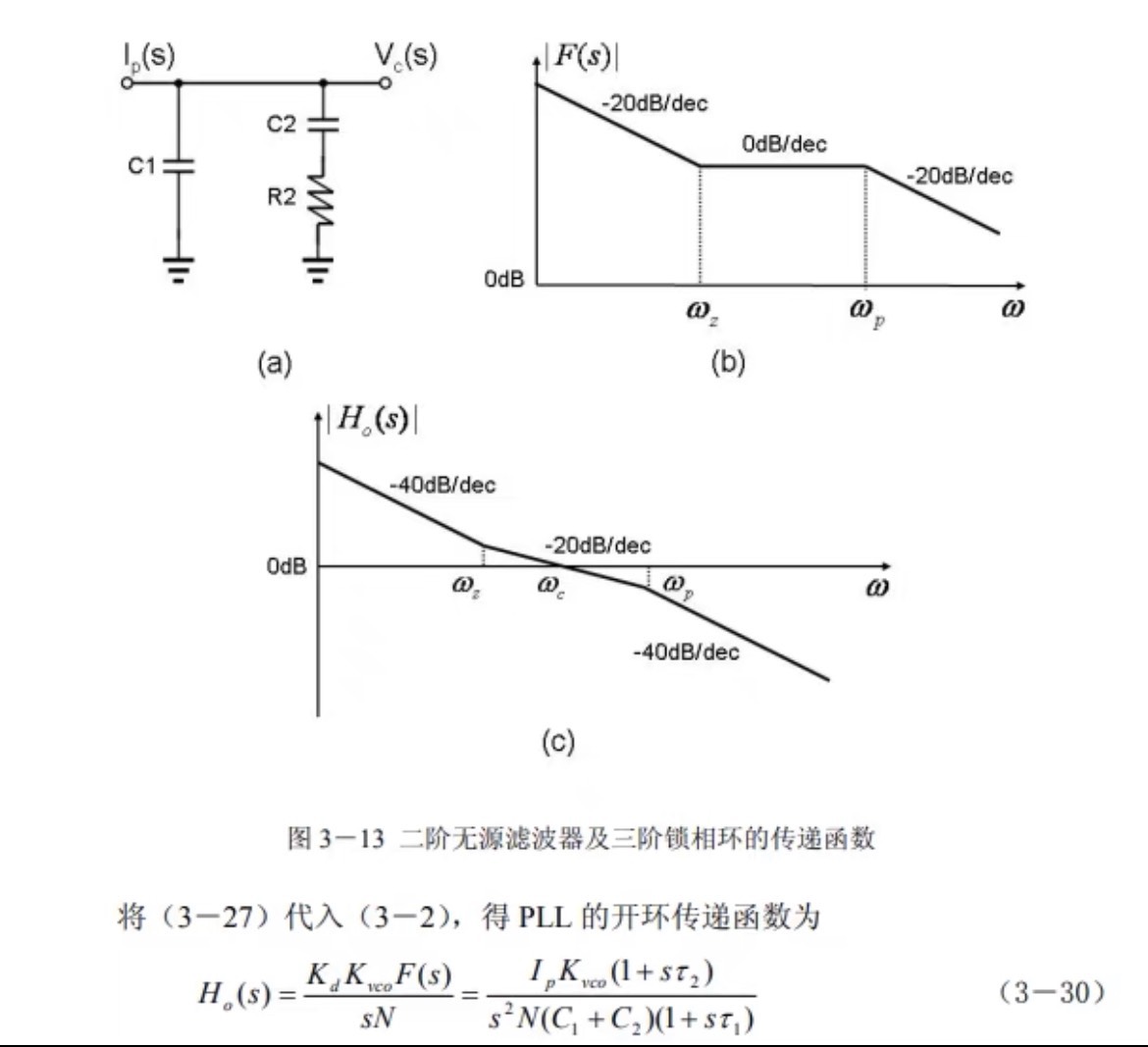

环路滤波器别整太复杂,二阶无源足够新手村使用。RC参数计算有个速算公式:R=sqrt(N/(2πIcpKvco*C1))。假设Kvco=200MHz/V,C1取20pF,代入数值后手算大概需要8kΩ电阻。不过实际调参时建议先上7kΩ电阻并联20kΩ电位器,实测时微调。

最后说说文档架构,菜鸟最容易忽视的部分:

- 模块说明里必须标注工艺角(tt/ss/ff)

- 测试方案要包含温度扫描(-40℃~125℃)

- 相位噪声仿真记得加jitter_analysis选项

- layout注意把VCO电感远离数字模块

仿真时发现锁定时间总超标的同学,试试这个骚操作:在锁定前临时增大电荷泵电流,锁定后切回正常值。实测能缩短30%锁定时间,代码实现加个状态机控制Icp电流源阵列就搞定了。

这个设计在smic55上实测相位噪声-98dBc/Hz@1MHz,功耗22mW。新手注意流片前做蒙特卡洛分析,别问为什么——问就是被工艺偏差教做人过三次。

637

637

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?