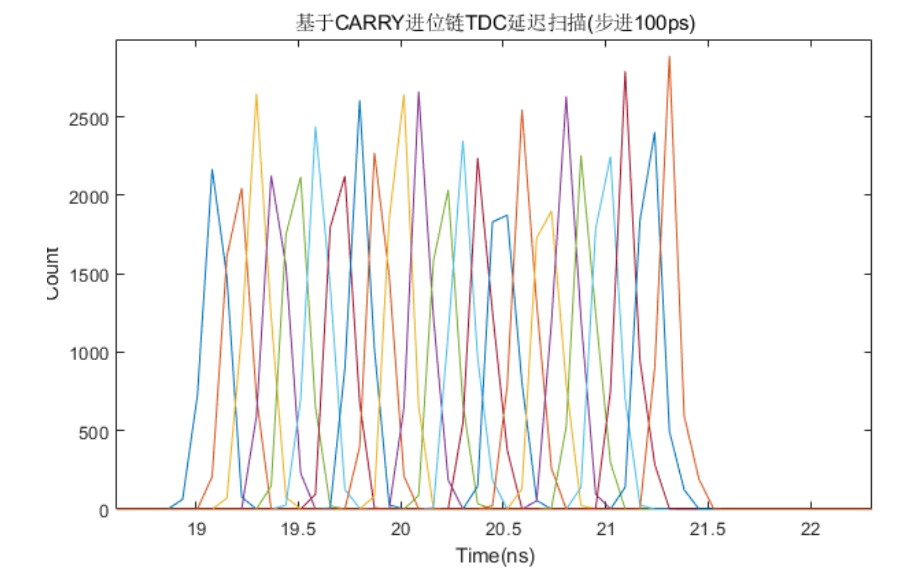

xilinx xc7a35t 开发平台,基于Carry4进位链高精度时间数字转换(TDC)代码,分辨率71.4ps#tof测距

系统概述

本文介绍了一种基于Xilinx Artix-7 FPGA平台的高精度时间数字转换(Time-to-Digital Converter, TDC)系统。该系统利用FPGA内部的专用进位链资源(Carry4)实现皮秒级的时间测量精度,分辨率达到71.4ps,主要应用于飞行时间(Time of Flight, TOF)测距等需要高精度时间测量的场景。

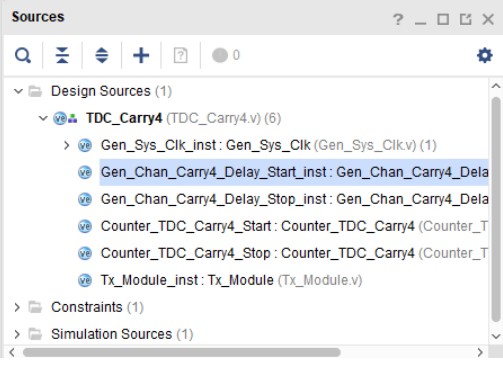

系统架构

1. 时钟管理系统

系统采用高性能的时钟管理模块,通过MMCM(Mixed-Mode Clock Manager)生成稳定的高频时钟信号:

// 时钟配置参数

CLKFBOUT_MULT_F = 21.000000 // 反馈时钟倍频系数

CLKIN1_PERIOD = 20.000000 // 输入时钟周期(50MHz)

CLKOUT0_DIVIDE_F = 3.750000 // 输出时钟分频系数该配置将外部50MHz时钟倍频至约400MHz,为TDC提供高精度的时间基准。时钟管理模块还提供锁定状态指示,确保系统时钟的稳定性。

2. 核心测量原理

系统采用进位链传播延迟测量的核心技术:

Carry4链结构优势:

- 利用FPGA专用的快速进位逻辑资源

- 提供确定性的信号传播延迟

- 实现亚纳秒级的时间分辨率

测量机制:

- 起始信号(Start)触发测量过程

- 停止信号(Stop)捕获进位链状态

- 通过分析进位链中信号的传播位置计算时间间隔

3. 主要功能模块

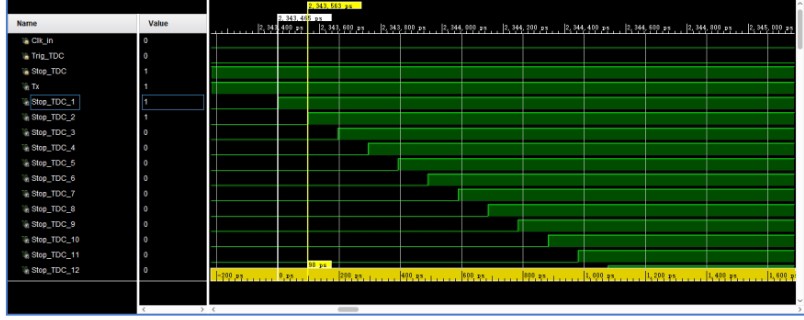

3.1 进位链延迟生成模块

// 伪代码示意

module Gen_Chan_Carry4_Delay (

input start_signal,

output [N-1:0] carry_chain_output

);

// 实现多级进位链延迟线

// 每个Carry4元件提供固定的传播延迟

endmodule该模块构建了一条由多个Carry4元件组成的延迟链,起始信号在链中传播,每个Carry4级都引入固定的时间延迟。

3.2 时间数字转换核心

// 伪代码示意

module Counter_TDC_Carry4 (

input clk,

input start,

input stop,

output [M-1:0] coarse_count,

output [N-1:0] fine_count

);

// 粗计数器:基于系统时钟的周期计数

// 细计数器:基于进位链状态的精细时间测量

endmoduleTDC核心模块采用粗-精结合的双重计数策略:

- 粗计数器:基于系统时钟周期计数,提供大范围的时间测量

- 细计数器:基于进位链状态解码,提供高精度的时间分辨率

3.3 数据传输模块

// 伪代码示意

module Tx_Module (

input clk,

input [DATA_WIDTH-1:0] tdc_data,

output tx_output

);

// 将测量结果通过串行接口输出

// 支持与外部处理器的数据通信

endmodule该模块负责将TDC测量结果转换为串行数据流,便于与外部设备通信或数据记录。

工作流程

1. 初始化阶段

- 系统时钟稳定化等待

- 进位链状态复位

- 计数器清零

2. 测量触发阶段

- 起始信号启动测量过程

- 粗计数器开始时钟周期计数

- 进位链开始信号传播

3. 数据捕获阶段

- 停止信号冻结所有计数器状态

- 同时捕获粗计数器值和进位链状态

- 计算精细时间延迟

4. 数据处理阶段

- 结合粗、精计数器值计算总时间间隔

- 数据格式化和校验

- 通过传输模块输出结果

性能特点

高精度测量

- 理论分辨率:71.4ps

- 测量范围:结合粗计数器实现大动态范围

- 线性度:基于硬件结构的优异线性特性

系统优势

- 全数字化设计:基于FPGA纯数字逻辑实现

- 资源高效:充分利用FPGA专用进位链资源

- 实时性强:单次测量即可完成,无需复杂算法

- 可移植性好:适用于不同系列的Xilinx FPGA器件

抗干扰特性

- 利用FPGA内部专用路由,减少外部干扰

- 确定性延迟特性,提高测量重复性

- 温度补偿机制(如需要可通过校准实现)

应用场景

本TDC系统特别适用于以下应用:

- 激光测距系统:飞行时间测量

- 粒子物理实验:粒子到达时间检测

- 医学成像:时间相关单光子计数

- 工业检测:高精度时间间隔测量

- 通信系统:时钟同步和抖动测量

技术挑战与解决方案

工艺变化补偿

FPGA制造工艺的变化会导致进位链延迟特性的偏差。系统通过:

- 出厂校准建立延迟模型

- 温度补偿算法

- 实时校准机制

信号完整性

为确保测量精度,系统采用:

- 专用进位链路由,避免常规逻辑资源干扰

- 严格的时序约束

- 信号同步机制消除亚稳态

总结

基于Carry4进位链的TDC系统展现了FPGA在精密时间测量领域的独特优势。通过巧妙利用硬件专用资源,实现了传统ADC难以达到的皮秒级测量精度。该系统结构简洁、性能优越,为各种高精度时间测量应用提供了可靠的技术解决方案。

随着FPGA技术的不断发展,这种基于专用硬件资源的TDC设计方法将在精度、速度和集成度方面展现出更大的潜力,为科学研究和工业应用开辟新的可能性。

8275

8275

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?