1. 基于FPGA数字识别仿真工程,图像处理,verilog设计。 2. 配套视频讲解。

一、文档概述

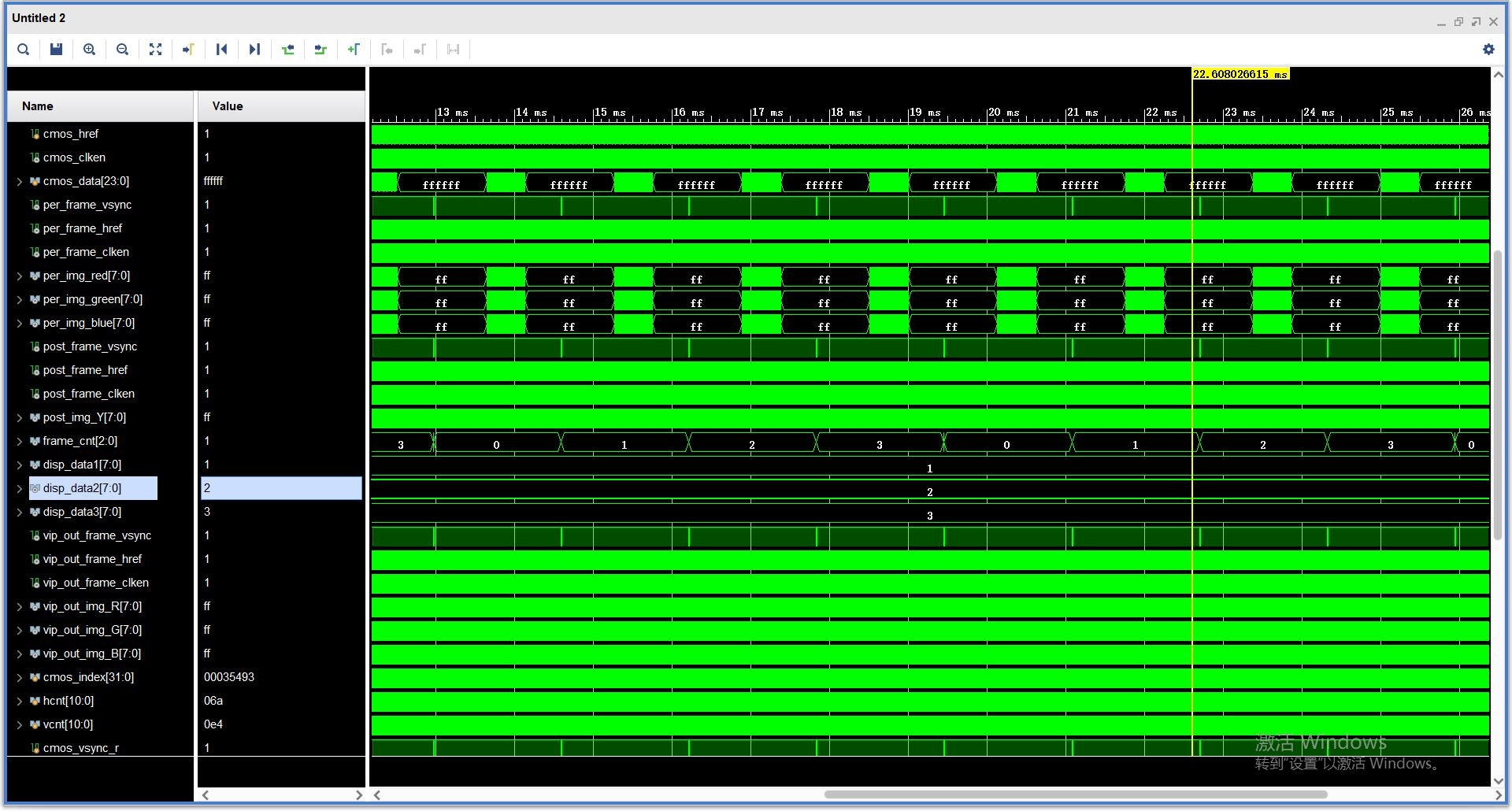

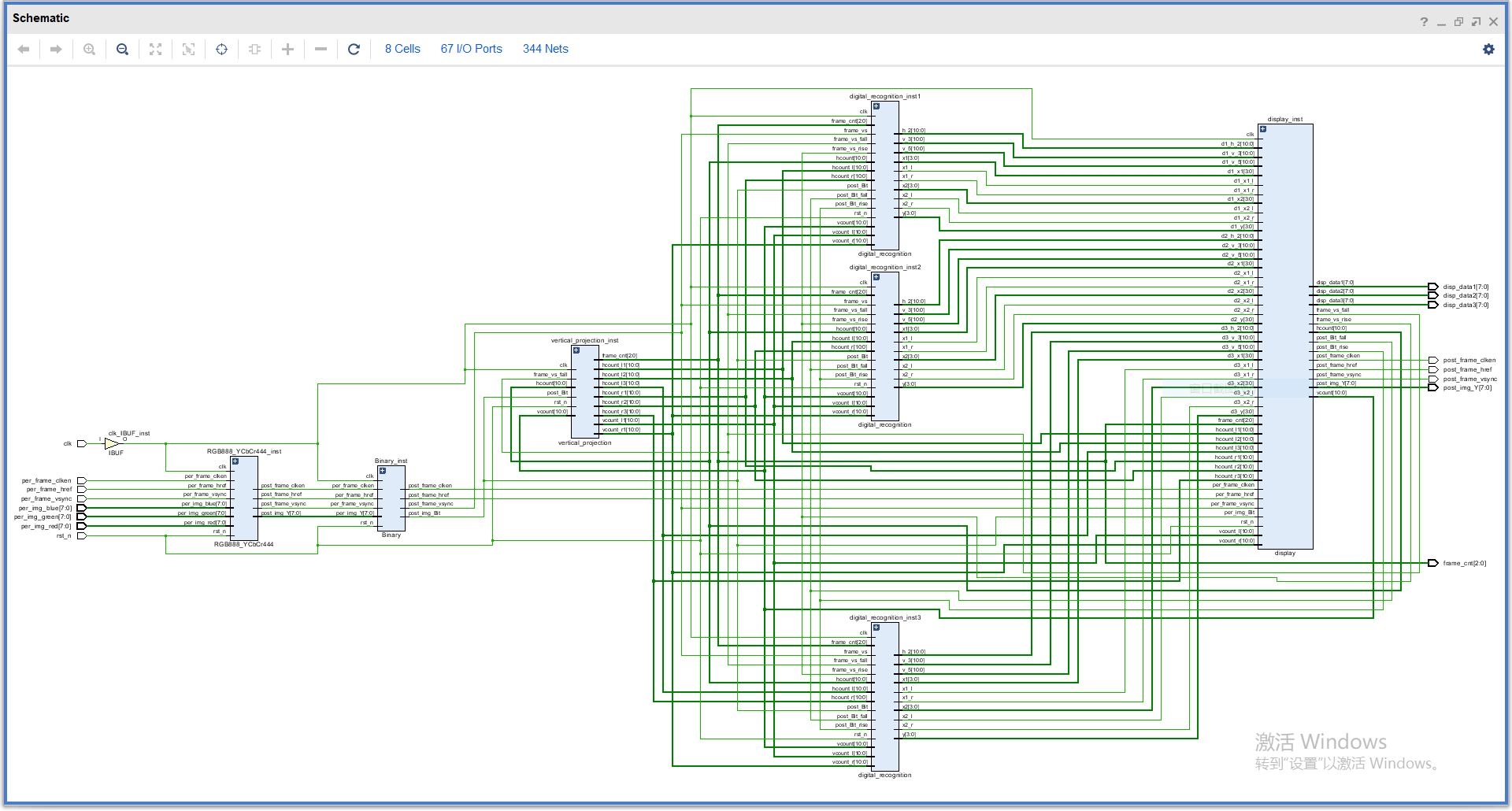

本文档聚焦于基于Xilinx Vivado 2018.3开发环境构建的ShiftRAM3X3_8bit模块,该模块作为FPGA数字识别仿真工程中图像处理环节的核心组件,主要实现3x3窗口的8位图像数据缓存与移位操作,为后续图像滤波、特征提取等算法提供稳定的数据窗口支撑。文档将从模块设计背景、核心功能、接口定义、关键参数、工作原理、仿真特性及工程应用场景等维度,全面解析模块的技术细节与实用价值。

二、设计背景与工程定位

在FPGA数字图像识别系统中,图像处理算法(如边缘检测、均值滤波、阈值分割等)常需以3x3像素窗口为基本运算单元——即通过当前像素与其周围8个相邻像素的联合计算,实现图像特征提取或噪声抑制。传统数据传输方式难以直接提供“窗口化”数据,需通过缓存结构对连续输入的图像数据流进行暂存与重组。

ShiftRAM3X38bit模块正是为解决这一问题设计,基于Xilinx的cshiftramv12012IP核构建,专门针对8位灰度图像数据(常见图像数据格式),实现3行3列像素数据的实时缓存与移位输出,为下游数字识别算法(如数字轮廓提取、模板匹配)提供符合时序要求的窗口数据,是连接“图像数据输入”与“算法运算”的关键中间层。

三、核心功能描述

1. 8位图像数据缓存

模块支持8位宽的并行数据输入(D接口),可直接对接图像传感器或前级数据预处理模块输出的灰度图像数据(像素值范围0-255)。通过内部移位RAM阵列,模块能暂存多行图像数据,确保数据在时钟同步下无丢失、无错序缓存,为窗口数据构建提供基础。

2. 3x3窗口数据移位生成

这是模块的核心功能。对于连续输入的图像数据流(按行扫描顺序),模块通过行内移位+跨行缓存的双重机制,实时构建3x3像素窗口:

- 行内移位:单一行的8位数据按时钟节拍依次移位,实现“左移更新”,即新输入像素替换最左侧像素,中间像素依次左移;

- 跨行缓存:通过3组独立的移位RAM通道,分别缓存当前行、前一行、前两行数据,最终在输出端(

Q接口)同步输出3行3列的窗口数据,供下游算法直接调用。

3. 同步控制与复位管理

模块严格遵循时钟同步设计,所有数据移位、缓存操作均在CLK时钟上升沿完成,确保时序稳定性;同时支持高电平有效的同步复位(SCLR),复位信号触发时,内部RAM阵列将清零,所有输出置为初始值(00000000),避免上电或异常场景下的脏数据干扰。

4. 功能仿真支持

模块配套生成了专门的仿真网表(Verilog与VHDL两种版本),用于功能验证阶段的时序仿真。仿真网表保留了模块的所有外部接口与内部核心逻辑映射,可直接接入FPGA仿真环境,验证数据移位、窗口生成、复位等功能的正确性,但不包含物理实现相关的时序约束,不可用于综合或比特流生成。

四、接口定义与参数解析

1. 外部接口详情

| 接口名称 | 方向 | 位宽 | 功能描述 | 时序特性 |

|---|---|---|---|---|

D | 输入 | 8bit | 8位图像数据输入接口,接收前级模块输出的灰度像素值 | 与CLK同步,在时钟上升沿采样 |

CLK | 输入 | 1bit | 全局时钟信号,模块所有操作的同步基准 | 推荐频率100MHz(可根据工程需求调整),占空比50% |

SCLR | 输入 | 1bit | 同步复位信号,高电平有效 | 复位期间,Q接口输出00000000,复位释放后恢复正常操作 |

Q | 输出 | 8bit | 3x3窗口数据输出接口,按特定顺序输出窗口内像素 | 与CLK同步,时钟上升沿更新输出 |

2. 关键配置参数

模块通过IP核参数配置实现功能定制,核心参数及含义如下:

- 数据宽度(

C_WIDTH):配置为8bit,匹配灰度图像数据的位宽需求,确保数据无截断或位扩展; - RAM深度(

C_DEPTH):配置为320,对应图像行像素数(如320列图像),确保单一行数据可完整缓存并移位; - 复位初始值(

CSINITVAL/CAINITVAL):均配置为00000000,复位时内部RAM与输出均清零,避免初始噪声; - 同步优先级(

CSYNCPRIORITY):配置为1,确保复位信号(SCLR)的优先级高于数据输入,避免复位与数据写入冲突; - RAM类型(

CSHIFTTYPE):配置为0,采用线性移位模式,适配行扫描图像数据的顺序移位需求。

五、工作原理深度解析

1. 内部结构简化模型

模块内部基于cshiftramv120_12IP核构建,核心结构包含3个并行的移位RAM通道(对应3x3窗口的3行数据),每个通道的工作流程如下:

- 数据写入:

D接口输入的像素数据按行顺序,依次写入当前行的移位RAM; - 行内移位:每个时钟周期,当前行RAM内的数据左移1位,最左侧数据溢出并传入下一行RAM的输入端;

- 跨行传递:前两行RAM的数据同样按时钟移位,最终3个RAM的输出端分别对应3x3窗口的“前两行”“前一行”“当前行”数据,经逻辑组合后通过

Q接口输出完整窗口。

2. 3x3窗口生成时序

以图像行像素序列P11, P12, P13,..., P1n(第1行)、P21, P22, P23,..., P2n(第2行)、P31, P32, P33,..., P3n(第3行)为例,窗口生成过程如下:

- 当

P33输入时,第1行RAM缓存P11-P13、第2行RAM缓存P21-P23、第3行RAM缓存P31-P33,Q接口输出窗口[P11,P12,P13; P21,P22,P23; P31,P32,P33]; - 下一时钟周期,

P34输入,第3行RAM左移,P31溢出并传入第2行RAM,第2行RAM左移后P21传入第1行RAM,第1行RAM左移后P11溢出,最终Q接口输出窗口[P12,P13,P14; P22,P23,P24; P32,P33,P34],实现窗口的“右移更新”。

3. 复位与时钟同步机制

- 复位机制:

SCLR为高电平时,内部所有寄存器与RAM阵列将被强制清零,Q接口输出00000000;SCLR拉低后,模块从下一个CLK上升沿开始重新接收数据并构建窗口; - 时钟同步:所有数据采样(

D接口)、移位(RAM内部)、输出(Q接口)操作均在CLK上升沿执行,确保整个模块的时序收敛,避免亚稳态风险。

六、仿真网表特性

1. 仿真网表用途与限制

模块生成的ShiftRAM3X38bitsimnetlist.v(Verilog)与ShiftRAM3X38bitsimnetlist.vhdl(VHDL)文件,仅用于功能仿真,不可用于综合或FPGA编程,核心特性如下:

- 保留了外部接口与内部逻辑的功能映射,可直接与测试激励模块(Testbench)对接,验证窗口生成、复位等功能;

- 不包含物理实现相关的约束(如时钟延迟、布线资源映射),无法用于时序分析或比特流生成;

- 包含加密的IP核内部逻辑(通过

pragma protect关键字保护),确保Xilinx IP核的知识产权,用户无需修改加密部分即可正常仿真。

2. 仿真环境适配

仿真网表适配主流FPGA仿真工具,包括:

- Synopsys VCS:支持Verilog网表的功能仿真,需加载配套的加密密钥(网表中已包含

SNPS-VCS-RSA-2密钥块); - Mentor QuestaSim:支持Verilog与VHDL网表,网表中包含

MGC-VELOCE-RSA等适配密钥; - Xilinx Vivado Simulator:原生支持,可直接导入工程进行仿真验证。

七、工程应用场景与注意事项

1. 典型应用场景

- FPGA数字识别系统:作为图像处理前端,为数字区域检测、字符分割算法提供3x3窗口数据,助力提取数字边缘、轮廓等特征;

- 实时图像滤波:配合下游滤波算法(如Sobel边缘检测、中值滤波),提供滤波所需的邻域像素数据,提升图像质量;

- 高速图像采集系统:适配100MHz时钟下的高速数据传输,支持320列以内的图像分辨率,可扩展至VGA(640x480)分辨率(需调整

C_DEPTH参数至640)。

2. 工程集成注意事项

- 时钟约束:需在FPGA工程中为

CLK接口添加时序约束,确保时钟频率与模块设计一致(推荐100MHz),避免时序违例; - 复位时序:

SCLR信号需保持至少1个CLK周期的高电平,确保内部RAM完全清零,避免复位不彻底导致的脏数据; - 数据对齐:前级数据输入模块需与

ShiftRAM3X3_8bit的CLK同步,避免异步数据输入导致的采样错误; - 参数调整:若图像分辨率变更(如列数从320改为640),需重新配置

C_DEPTH参数(对应改为640),并重新生成IP核与仿真网表。

八、总结

ShiftRAM3X3_8bit模块作为FPGA数字识别仿真工程的关键组件,通过高度集成的移位RAM结构,实现了8位图像数据的3x3窗口实时生成,解决了图像处理算法中“邻域数据获取”的核心问题。其时钟同步设计、灵活的参数配置与完善的仿真支持,确保了模块在不同分辨率、不同算法场景下的适配性与可靠性。在实际工程中,需重点关注时序约束、复位机制与数据对齐,以充分发挥模块的性能,为下游数字识别算法提供稳定、高效的数据支撑。

FPGA 3x3移位RAM模块功能详解

FPGA 3x3移位RAM模块功能详解

1762

1762

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?