一、说明

agx orin默认只有1个万兆网卡可以正常使用,该网卡的型号是AQR113C。如果需要扩展网口就需要使用RGMII接口。

1.1 常用的PHY接口

常见的 PHY 接口除了 RGMII 外,还有 MII、RMII、GMII、SMII 等。它们的区别如下表所示:

| 接口类型 | 全称 | 数据位宽 | 支持速率 | 时钟频率 | 主要特点 |

|---|---|---|---|---|---|

| MII | Media Independent Interface(媒体独立接口) | 4 位 | 10Mbps 和 100Mbps | 10Mbps 时为 2.5MHz,100Mbps 时为 25MHz | 接口信号较多,共 16 根线(不含时钟线),适用于早期设备,“媒体独立” 意味着任何类型的 PHY 设备都可工作,无需重新设计或更换 MAC 硬件 |

| RMII | Reduced Media Independent Interface(简化媒体独立接口) | 2 位 | 100Mbps | 50MHz | 是 MII 的简化版,引脚数减少至 7 个,MAC 和 PHY 需使用相同的时钟源,节省引脚资源和成本,适用于高密度端口 PHY |

| GMII | Gigabit MII(千兆媒体独立接口) | 8 位 | 10Mbps、100Mbps 和 1000Mbps | 10/100Mbps 时与 MII 相同,1000Mbps 时为 125MHz | 向下兼容 MII 接口,可支持千兆以太网,数据传输速度更快,但引脚数较多 |

| RGMII | Reduced GMII(简化千兆媒体独立接口) | 4 位 | 10Mbps、100Mbps 和 1000Mbps | 125MHz | 是 GMII 的简化版,通过在时钟的上升沿和下降沿传输数据来保持千兆速率,占用引脚数较少,但 PCB 布线时对时钟、控制和数据线等长处理要求高,时序约束严格 |

| SMII | Serial MII(串行媒体独立接口) | 1 位 | 100Mbps | 通常为 50MHz 或更高 | 收发数据位宽为 1bit,相对于 RMII 管脚更少,MAC 和 PHY 共用一个参考时钟,接口距离不能太远 |

| SSMII | Serial Sync MII(串行同步媒体独立接口) | 1 位 | 100Mbps | 根据具体情况而定 | 与 SMII 类似,收发采用单独的时钟和同步信号,虽增加了两个管脚,但接口之间的传输距离可以更远 |

| SGMII | Serial Gigabit Media Independent Interface(串行千兆媒体独立接口) | 串行 | 1000Mbps | 根据具体情况而定 | 通过将数据串行化来减少引脚数量,特别适用于对板载空间和引脚数量要求严格的应用 |

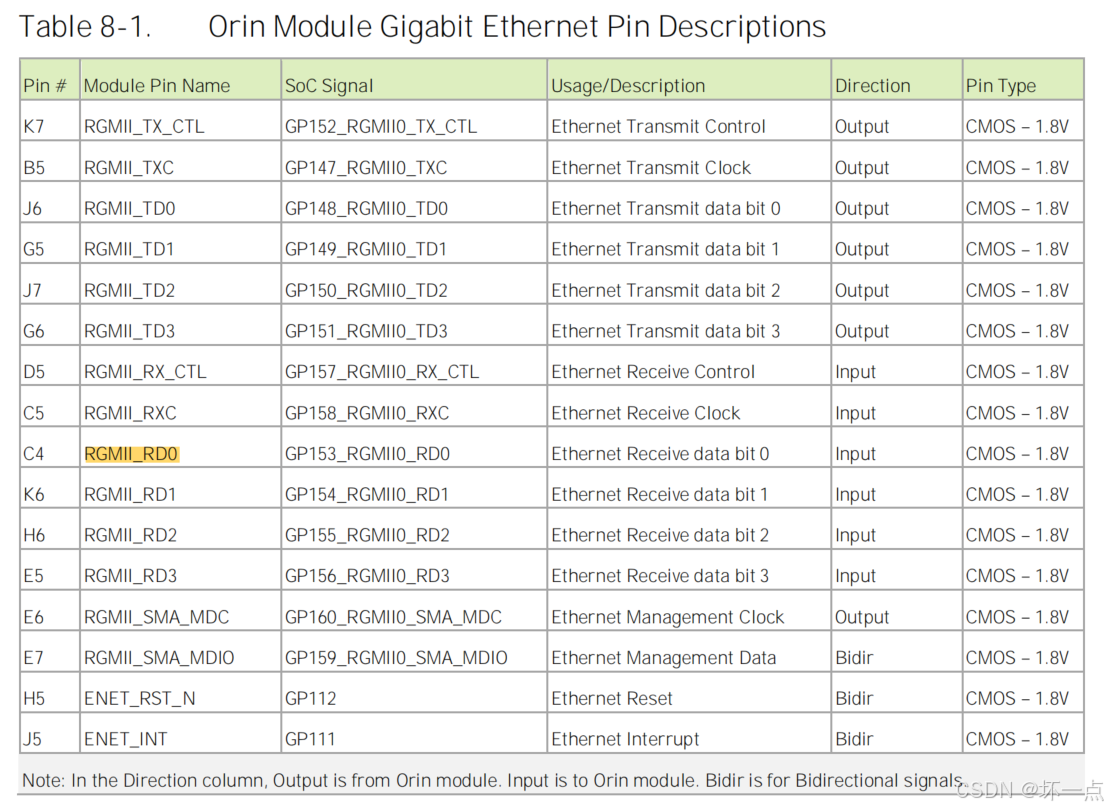

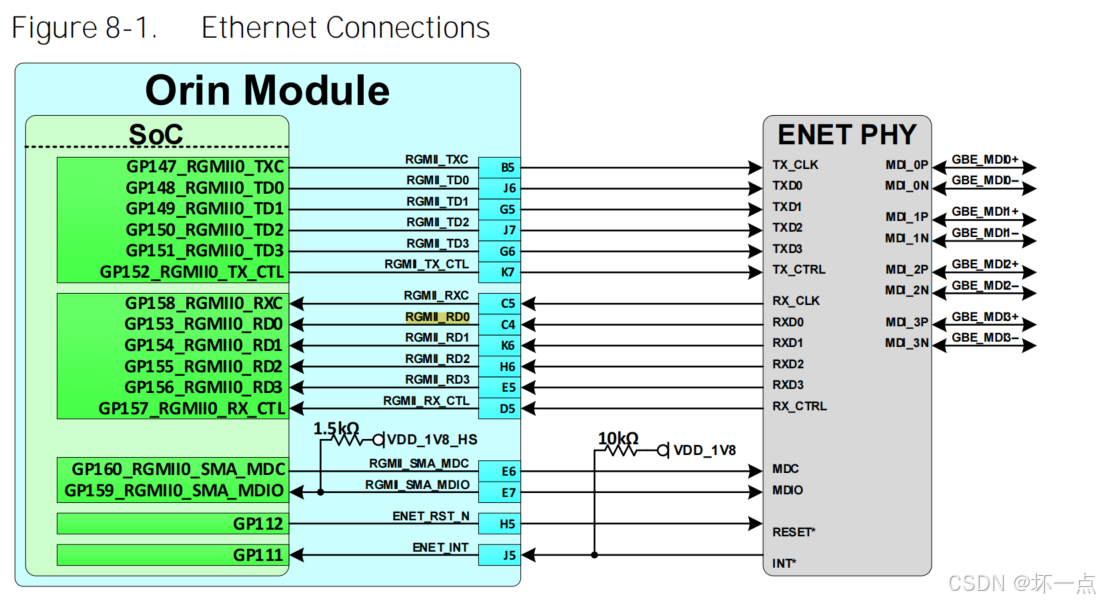

1.2 agx orin的RGMII

参考手册:Jetson_AGX_Orin_Series_Design_Guide_DG-10653-001_v1.5.pdf第”Chapter 8.Gigabit Ethernet“。

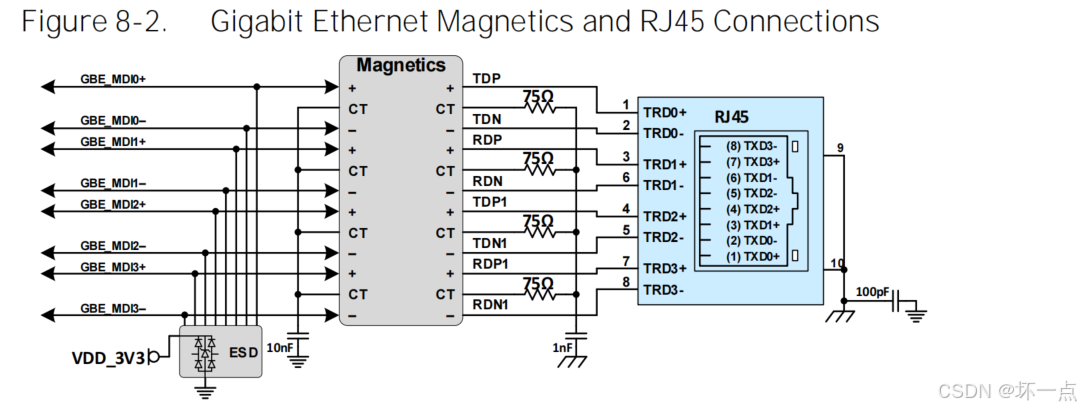

Orin 模块提供一个 RGMII 接口,以支持 1000兆以太网功能。以太网 PHY、磁隔离器和 RJ45 连接器并未集成在 Orin 模块上,必须在 Orin 模块外部进行实现。

1.3 88EA12PB2介绍

88EA1512B2 芯片是由Marvell(美满电子)生产,基本特性如下:

| 参数 | 详情 |

|---|---|

| 芯片类型 | 千兆位以太网收发器 |

| 实现标准 | 实现了 1000BASE - T、100BASE - TX 和 10BASE - T 标准的以太网物理层部分 |

| 应用领域 | 支持广泛的汽车应用,包括 RGMII 到铜 / 光纤 / SGMII 与自动媒体检测、RGMII 到铜、RGMII 到 SGMII / 光纤以及 SGMII 到铜连接等场景 |

| 符合标准 | 符合 AEC - Q100 2 级标准(工作温度范围为 - 40℃至 + 105℃) |

| 集成特性 | 在 PHY 中集成了 MDI 接口终端电阻,简化电路板布局并降低成本 |

| 延迟性能 | 与非优化设计相比,PHY 发送和接收延迟降低了 40%,总(RX + TX)延迟 < 400 ns(对于具有 1518 字节帧的 100BASE - TX 和 1000BASE - T 模式) |

| 其他特性 | 支持带有硬件加速的 IEEE 1588v2,提供 16 个 PHY 地址,更容易编程 |

| 封装形式 | 56 引脚 QFN 封装,0.5 毫米间距,8 毫米 x8 毫米 |

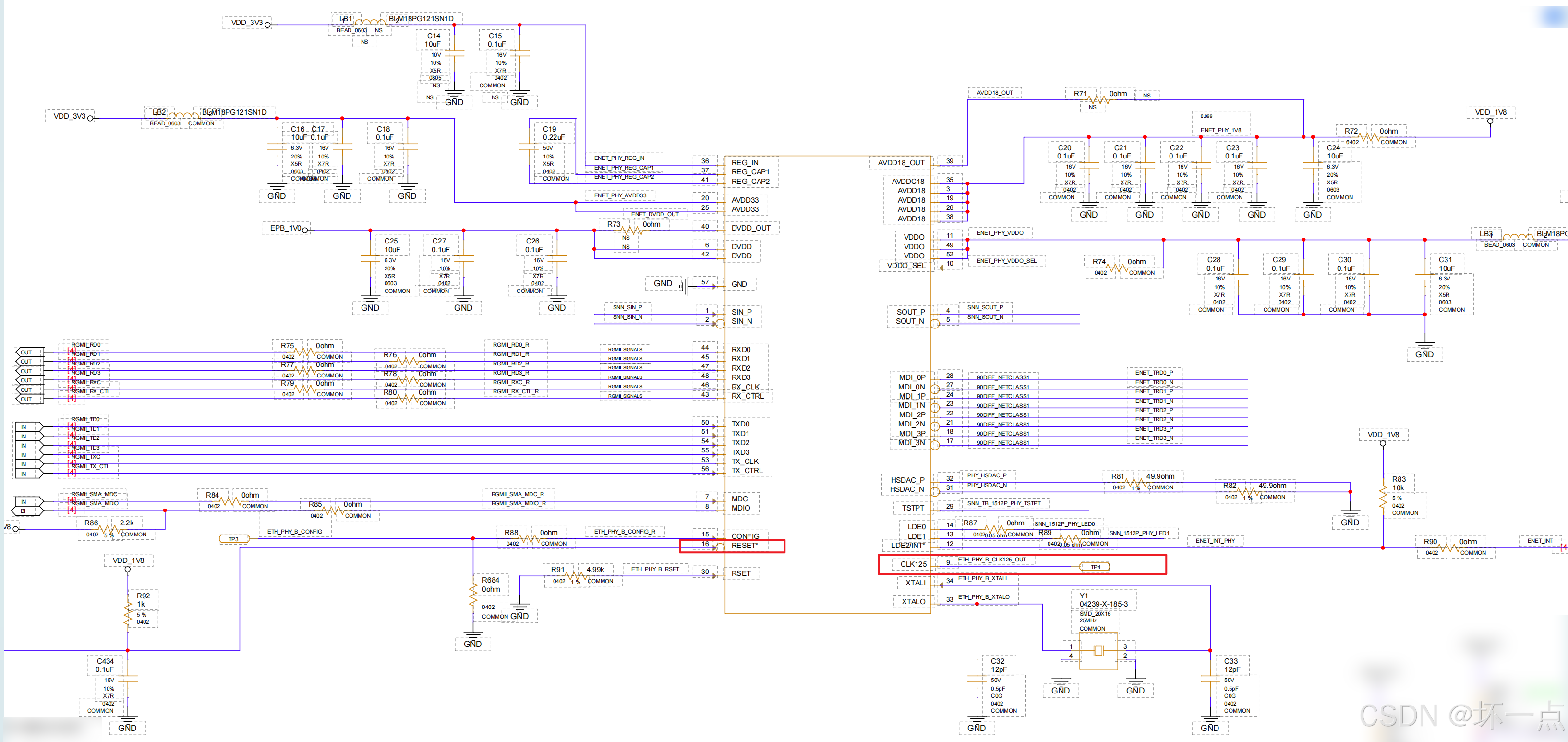

二、电路图设计

| 电路模块 / 信号 | 功能与关键元件 | 备注 |

|---|---|---|

| 电源供电(如 VDD_3V3、VDD_1V8 等) | 为 PHY 芯片及周边电路提供工作电压,通过电感(如 L4、L6 )、电容(如 C10、C14、C15 等)滤波稳压,保障电源纯净,避免干扰 | 不同电压轨适配芯片不同供电需求,电容起去耦、滤波作用,电感抑制电源噪声 |

| RGMII 接口信号(如 RXD0 - RXD3、TXD0 - TXD3、RX_CLK、TX_CTL 等) | 实现 PHY 与主控芯片间以太网数据收发,是 RGMII 协议的物理层信号传输通道 | 用于千兆以太网数据交互,遵循 RGMII 时序规范,传递收发数据、时钟及控制信号 |

| MDIO 接口信号(MDIO、MDC ) | 用于对 PHY 芯片进行配置和状态读取,是以太网 PHY 常用的管理接口 | 通过 MDIO(数据)和 MDC(时钟)信号,主控可读写 PHY 寄存器,实现参数配置、状态查询 |

| 复位电路(RESET# 等) | RESET# 为复位信号,低电平有效时触发 PHY 芯片复位,恢复初始状态,保障初始化流程 | 确保 PHY 启动或异常时能重置,需关注复位电平、复位时间等参数,配合芯片复位时序 |

| 时钟电路(如 XTAL 相关、CLK25 等 ) | XTAL 为晶振,提供基础时钟信号;CLK25 可能是 25MHz 时钟输出或输入,为 PHY 及相关模块提供定时基准 | 时钟是电路时序核心,晶振频率及时钟质量影响以太网数据收发同步性、稳定性 |

| 以太网差分信号(如 SIN_P/N、SOUT_P/N、HSDA_P/N 等 ) | SIN_P/N 为接收差分信号,SOUT_P/N 为发送差分信号,HSDA_P/N 等可能是其他高速差分链路,用于以太网信号的差分传输,抗干扰能力强 | 差分信号利用正负电压差传输数据,可有效抑制共模噪声,提升信号传输距离和可靠性 |

| 滤波与匹配电路(电阻、电容、电感组合 ) | 电阻(如 R73、R74 等)用于阻抗匹配、限流;电容(如 C20 - C24 等)滤波、隔直;电感(如 L4、L6 )滤波、扼流,保障信号质量,满足阻抗要求 | 不同元件在信号链路、电源链路中协同,优化信号完整性,适配以太网信号传输特性 |

三、驱动设计

默认agx orin的SDK包含marvel的phy芯片驱动,在驱动设计上需要完成设备树的配置、

3.1 设备树配置

第一步:补充千兆PHY的配置

platform/t23x/common/kernel-dts/t234-common-cvb/tegra234-p3711-ethernet.dtsi

/ {

/* EQOS */

ethernet@2310000 {

status = "okay";

nvidia,mac-addr-idx = <0x1>;

nvidia,if-name = "eth1";

nvidia,phy-reset-gpio = <&tegra_main_gpio TEGRA234_MAIN_GPIO(G, 5) 0>;

phy-mode = "rgmii-id";

phy-handle = <&phy>;

/delete-node/ fixed-link;

mdio {

compatible = "nvidia,eqos-mdio";

#address-cells = <1>;

#size-cells = <0>;

phy: phy@0 {

reg = <0>;

#if TEGRA_ETHERNETPHY_DT_VERSION >= DT_VERSION_2

/* use phy in poll mode */

#else

interrupt-parent = <&tegra_main_gpio>;

interrupts = <TEGRA234_MAIN_GPIO(G, 4) IRQ_TYPE_LEVEL_LOW>;

#endif

marvell,copper-mode;

/* Setup LED[2] as interrupt pin (active low) */

marvell,reg-init = <0x03 0x12 0x7fff 0x880>;

};

};

};

};

| 节点/属性 | 配置说明 |

|---|---|

| ethernet@2310000 | EQOS以太网控制器节点,基地址为0x2310000 |

| status | 设备状态为"okay",表示设备可用 |

| nvidia,mac-addr-idx | MAC地址索引,设置为0x1 |

| nvidia,if-name | 网络接口名称设置为"eth1" |

| nvidia,phy-reset-gpio | PHY复位GPIO引脚配置为TEGRA234_MAIN_GPIO(G, 5) |

| phy-mode | PHY模式设置为"rgmii-id"(RGMII带内部延迟) |

| phy-handle | 引用PHY设备节点 |

| /delete-node/ fixed-link | 删除固定链路配置,使用自动协商 |

| mdio | MDIO总线节点,用于管理PHY设备 |

| compatible | 兼容nvidia,eqos-mdio设备 |

| #address-cells | 地址单元格数量为1 |

| #size-cells | 大小单元格数量为0 |

| phy@0 | PHY设备节点,地址为0 |

| reg | PHY设备地址为0 |

| interrupt-parent | 中断控制器父节点为tegra_main_gpio |

| interrupts | 中断配置为TEGRA234_MAIN_GPIO(G, 4),低电平触发 |

| marvell,copper-mode | 启用铜缆模式 |

| marvell,reg-init | PHY寄存器初始化设置:在寄存器0x03的0x12偏移处写入0x880,屏蔽值为0x7fff |

第二步:配置PHY接口引脚

新建platform/t23x/common/kernel-dts/t234-common-cvb/tegra234-p3737-eqos-pinmux.dtsi

/ {

/* EQOS */

pinmux@2430000 {

pinctrl-names = "default", "drive", "unused";

pinctrl-0 = <&pinmux_default>;

pinctrl-1 = <&drive_default>;

pinctrl-2 = <&pinmux_unused_lowpower>;

pinmux_default: common {

eqos_txc_pe0 {

nvidia,pins = "eqos_txc_pe0";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_DISABLE>;

};

eqos_td0_pe1 {

nvidia,pins = "eqos_td0_pe1";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_DISABLE>;

};

eqos_td1_pe2 {

nvidia,pins = "eqos_td1_pe2";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_DISABLE>;

};

eqos_td2_pe3 {

nvidia,pins = "eqos_td2_pe3";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_DISABLE>;

};

eqos_td3_pe4 {

nvidia,pins = "eqos_td3_pe4";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_DISABLE>;

};

eqos_tx_ctl_pe5 {

nvidia,pins = "eqos_tx_ctl_pe5";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_DISABLE>;

};

eqos_rd0_pe6 {

nvidia,pins = "eqos_rd0_pe6";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_ENABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

eqos_rd1_pe7 {

nvidia,pins = "eqos_rd1_pe7";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_ENABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

eqos_rd2_pf0 {

nvidia,pins = "eqos_rd2_pf0";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_ENABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

eqos_rd3_pf1 {

nvidia,pins = "eqos_rd3_pf1";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_ENABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

eqos_rx_ctl_pf2 {

nvidia,pins = "eqos_rx_ctl_pf2";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_ENABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

eqos_rxc_pf3 {

nvidia,pins = "eqos_rxc_pf3";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_ENABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

eqos_sma_mdio_pf4 {

nvidia,pins = "eqos_sma_mdio_pf4";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

eqos_sma_mdc_pf5 {

nvidia,pins = "eqos_sma_mdc_pf5";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_DISABLE>;

};

soc_gpio17_pg4 {

nvidia,pins = "soc_gpio17_pg4";

nvidia,function = "rsvd0";

nvidia,pull = <TEGRA_PIN_PULL_UP>;

nvidia,tristate = <TEGRA_PIN_ENABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

nvidia,lpdr = <TEGRA_PIN_DISABLE>;

};

soc_gpio18_pg5 {

nvidia,pins = "soc_gpio18_pg5";

nvidia,function = "rsvd0";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_DISABLE>;

nvidia,lpdr = <TEGRA_PIN_DISABLE>;

};

};

pinmux_unused_lowpower:unused_lowpower {

};

drive_default:drive {

};

};

};

第三步:包含设备树文件

在soc/t23x/kernel-dts/tegra234-soc/tegra234-soc-eqos.dtsi文件增加:

#include <t234-common-cvb/tegra234-p3711-ethernet.dtsi>

#include <t234-common-cvb/tegra234-p3737-eqos-pinmux.dtsi>

第四步:使能千兆网口

找到ethernet@2310000节点,将status = "disabled";注释掉

第五步:单独编译生成设备树文件

make -C Linux_for_Tegra/source/public/kernel/kernel-5.10 ARCH=arm64 LOCALVERSION="-tegra" CROSS_COMPILE=/opt/orin/bin/aarch64-buildroot-linux-gnu- O=/Linux_for_Tegra/source/public/kernel_out -j2 --output-sync=target dtbs

生成的设备树文件在: Linux_for_Tegra/source/public/kernel_out/arch/arm64/boot/dts/nvidia/tegra234-p3701-0004-p3737-0000.dtb

第六步:验证

将dtb文件替换板子根文件系统/boot/dtb/kernel_tegra234-p3701-0004-p3737-0000.dtb (需要注意文件名称不一样)

通过ifconfig等网络命令可以看到eth1的网卡名称。

3.2 PHY芯片调试

如果设备树配置完成并替换,agx orin上电后找不到eth1的网卡名称,此时需要动用手段进行PHY芯片的调试,用来确定是PHY芯片电路设计问题还是驱动问题。

该内容参考《nvidia agx orin驱动PHY芯片(调试)》

604

604