nvidia agx orin驱动千兆网卡88EA12PB2上节介绍的nvidia agx orin驱动千兆网卡,如果未顺利识别,则需要进行调试。

一、PHY芯片介绍

| 维度 | 描述 |

|---|---|

| 功能 | - 实现 OSI 模型物理层功能 - 处理电 / 光信号转换 - 信号调制解调 - 错误检测(如 CRC) - 速率适配(10/100/1000Mbps) - 自动协商(与对端设备协商参数) |

| 接口类型 | - MAC-PHY 接口:GMII/RGMII/SGMII/TBI/RTP 等 - 物理介质接口:RJ45(电口)、SFP(光口)、MIIM(管理接口,用于寄存器配置) |

| 集成度 | - 低集成度:仅含 PHY 功能,需外接 MAC 控制器 - 高集成度:集成 MAC+PHY(如某些 SoC 内置) - 附加功能:部分集成交换芯片、PoE 供电、硬件卸载功能(如 TCP 分段) |

| 典型应用 | - 以太网交换机 / 路由器 - 网卡(PCIe 转 RJ45) - 工业控制网络 - 数据中心服务器网卡 |

| 关键参数 | - 传输速率(1G/2.5G/5G/10Gbps) - 功耗(如 IEEE 802.3az 能效以太网) - 支持的线缆类型(UTP / 光纤) - 工作温度范围(工业级 / 消费级) |

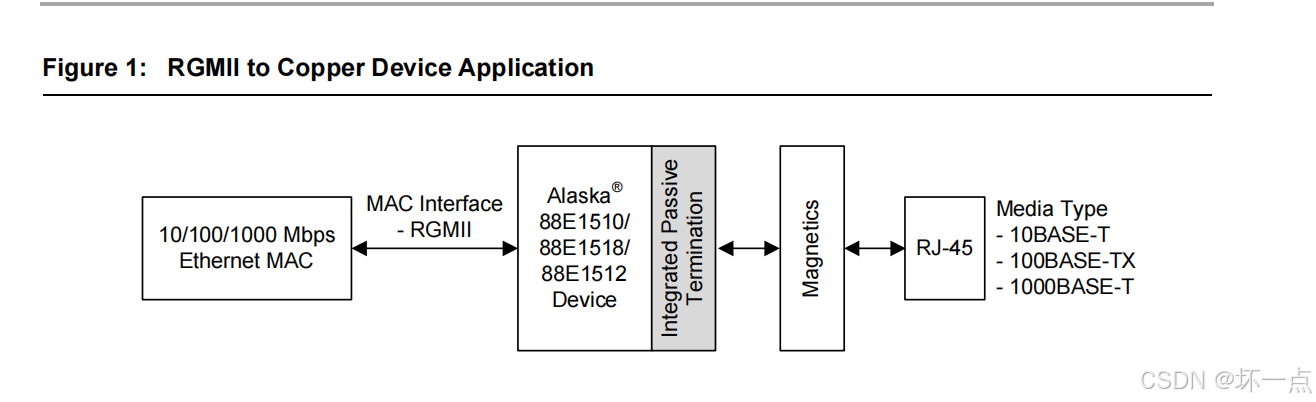

二、agx orin与88EA12PB2连接方式

(1)agx orin的Gigabit Ethernet控制器含有mac;

(2)agx orin与88EA12的数据通信,通过RGMII接口;

(3)agx orin与88EA12的控制,通过MDIO接口;

三、PHY芯片调试手段

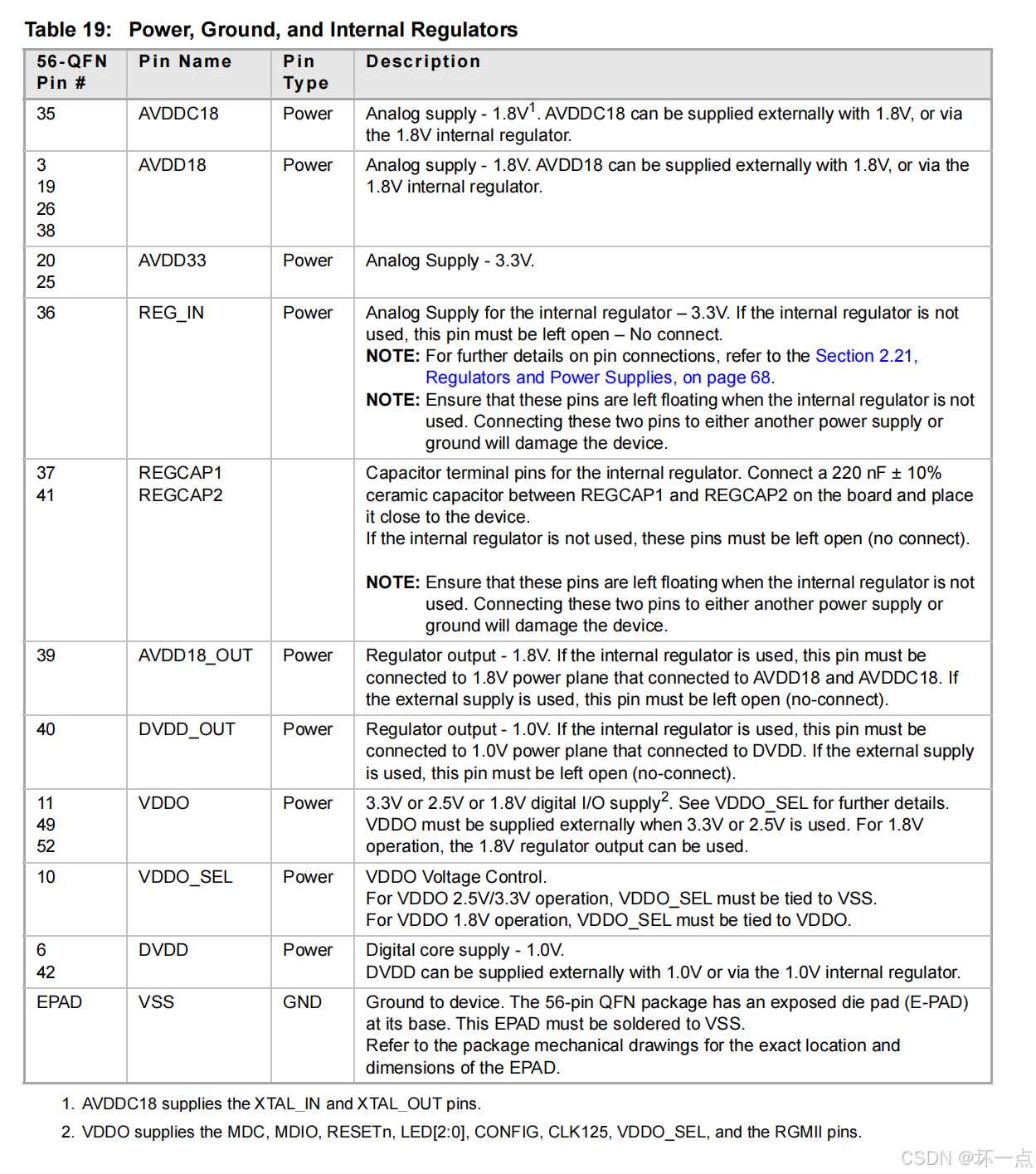

3.1 PHY芯片供电是否正常

使用万用表测试供电点是否正常,1.8V或3.3V。

3.2 判断驱动是否加载

执行:dmesg | grep 2310000 #其中0x2310000是千兆网卡寄存器

输出:

[ 8.590881] nvethernet 2310000.ethernet: Adding to iommu group 52

[ 8.591175] nvethernet 2310000.ethernet: failed to read skip mac reset flag, default 0

[ 8.591389] nvethernet 2310000.ethernet: failed to read MDIO address

[ 8.591562] nvethernet 2310000.ethernet: Failed to read nvida,pause_frames, so setting to default support as disable

[ 8.591846] nvethernet 2310000.ethernet: setting to default DMA bit mask

[ 8.592031] nvethernet 2310000.ethernet: max-platform-mtu DT entry missing, setting default 1500

[ 8.592275] nvethernet 2310000.ethernet: missing nvidia,pad_auto_cal_pu_offset, setting default 0

[ 8.592503] nvethernet 2310000.ethernet: missing nvidia,pad_auto_cal_pd_offset, setting default 0

[ 8.601542] nvethernet 2310000.ethernet: Ethernet MAC address: 48:b0:2d:91:af:f3

[ 8.601969] nvethernet 2310000.ethernet: macsec param in DT is missing or disabled

[ 8.605935] nvethernet 2310000.ethernet: Macsec not supported/Not enabled in DT

[ 8.614176] nvethernet 2310000.ethernet: eth1 (HW ver: 53) created with 8 DMA channels

[ 15.839960] nvethernet 2310000.ethernet eth1: Link is Up - 1Gbps/Full - flow control off

如果出现上述”nvethernet 2310000.ethernet eth1: Link is Up - 1Gbps/Full - flow control off“表明千兆phy已经被识别。否则根据报错信息解决。

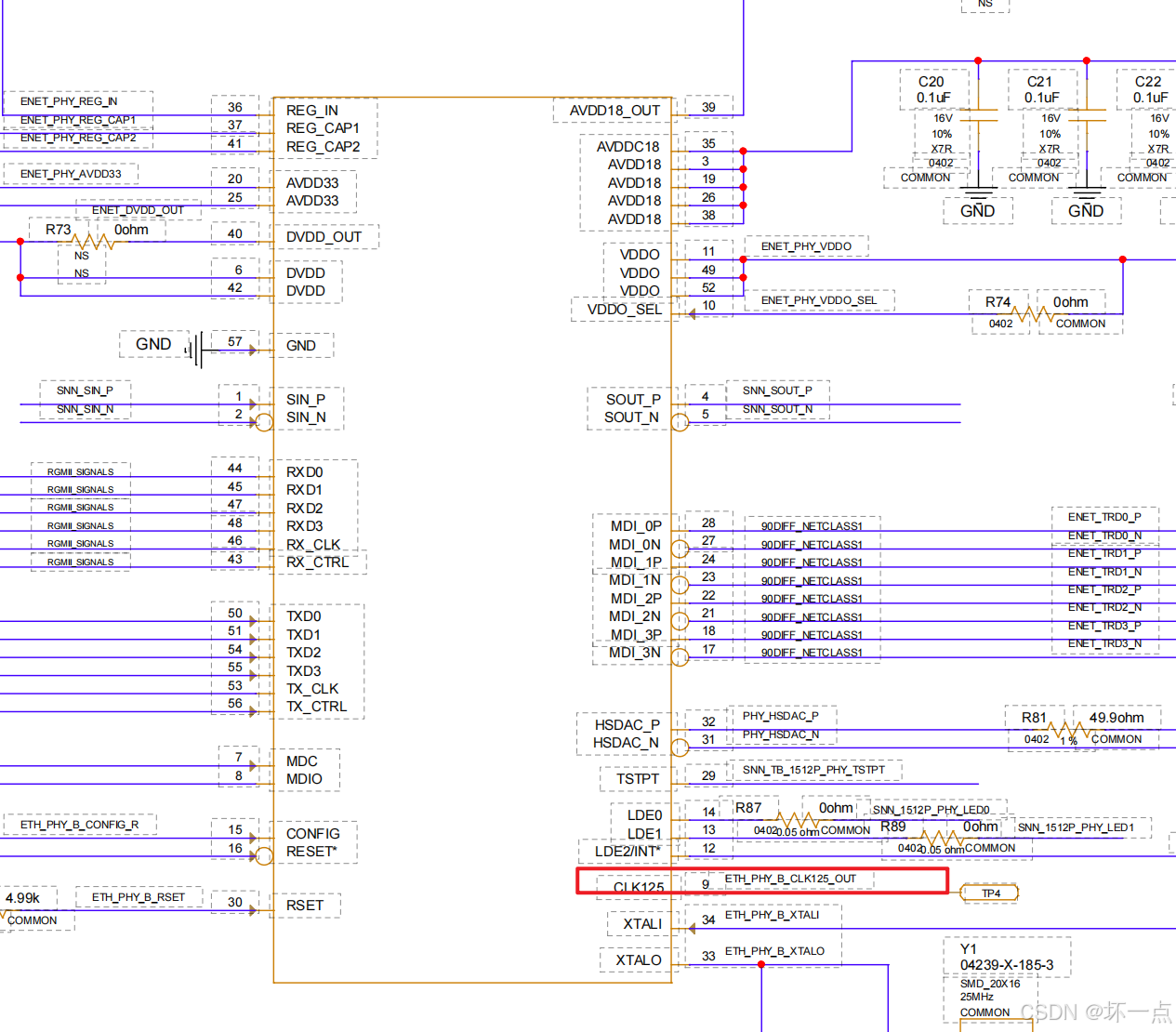

3.3 测量phy芯片参考时钟

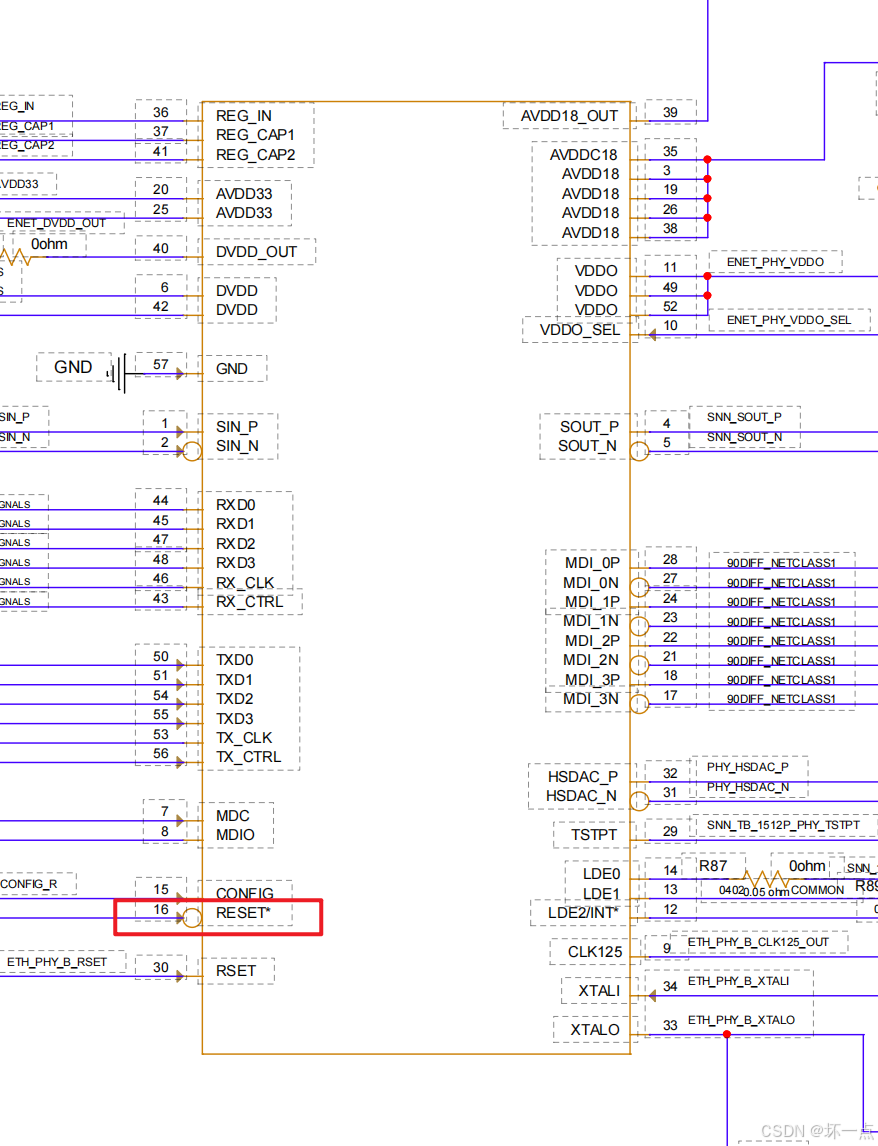

需要测试如图红色标记的CLK125引脚是否输出正常的124MHZ的波形,如果没有输出需要排查phy的配置和供电。

3.4 测量phy芯片的复位引脚

需要测试下图红色标记的RESET引脚,若phy芯片不复位,需要排查设备树配置和引脚功能配置。

3.5 MDIO存在代码

创建mdio.c文件

#include <stdio.h>

#include <netinet/in.h>

#include <stdlib.h>

#include <string.h>

#include <unistd.h>

#include <sys/ioctl.h>

#include <sys/socket.h>

#include <sys/types.h>

#include <linux/mii.h>

#include <linux/sockios.h>

#include <linux/types.h>

#include <net/if.h>

#define reteck(ret) \

if (ret < 0) { \

printf("%m! \"%s\" : line: %d\n", __func__, __LINE__); \

goto lab; \

}

#define help() \

printf("phyreg:\n"); \

printf("read operation: phyreg reg_addr\n"); \

printf("write operation: phyreg reg_addr value\n"); \

printf("For example:\n"); \

printf("phyreg eth0 1\n"); \

printf("phyreg eth0 0 0x12\n\n"); \

exit(0);

int sockfd;

int main(int argc, char *argv[])

{

struct mii_ioctl_data *mii = NULL;

struct ifreq ifr;

int ret;

if (argc == 1 || !strcmp(argv[1], "-h")) {

help();

}

memset(&ifr, 0, sizeof(ifr));

strncpy(ifr.ifr_name, argv[1], IFNAMSIZ - 1);

sockfd = socket(PF_LOCAL, SOCK_DGRAM, 0);

reteck(sockfd); // get phy address in smi bus

ret = ioctl(sockfd, SIOCGMIIPHY, &ifr);

reteck(ret);

mii = (struct mii_ioctl_data *)&ifr.ifr_data;

if (argc == 3) {

mii->reg_num = (uint16_t)strtoul(argv[2], NULL, 0);

ret = ioctl(sockfd, SIOCGMIIREG, &ifr);

reteck(ret);

printf("read phy addr: 0x%x reg: 0x%x value : 0x%x\n", mii->phy_id, mii->reg_num, mii->val_out);

} else if (argc == 4) {

mii->reg_num = (uint16_t)strtoul(argv[2], NULL, 0);

mii->val_in = (uint16_t)strtoul(argv[3], NULL, 0);

ret = ioctl(sockfd, SIOCSMIIREG, &ifr);

reteck(ret);

printf("write phy addr: 0x%x reg: 0x%x value : 0x%x\n", mii->phy_id, mii->reg_num, mii->val_in);

}

lab:

close(sockfd);

return 0;

}编译mdio.c文件有两种方式:

(1)在宿主机上交叉编译;

(2)直接在agx orin系统上编译。

编译完成后,使用方法如下:

读取寄存器:./mdio reg_addr

写入寄存器:./mdio reg_addr value

3.5 通过MDIO接口存在PHY芯片寄存器

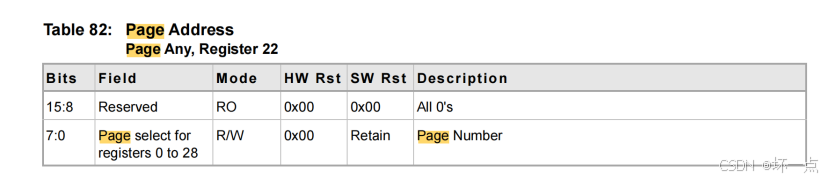

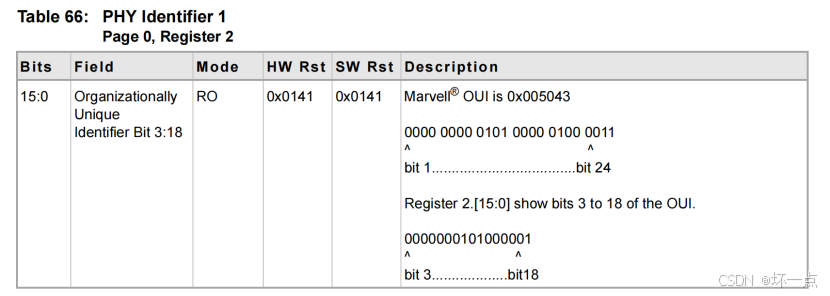

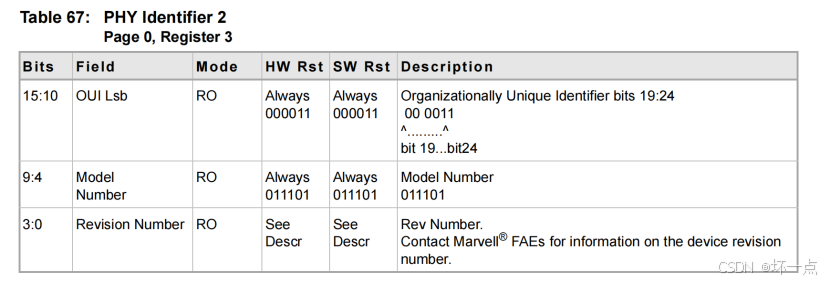

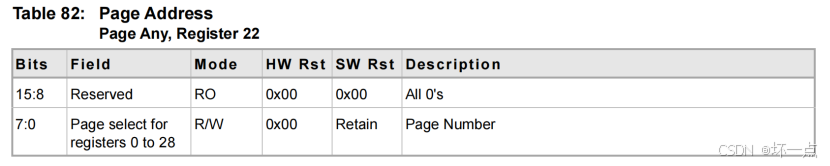

(1)阅读88E1512PB2-NNP2C000-U9.pdf手册,存在页寄存器切换情况。

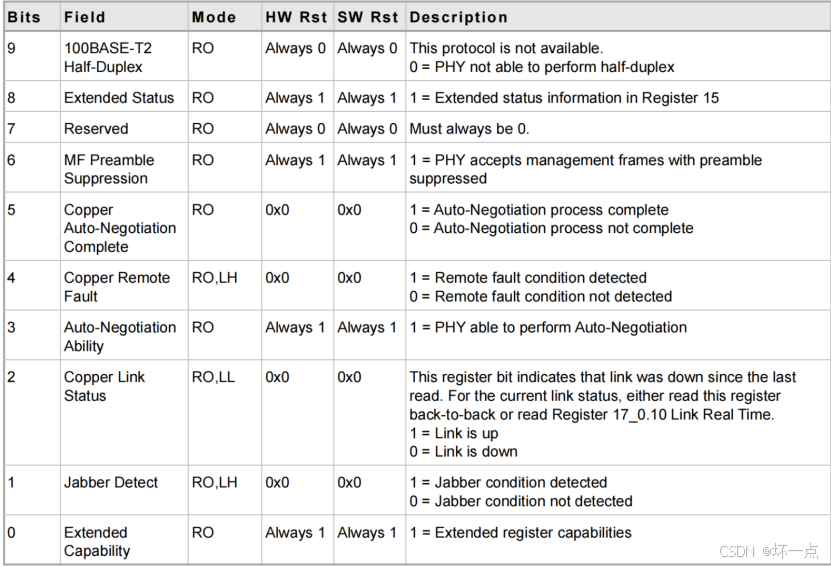

(2)默认是0页的寄存器,可以读取0页地址为1的phy寄存器值

(3)读取PHY的ID寄存器

执行:./mdio read eth1 1

返回:0x796d

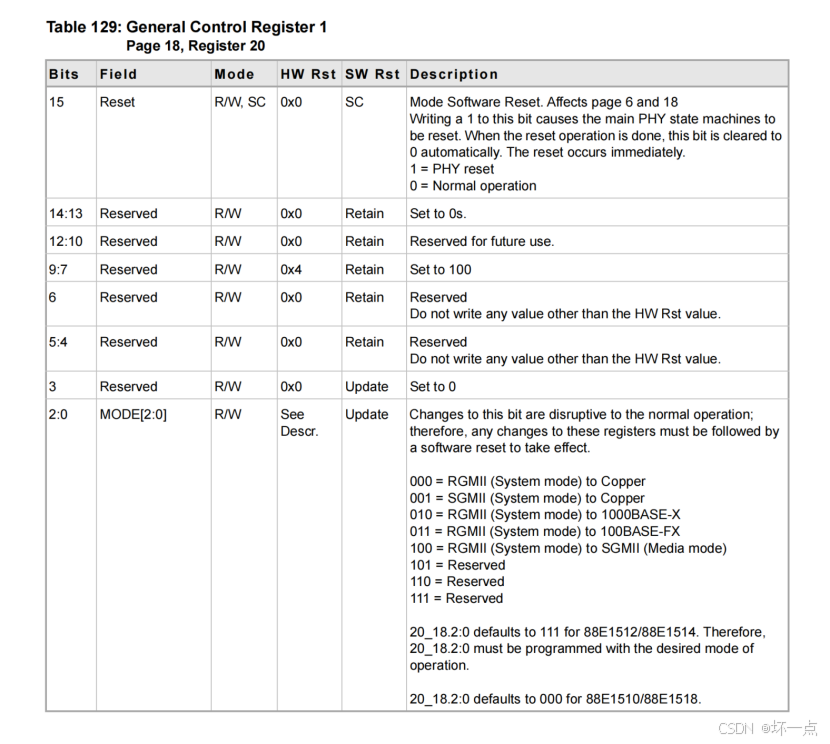

(4)切换页18读取20寄存器值

先写入页18

执行:./mdio write eth1 22 18

再执行:./mdio read eth1 18

四、总结调试方法

4.1、硬件层调试

| 手段 | 工具 / 方法 | 作用 |

|---|---|---|

| 链路状态检测 | 网线测试仪、LED 指示灯观察 | 验证物理链路连通性(如网线是否断路、PHY 的 Link/Activity 灯是否正常) |

| 信号质量分析 | 示波器、逻辑分析仪 | 检测 TX/RX 信号波形(如幅度、上升沿、时钟抖动),排查信号失真问题 |

| 电源测试 | 万用表、电源轨监控 | 测量 PHY 芯片各供电引脚电压(如 3.3V、1.8V),确保电源稳定 |

| 物理层环回 | PHY 寄存器配置环回模式(Loopback) | 验证 PHY 内部收发路径是否正常(无需对端设备,自环测试) |

4.2、寄存器级调试

| 手段 | 工具 / 方法 | 作用 |

|---|---|---|

| 基本寄存器读取 | MIIM/I2C 工具(如ethtool -g) | 读取 PHY 状态寄存器(如 BMSR、BMR),检查链路状态、自协商结果 |

| 扩展寄存器访问 | phytool、自定义驱动程序 | 访问 vendor-specific 寄存器(如 Marvell、Broadcom 的私有寄存器) |

| 寄存器日志记录 | 抓包分析寄存器配置时序 | 验证驱动程序对 PHY 的配置流程是否正确(如自协商参数设置顺序) |

4.3、软件层调试

| 手段 | 工具 / 方法 | 作用 |

|---|---|---|

| 内核日志分析 | dmesg、syslog | 查看驱动加载过程(如 PHY 探测、自协商结果),定位初始化失败原因 |

| ethtool 工具 | ethtool ethX | 查询 PHY 状态(ethtool -s修改配置)、自协商参数、错误计数器(如 CRC 错误) |

| 网络抓包 | tcpdump、Wireshark | 分析数据包收发情况(如丢包率、错包率),验证数据通路是否正常 |

| 驱动调试 | 内核调试选项(如CONFIG_PHY_DEBUG) | 启用驱动详细日志,跟踪 PHY 状态机转换(如链路 up/down 事件) |

4.4、高级调试技术

| 手段 | 工具 / 方法 | 作用 |

|---|---|---|

| 硬件断点 | JTAG/SWD 调试器 | 在 PHY 芯片初始化流程中设置断点,检查关键寄存器值 |

| 功耗分析 | 功率计、电流探针 | 监控 PHY 工作功耗,排查异常耗电问题(如芯片锁死导致的高功耗) |

| 温度测试 | 红外热成像仪、热敏贴纸 | 检测 PHY 芯片工作温度,避免因过热导致性能下降或丢包 |

| 应力测试 | 网络流量发生器(如 Ixia、Spirent) | 在高负载下验证 PHY 稳定性(如 100% 线速转发时的丢包率) |

4.5、 网络分析仪调试

网络分析仪(如 Keysight E5071C、R&S ZNB 系列)在 PHY 芯片调试中主要用于测试高频信号特性和验证物理层性能。以下是其具体应用场景、操作步骤及注意事项:

| 测试项目 | 作用 |

|---|---|

| S 参数测试 | 测量信号反射(回波损耗)和传输特性(插入损耗),评估阻抗匹配和信号完整性 |

| 眼图分析 | 评估高速信号质量(如抖动、噪声容限),验证是否满足 IEEE 标准 |

| 误码率测试(BERT) | 在不同速率和编码下测试误码率,确定 PHY 的极限性能 |

| 频响特性测试 | 分析信号带宽、截止频率和群延迟,优化传输介质匹配 |

| 电磁干扰(EMI)分析 | 检测信号辐射和串扰,优化 PCB 布线和屏蔽设计 |

4.6、 常见问题排查流程

-

物理层验证:

- 检查网线连接、LED 状态

- 使用示波器观察信号质量

- 配置 PHY 环回模式测试

-

自协商问题定位:

- 通过

ethtool查看自协商状态 - 强制 PHY 工作在固定速率 / 双工模式(

ethtool -s ethX speed 1000 duplex full) - 检查对端设备配置是否匹配

- 通过

-

数据通路验证:

- 使用

ping测试连通性 - 通过

iperf测试吞吐量 - 抓包分析丢包位置(PHY 前 / 后)

- 使用

-

驱动与固件调试:

- 检查内核驱动版本兼容性

- 更新 PHY 固件(如有)

- 对比参考设计的寄存器配置值

4.7、注意事项

- 硬件依赖:不同 PHY 芯片的寄存器映射和调试接口(如 MIIM/I2C)可能不同,需参考芯片手册

- 电源敏感性:PHY 对电源噪声敏感,建议使用低噪声 LDO 供电

- 散热考量:高速 PHY(如 10Gbps)需注意散热设计,避免温度影响信号质量

1161

1161

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?