一、0.1mm 薄介质的技术特性与挑战

0.1mm(100μm)薄介质在高密度 PCB(如 5G 模块、AI 芯片载板)中广泛应用,其核心特性为:

-

物理特性

-

介质厚度公差敏感:±10% 公差即 ±0.01mm,导致阻抗偏差可达 ±8Ω(远大于常规介质的 ±5Ω);

-

铜箔与介质结合力要求高:薄介质易因铜箔张力产生翘曲,影响阻抗稳定性;

-

加工难度大:钻孔易导致介质破损,蚀刻线宽精度难控制(±0.01mm 误差对阻抗影响显著)。

-

-

电磁场特性

薄介质中,传输线与参考平面距离近,电磁场集中在介质层内,导致:-

耦合增强:差分线间距稍小即会过度耦合,使差分阻抗低于目标值;

-

边缘效应显著:线宽微小变化(如 0.01mm)会导致阻抗大幅波动(可达 5Ω);

-

寄生电容增大:薄介质导致线间电容 C 增加,使阻抗 Z=√(L/C) 降低。

-

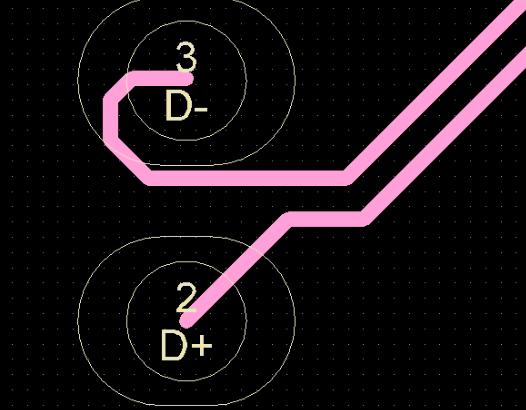

二、90Ω 差分设计的核心禁区界定

基于仿真与实测数据,0.1mm 薄介质下 90Ω 差分的设计禁区主要集中在以下四个维度:

(一)线宽 / 间距禁区

-

线宽过窄(<0.12mm)

-

问题:线宽<0.12mm 时,制造公差(±0.01mm)导致线宽实际波动范围达 16.7%,阻抗偏差超过 ±10Ω(90Ω 目标变为 80-100Ω);

-

原理:线宽减小使导体横截面积降低,电阻增大,同时电磁场更集中,边缘效应加剧阻抗波动。

-

-

间距过小(<0.15mm)

-

问题:间距<0.15mm 时,差分对耦合过强,差分阻抗降至 80Ω 以下(如间距 0.12mm 时,仿真阻抗仅 78Ω);

-

原理:间距减小使线间互容 C12 增大,差分阻抗公式 Zdiff= (Z01 + Z02 - 2Z12) 中,耦合阻抗 Z12 增大,导致 Zdiff 降低。

-

-

线宽 / 间距比失衡(W/S>1.2)

-

问题:当 W=0.18mm、S=0.15mm(W/S=1.2)时,阻抗稳定在 90Ω;若 W=0.20mm、S=0.15mm(W/S=1.33),阻抗降至 85Ω,且容性耦合占比超过 60%,导致信号时延增加。

-

(二)过孔设计禁区

-

过孔直径>0.2mm

-

问题:0.1mm 薄介质中,过孔直径>0.2mm 会导致反焊盘直径需>0.4mm(通常为孔径的 2 倍),破坏参考平面完整性,使过孔处阻抗突变达 20Ω(从 90Ω 跳至 110Ω);

-

验证:仿真显示 0.25mm 孔径过孔的 TDR 曲线在过孔处有明显尖峰,反射系数 S11>-10dB(反射功率>10%)。

-

-

过孔残桩>0.1mm

-

问题:残桩长度>0.1mm 时,相当于在传输线中串联电感(每 0.1mm 残桩约 0.5nH),高频下(10GHz)感抗 X_L=2πfL≈31.4Ω,导致阻抗突变超过 15Ω;

-

实测:0.15mm 残桩在 10GHz 时,过孔处阻抗从 90Ω 升至 106Ω,信号眼图张开度降低 20%。

-

(三)布局禁区

-

跨介质层过渡

-

问题:从 0.1mm 薄介质层过渡到 0.2mm 厚介质层时,若未做阻抗补偿,阻抗会从 90Ω 突变为 105Ω,反射系数 S11=-8dB(反射功率 15%);

-

原理:介质厚度增加导致特性阻抗升高,且过渡处电磁场分布突变,产生不连续反射。

-

-

紧邻大面积铜皮

-

问题:差分线与大面积铜皮(如电源平面)距离<0.3mm 时,会引入额外容性耦合,使阻抗降低 5-8Ω(如从 90Ω 变为 83Ω);

-

仿真:铜皮距离 0.2mm 时,线间电容增加 0.05pF/mm,导致阻抗降低 7Ω。

-

(四)材料与工艺禁区

-

基材 εr 波动>±0.2

-

问题:0.1mm 薄介质对介电常数敏感,εr 从 4.2 变为 4.4(波动 0.2)时,阻抗从 90Ω 降至 85Ω,超出 ±5% 公差范围;

-

数据:εr 每变化 0.1,阻抗变化约 2.5Ω,需严格控制基材批次一致性。

-

-

铜箔粗糙度>0.5μm

-

问题:粗化铜箔(粗糙度>0.5μm)会增加高频下的趋肤效应损耗,同时改变电磁场分布,使阻抗测量值比仿真值高 6-8Ω(仿真 90Ω,实测 97Ω);

-

原理:粗糙表面导致电流路径变长,等效电阻增大,阻抗升高。

-

三、禁区规避的工程实现方案

-

线宽 / 间距优化

-

推荐参数:线宽 0.15-0.18mm,间距 0.18-0.2mm(W/S=0.8-1.0),仿真验证阻抗 90±3Ω;

-

公差控制:要求 PCB 厂线宽公差 ±0.005mm,间距公差 ±0.01mm,需提供 CPK≥1.33 的制程能力报告。

-

-

过孔结构改进

-

采用微型过孔:孔径 0.15-0.2mm,反焊盘 0.3-0.35mm,减少参考平面破坏;

-

全背钻工艺:残桩长度控制在 0.05mm 以下,仿真显示阻抗突变≤5Ω,S11≤-15dB(反射功率≤3%)。

-

-

布局补偿设计

-

介质层过渡处:在厚介质侧减小线宽 0.02-0.03mm(如从 0.16mm 减至 0.13mm),补偿阻抗升高;

-

铜皮隔离:差分线与大面积铜皮间预留≥0.3mm 隔离带,或增加接地过孔(间距 0.5mm)屏蔽耦合。

-

-

材料与工艺控制

-

基材选型:选用低波动 εr 的薄介质(如罗杰斯 RO4350,εr=3.48±0.05),并要求厂商提供每批次测试报告;

-

铜箔选择:采用低粗糙度铜箔(≤0.3μm),如压延铜(RA=0.2μm),减少趋肤效应影响。

-

624

624

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?