在高速PCB设计中,布局决定了80%的成功率。一个优秀的布局能避开信号干扰、散热失控、生产隐患三大陷阱。本文结合工程实践,拆解高速PCB布局的核心法则。

先画地图,再建城市—

功能分区是布局的第一步。工程师需要像城市规划师一样划分功能区块:

-

数字区(如CPU、内存)集中放置,避免高频噪声干扰模拟电路。

-

模拟区(如传感器、ADC)靠近板边,缩短信号采集路径。

-

大功率区(如电源模块、电机驱动)独立布局,周围预留散热空间。

格点系统让元件整齐排列:

-

大芯片(如FPGA)用50mil格点对齐引脚

-

小电阻电容用25mil格点精细定位

这种设计让贴片机生产效率提升30%。

电磁环境的“地基”—

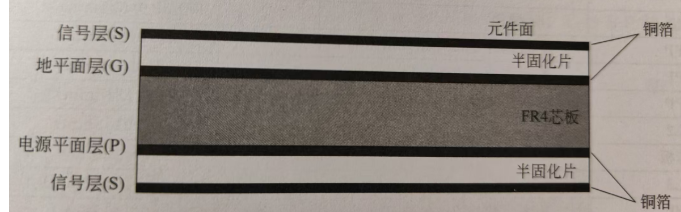

四层板经典方案S-G-P-S(信号-地-电源-信号)是性价比之选:

-

地层作为电磁屏蔽层,隔离顶层和底层的信号干扰

-

电源层与地层紧密耦合,形成天然的去耦电容

六层板升级方案更抗干扰:信号/地/高速信号/电源/地/信号。两个地平面夹住高速信号层,串扰降低50%。

对称叠层是防变形的关键:

-

芯板与半固化片对称分布

-

铜厚分布上下平衡

某服务器主板因叠层不对称,回流焊后变形0.3mm导致BGA虚焊。对称设计后良率提升至99.9%。

噪声控制的胜负手—

电源布局要遵循“三近原则”:

-

去耦电容靠近IC电源引脚(<3mm)

-

大电容靠近电源输入端

-

电源模块靠近耗电芯片

地平面必须完整连续:

-

避免分割地平面,防止高频信号绕远路

-

数字地与模拟地单点连接

某射频模块因分割地平面产生天线效应,辐射超标15dB。改用完整地平面后通过EMC认证。

给高速线系上“安全带”—

3W原则是防串扰的底线:

-

线间距≥3倍线宽(0.2mm线宽需0.6mm间距)

-

关键信号(如时钟线)加地线护围

高速信号走带状线层:

-

将DDR4等高速信号布在内层(如六层板的L3)

-

上下用地平面屏蔽

某摄像头模组将MIPI线改到内层,眼图抖动改善40%。

特殊电路布局技巧—

BGA芯片的“同心圆法则”:

-

第一圈(0-3mm):放置0402尺寸去耦电容

-

第二圈(3-5mm):配置端接电阻

-

第三圈(>5mm):摆放接口电路

DC-DC电路的散热设计:

-

电感与MOSFET呈L形排列,避免热量叠加

-

底层铺散热铜箔+过孔阵列(孔径0.3mm/间距1mm)

某工业电源模块采用该布局,满载温度下降28℃。

高速PCB布局如同在方寸间编排一场交响乐——功能分区是乐章的章节划分,叠层设计是舞台的声学结构,电源布线是乐器的调音校准。当BGA芯片下的电容如定音鼓般精准排布,当地平面如低音提琴般沉稳托底,那些在GHz频率上起舞的信号线,才能奏出无杂音的纯净乐章。而最终通过EMC测试的静默时刻,正是对布局艺术家最隆重的喝彩。

624

624

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?