四层PCB的电源接口设计直接决定了系统的稳定性和EMI性能。合理的电源接口设计可使电源噪声降低40%,同时提升20%的能源效率。

一、四层板电源接口设计三大原则

-

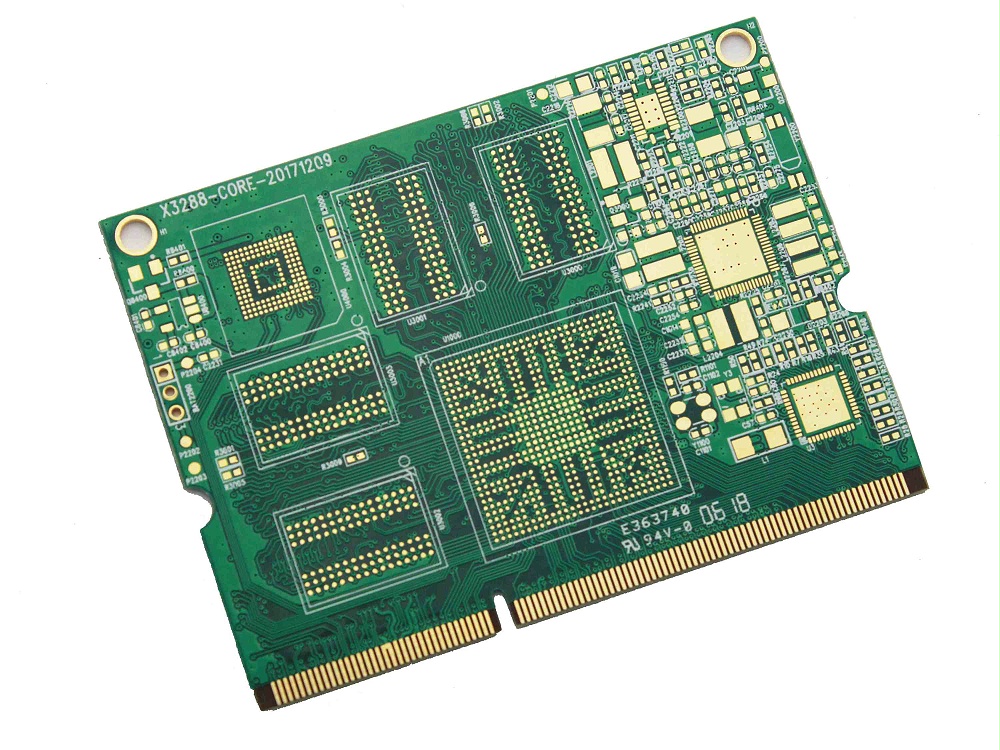

紧耦合电源地层架构

电源层与地层必须采用3-4mil间距的紧耦合结构,形成天然的去耦电容。实测数据显示,3mil间距的电源-地平面组合,在100MHz频段可提供75pF/cm²的等效电容,比常规6mil间距方案滤波效率提升3倍。多级去耦网络构建

在电源入口处设置三级去耦体系:-

10μF钽电容(处理1-10MHz低频噪声)

-

100nF陶瓷电容(抑制10-100MHz中频干扰)

-

1nF高频MLCC(滤除100MHz以上噪声)

-

-

星型拓扑供电模式

核心芯片供电采用放射状布线,从电源入口直接引出独立分支。在FPGA供电案例中,该方式使电流路径缩短35%,压降减少至0.05V。

二、电源接口核心设计要点

1. 电源层分割策略

-

智能分割技术

采用“主通道保留+边缘蜂窝化”的分割方案:-

核心供电区域保留80%以上完整平面

-

辅助电源区采用线宽8mil/间距50mil的蜂窝结构

该方案在DDR4供电系统中,使不同电压域的串扰降低至-50dB以下。

-

-

分割线优化原则

使用20mil宽度的渐变齿状分割线,边缘倒角半径≥50μm。在12V/5V混合供电场景下,该设计使跨分割区阻抗波动控制在±5%。

2. 过孔阵列配置规范

-

电源过孔采用0.3mm孔径+0.6mm焊盘的双排阵列

-

每安培电流配置3个过孔

-

相邻过孔中心距≥2倍孔径,防止铜箔撕裂

3. 去耦电容布局法则

-

空间分布

高频MLCC距芯片引脚≤2mm,中频电容布置在3-5mm区域,低频电容置于电源入口5cm范围内。 -

焊盘优化

0402封装电容采用椭圆形焊盘(0.6×0.3mm),使ESL降低至0.2nH。在PCIe接口供电中,该设计使信号完整性提升25%。

三、常见设计误区与解决方案

-

电源分割过碎导致谐振

某5G基站案例中,过度分割引发60MHz谐振峰超标12dB。改进方案:保留核心区完整平面,边缘采用渐变蜂窝结构。 -

去耦电容布局失当

高频MLCC距离芯片超过5mm,导致100MHz以上噪声滤除失效。优化方案:采用倒装焊工艺将电容嵌入封装底部。 -

过孔数量不足引发热失效

3A电源仅配置6个过孔,实测温升达45℃。修正方案:按每安培3孔标准配置,并采用双排交错布局。

97

97

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?