PCB层压结构的堆叠顺序直接决定电磁干扰(EMI)的控制水平。

一、层压结构设计的三大核心原则

-

信号-地相邻准则

高速信号层必须紧邻完整地平面,可将微带线辐射强度降低40%。对于28Gbps以上差分信号,建议采用对称双地平面夹层结构(如S-G-S-G),使插入损耗波动控制在±0.2dB以内。 -

电源-地耦合法则

电源层与地平面间隔应≤4mil,利用层间电容形成天然滤波器。实测数据显示,3mil间距的电源层可吸收70%的共模噪声,比常规6mil间距方案效率提升3倍。 -

跨层信号管控

禁止高速信号跨越分割区域,必要时采用地缝合孔阵列。在56G PAM4系统中,每毫米信号线需配置2个0.2mm接地过孔,可将串扰抑制在-50dB以下。

二、典型层压结构EMI性能对比

1. 四层板最优方案

-

S-G-P-S结构

外层地平面提供天然屏蔽,中间层电源与地层形成3.5pF/cm²耦合电容。在2.4GHz频段辐射值比传统G-S-P-G结构低8dB,但布线密度下降25%。 -

改进型G-S-S-G结构

增加内层铜填充率至85%,使10Gbps信号的回流路径阻抗从120Ω降至35Ω。需注意避免第2/3层平行走线,交叉角度应≥30°。

2. 六层板黄金比例

-

S-G-S-P-G-S布局

第3/4层电源地紧耦合,关键信号分布在1/6层。实测56Gbps信号在此结构下,眼图高度提升28%,同时将谐振峰频率推高至12GHz以上。 -

地平面分割技术

对多电压系统采用智能分割:-

核心电源区域保留完整平面(≥80%面积)

-

辅助电源采用蜂窝状网格

该方法可使电源完整性PSRR指标提升15dB。

-

3. 八层及以上高阶设计

-

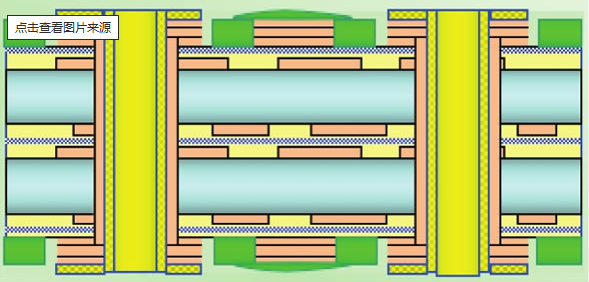

S-G-S-P-G-S-G-S堆叠

每两个信号层间插入地平面,特别适合112G Serdes设计。需控制相邻信号层走线方向正交,交叉角度容差≤5°。 -

3D屏蔽舱结构

在FPGA和DDR4区域局部增加垂直互联地墙,采用0.15mm激光钻孔形成全包围屏蔽。实测显示该方法可将辐射热点强度降低18dBμV/m。

优秀的层压设计需要平衡信号完整性、制造成本和EMI性能。随着224Gbps光模块等新技术的普及,基于机器学习的动态层压优化将成为下一代PCB设计的核心技术突破点。

175

175

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?