“PCB上焊盘尺寸差不多的连接器,为什么SI工程师给的阻抗优化方案完全不同?他们是不是在故弄玄虚?”真相往往藏在你看不到的地方——连接器的3D管脚结构才是关键。

一、案例:两种连接器,阻抗差4Ω意味着什么?

某高速板卡上同时使用了16Gbps和25Gbps连接器,PCB焊盘尺寸几乎一致,但SI仿真结果却让人大跌眼镜:

• 25G连接器:反焊盘挖空第2-3层,参考第4层GND,阻抗稳定在93.9Ω。

• 16G连接器:同样方案下阻抗仅89.7Ω,相差4.2Ω。

这意味着什么? 在5Gbps信号中,4Ω的阻抗偏差会导致信号反射超过15%,直接引发眼图闭合、误码率飙升。

二、阻抗差异的元凶:3D管脚结构

1. 焊盘背后的“隐藏参数”

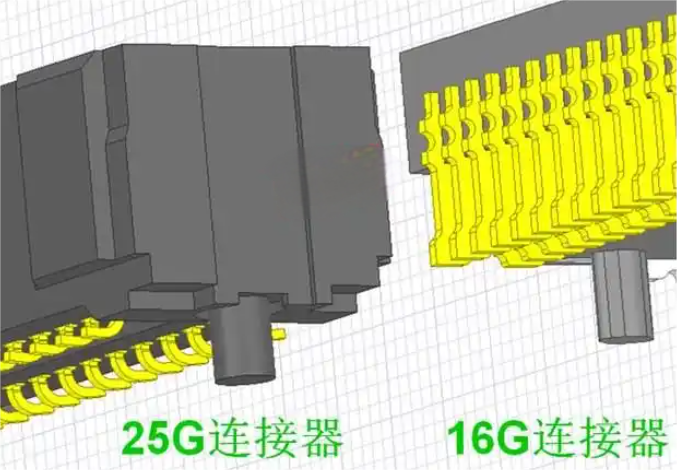

PCB设计软件显示的焊盘只是二维投影,实际连接器的管脚结构差异巨大:

• 25G连接器:管脚细长(类似“三寸金莲”),铜厚薄,与参考平面距离近。

• 16G连接器:管脚粗短(堪称“大脚怪”),铜厚更厚,内部填充更多塑胶。

三、常规优化为何失效?

1. 反焊盘挖空:治标不治本

• 16G连接器:反焊盘加宽5mil,阻抗仅提升0.4Ω(89.7→90.1Ω)。

• 根本原因:管脚本身过粗,反焊盘调整对整体阻抗影响有限。

2. 多层挖空:牺牲层间完整性

强行挖空第4-5层参考第6层GND,阻抗仅提升0.6Ω,却导致:

• 信号回流路径变长:增加环路电感。

• 层间应力集中:可能引发PCB分层。

四、破局方案:从“改板”到“改结构”

1. 管脚尺寸优化(设计源头)

• 内缩管脚:将16G连接器管脚侧壁内缩5mil,等效宽度从20mil降至15mil。

• 效果:阻抗直接提升至93.5Ω,与25G连接器持平,无需复杂挖空。

2. 参考平面协同设计

• 精准匹配间距:根据管脚宽度设定h值(如15mil宽管脚对应h=10mil)。

• 避免过度挖空:优先调整管脚而非牺牲层间结构。

五、设计避坑指南

1. 必查三维模型

• 要求SI提供管脚3D数据:包括截面尺寸、倒角、镀层厚度。

• 仿真前验证:用T型结构模拟实际管脚阻抗,修正理论参数。

2. 参数化设计流程

步骤操作要点工具示例1导入连接器3D模型Altium/Cadence 3D Viewer2提取管脚等效电路Ansys HFSS3生成阻抗-结构映射表HyperLynx SI

3. 高速场景选型原则

• 25G+信号:选细管脚、低h值连接器。

• 16G信号:选宽管脚、高h值连接器。

635

635

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?