PCB 设计在制造前涉及布局与布线两方面,关乎电路性能与稳定性,分享一些PCB打样设计的关键要点。

一、布局规则

- 优先布局原则:遵循 “先大后小,先难后易”,重要单元电路、核心元器件优先布局,且参考原理框图依主信号流向安排主要元器件。

- 调试维修便利:小元件周边勿放大元件,需调试器件周围留足空间,方便操作。

- 对称与美观:相同结构电路尽量采用 “对称式” 布局,整体按均匀分布、重心平衡、版面美观标准优化。

- 元件放置方向:同类型插装元器件及有极性分立元件在 X 或 Y 方向保持一致,利生产检验。

- 发热与敏感元件:发热元件均匀分布助散热,温度敏感器件(除温度检测元件)远离发热量大的元器件。

- 连线及信号分离:布局要使总连线短,关键信号线更短,且高电压大电流与小电流低电压信号、模拟与数字信号、高频与低频信号分开,高频元器件间隔充分。

- 去偶电容布局:去偶电容靠近 IC 电源管脚,与电源和地回路最短。

- 电源器件分组:使用同一种电源的器件尽量放一起,便于电源分隔。

二、布线规则

(一)布线优先次序

- 关键信号优先:模拟小信号、高速信号等关键信号优先布线。

- 密度优先:从连接关系复杂、连线密集区域着手布线。同时,为关键信号提供专门布线层,保证最小回路面积,必要时手工优先布线、屏蔽等;避免在电源层和地层之间布置敏感信号;有阻抗控制要求的按规定布线。

(二)具体走线方式

- 时钟布线:时钟线对 EMC 影响大,少打过孔,避免与其他信号线并行走线、靠近电源部分,时钟发生芯片及晶振下方铺铜隔离。

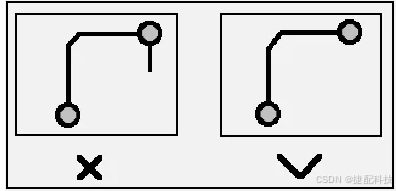

- 直角走线:应尽量避免,因其会使线宽变化、阻抗不连续,影响信号传输,体现在产生容性负载、信号反射及 EMI 等方面。

- 差分走线:应用广泛,优势明显,如抗干扰能力强、能抑制 EMI、时序定位精确等,布线要求 “等长、等距、尽量靠近”。

- 蛇形线:用于调节延时,但会破坏信号质量,实际设计中为满足时序要求必要时才使用,成对差分信号线等应注意相关要求。

(三)常用布线规则

包括走线方向控制、开环检查、阻抗匹配检查、长度控制、倒角、器件去藕、布局分区 / 分层、地线回路、电源与地线层完整性、3W 规则、屏蔽保护、走线终结网络、闭环检查、分枝长度控制、谐振、孤立铜区控制、重叠电源与地线层、20H 规则等,各规则从不同角度保障布线质量与电路性能。

三、其他要点

单双层板电源线应粗短,依电流计算宽度,电源和地构成环路尽量小,进入器件前先对电源去藕且独立去藕,布线中保持接地良好。

总之,PCB 设计需综合考虑布局与布线各规则要点,精心设计才能确保电路良好性能与稳定运行。

536

536

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?