1. OV7725摄像头

1.1 简介

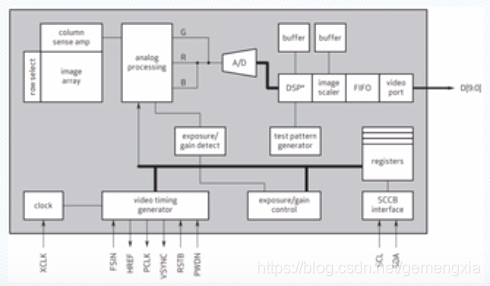

OV7725是OmniVision(豪威科技)公司生产的CMOS图像传感器,该传感器功耗低、可靠性高一级采集速率快,主要应用在玩具、安防监控、电脑多媒体等领域。

OV7725感光阵列达到640*480,功能最快60fps VGA分辨率的图像采集。传感器内部集成了图像处理的功能,包括自动曝光控制(AEC)、自动增益控制(AGC)和自动白平衡(AWB)等。

1.2 SCCB接口

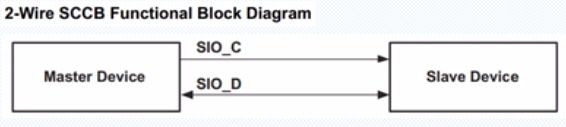

SCCB(Serial Camera Control Bus,串行摄像头控制总线)是由OV公司定义和发展的三线式串行总线。

该总线控制着OV系列摄像头的大部分功能,包括图像数据格式、分辨率以及图像处理参数等。

OV公司为了减少传感器引脚的封装,现在SCCB总线大多采用两线式接口总线。(类似IIC总线)

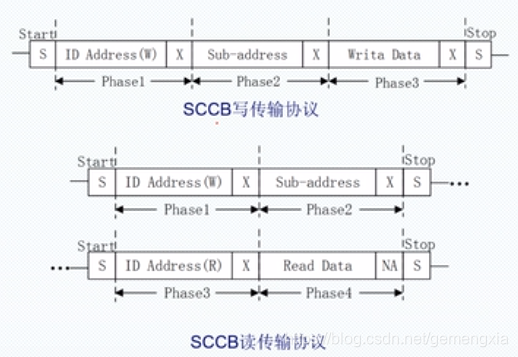

SCCB与IIC的差异

1、SCCB传输协议中,第9位为不必关心位,而IIC写传输协议为应答位。

2、SCCB每次传输过程不超过3个阶段(Phase),即不能连续读写。

3、SCCB读传输协议中没有重复开始的概念,在写完寄存器地址后,发起停止信号。

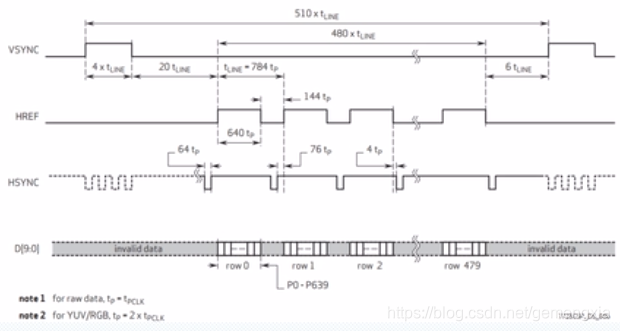

1.3 图像输出时序

OV7725支持多种不同分辨率图像的输出,包括VGA(640x480)、QVGA(320x240)、以及CIF(一种常用的标准化图像格式,分辨率为352x288)到40x30之间的任意尺寸。

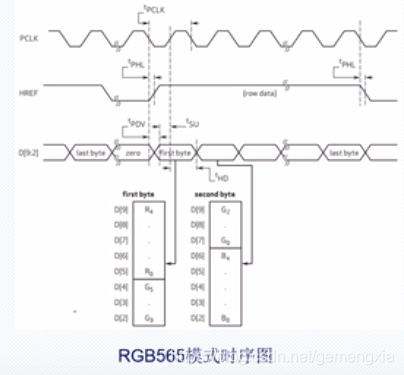

OV7725支持多种不同的数据像素格式,包括YUV(亮度参数和色度参数量分开表示的像素格式)、RGB(其中RGB格式包括RGB565、RGB555)以及8位的RAW(原始图像数据)和10位的RAW。

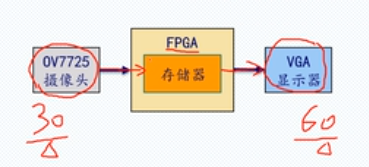

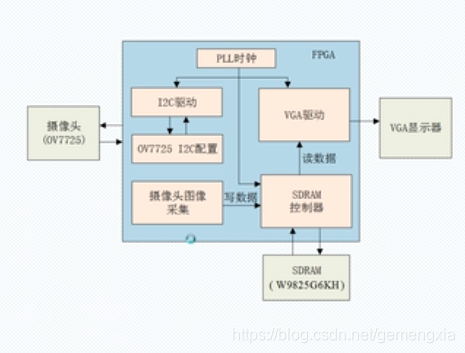

2. 程序设计

使用FPGA开发板及OV7725摄像头实现图像采集,并通过VGA显示器显示,以及RGBLCD液晶屏(800*480)实时显示。

2.1 系统框图

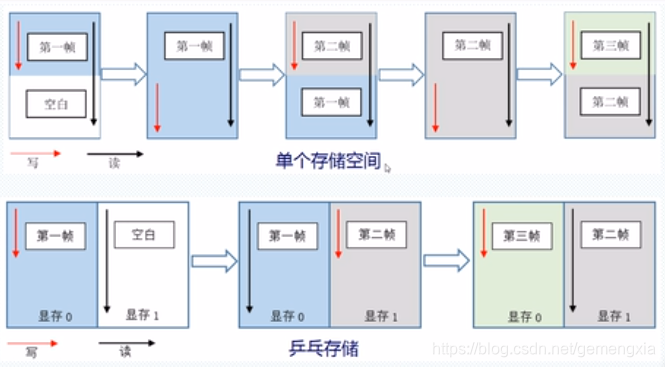

2.2 SDRAM乒乓存储

2.3 源码

module ov7725_rgb565_640x480_vga(

input sys_clk , //系统时钟

input sys_rst_n , //系统复位,低电平有效

//摄像头接口

input cam_pclk , //cmos 数据像素时钟

input cam_vsync , //cmos 场同步信号

input cam_href , //cmos 行同步信号

input [7:0] cam_data , //cmos 数据

output cam_rst_n , //cmos 复位信号,低电平有效

output cam_sgm_ctrl, //cmos 时钟选择信号, 1:使用摄像头自带的晶振

output cam_scl , //cmos SCCB_SCL线

inout cam_sda , //cmos SCCB_SDA线

//SDRAM接口

output sdram_clk , //SDRAM 时钟

output sdram_cke , //SDRAM 时钟有效

output sdram_cs_n , //SDRAM 片选

output sdram_ras_n , //SDRAM 行有效

output sdram_cas_n , //SDRAM 列有效

output sdram_we_n , //SDRAM 写有效

output [1:0] sdram_ba , //SDRAM Bank地址

output [1:0] sdram_dqm , //SDRAM 数据掩码

output [12:0] sdram_addr , //SDRAM 地址

inout [15:0] sdram_data , //SDRAM 数据

//VGA接口

output vga_hs , //行同步信号

output vga_vs , //场同步信号

output [15:0] vga_rgb //红绿蓝三原色输出

);

//parameter define

parameter SLAVE_ADDR = 7'h21 ; //OV7725的器件地址7'h21

parameter BIT_CTRL = 1'b0 ; //OV7725的字节地址为8位 0:8位 1:16位

parameter CLK_FREQ = 26'd25_000_000; //i2c_dri模块的驱动时钟频率 25MHz

parameter I2C_FREQ = 18'd250_000 ; //I2C的SCL时钟频率,不超过400KHz

parameter CMOS_H_PIXEL = 24'd640 ; //CMOS水平方向像素个数,用于设置SDRAM缓存大小

parameter CMOS_V_PIXEL = 24'd480 ; //CMOS垂直方向像素个数,用于设置SDRAM缓存大小

//wire define

wire clk_100m ; //100mhz时钟,SDRAM操作时钟

wire clk_100m_shift ; //100mhz时钟,SDRAM相位偏移时钟

wire clk_25m ; //25mhz时钟,提供给vga驱动时钟

wire locked ;

wire rst_n ;

wire i2c_exec ; //I2C触发执行信号

wire [15:0] i2c_data ; //I2C要配置的地址与数据(高8位地址,低8位数据)

wire cam_init_done ; //摄像头初始化完成

wire i2c_done ; //I2C寄存器配置完成信号

wire i2c_dri_clk ; //I2C操作时钟

wire wr_en ; //sdram_ctrl模块写使能

wire [15:0] wr_data ; //sdram_ctrl模块写数据

wire rd_en ; //sdram_ctrl模块读使能

wire [15:0] rd_data ; //sdram_ctrl模块读数据

wire sdram_init_done ; //SDRAM初始化完成

wire sys_init_done ; //系统初始化完成(sdram初始化+摄像头初始化)

//*****************************************************

//** main code

//*****************************************************

assign rst_n = sys_rst_n & locked;

//系统初始化完成:SDRAM和摄像头都初始化完成

//避免了在SDRAM初始化过程中向里面写入数据

assign sys_init_done = sdram_init_done & cam_init_done;

//不对摄像头硬件复位,固定高电平

assign cam_rst_n = 1'b1;

//cmos 时钟选择信号,0:使用引脚XCLK提供的时钟 1:使用摄像头自带的晶振

assign cam_sgm_ctrl = 1'b1;

//锁相环

pll_clk u_pll_clk(

.areset (~sys_rst_n),

.inclk0 (sys_clk),

.c0 (clk_100m),

.c1 (clk_100m_shift),

.c2 (clk_25m),

.locked (locked)

);

//I2C配置模块

i2c_ov7725_rgb565_cfg u_i2c_cfg(

.clk (i2c_dri_clk),

.rst_n (rst_n),

.i2c_done (i2c_done),

.i2c_exec (i2c_exec),

.i2c_data (i2c_data),

.init_done (cam_init_done)

);

//I2C驱动模块

i2c_dri

#(

.SLAVE_ADDR (SLAVE_ADDR),

.CLK_FREQ (CLK_FREQ ),

.I2C_FREQ (I2C_FREQ )

)

u_i2c_dri(

.clk (clk_25m ),

.rst_n (rst_n ),

.i2c_exec (i2c_exec ),

.bit_ctrl (BIT_CTRL ),

.i2c_rh_wl (1'b0), //固定为0,只用到了IIC驱动的写操作

.i2c_addr (i2c_data[15:8]),

.i2c_data_w (i2c_data[7:0]),

.i2c_data_r (),

.i2c_done (i2c_done ),

.scl (cam_scl ),

.sda

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1313

1313

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?