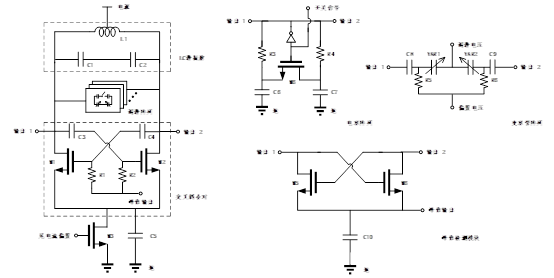

1、确定L的原则:根据需要的输出幅度,以及电流要求,按照Vout=R*I计算L值。根据L确定C。

2、VCO输出电压幅度计算有两个限制,一个是电流*寄生电阻,一个是MOS管本身的限幅特性。工作在两个限制的临界可以获得最优的相噪--功耗平衡。

3、可以在pnoise仿真后选result-print-noise anlysis下看输出报告,确定每个管子的噪声影响。

4、增加栅极反馈电容可以加快起振,增大输出幅度,改善相噪。

5、两个滤波电容取值需要注意,过大会造成不稳定。

6、使用PMOS会明显改善flicker noise。但缺点是会造成输出峰值低于地,不注意的情况下会造成sub和源漏的击穿。(如果采用差分电感中心抽头直接连尾电流或者地的方式)

7、尾电流源要不要加?尾电流源建议取比较大的尺寸,可以降低flicker noise.

8、变容管不宜直接接入,可以串合适的电容后再加。

9、FOM1一般做到185。如果电感Q值很高,可以做到190.。一般190是极限。

10、CMOS耦合结构可以省功耗。但也限制了输出幅度,相噪无法改善。

\\\\\\\\\\\

2018/12.18更新

1、上述结构造成振幅不稳定。环路带宽过宽。尝试发现在峰值反馈处加RC低通缩小带宽(MHz)左右才能稳定。具体原因有待计算。

2、Hooman Darabi的射频电路教材中提出class C的尾电流源和class-B相比,其高阻抗具有degneration作用。即:MOS管的负阻是小信号的概念,大信号下,实际电路工作为开关新式,当电路振荡到峰值时,一侧管子关闭,一侧管子开启,此时开启的管子表现为并联的正电阻,对LC tank的Q值有恶化作用。因此带尾电流源的结构具有提高阻值防止恶化的优点。

Darabi同时提出,源极耦合点的旁路电容在射频下表现为低阻抗点,会削弱阻值。因此电容不宜过大。但个人认为Q值的定义以实际的电路损耗为准,电容理论上不造成实际损耗,因此不存在上述问题。但电容的反馈会造成电路的不稳定(具体原因需研究colpitts振荡器)

\\\\\\\\\\\\\

2019/01/04更新

1、尾电流源的闪烁噪声主要还不在于管子本身。而在于普遍采用的电流镜进行复制时,第一级电流的闪烁噪声会放大到最后一级。而这一影响是主要的。

尝试的一种解决方案是挂电阻,通过电阻反馈使MOS管实际上作为共栅管,从而压掉了噪声。这一方案要求MOS自身的共栅增益要大,因此尺寸不宜过大。反过来缩小W*L又会造成flicker noise上升,所以存在一个平衡。目前采用10k左右电阻,效果良好。这一方案对电源有要求,不能过低。(1V以下设计采用此方案较困难)

2、在需要大电容(>1pF,甚至是10pF),而对容值要求不严格的场合(主要起滤波、稳压作用),可以采用MOS管做电容。如为降低成本不提供MIM电容工艺,则用MOS的栅到衬底电容,同等面积下容量较MOM要大得多。然此种方法对衬底噪声有不利影响,需要做好隔离。

本文总结了Class-C VCO的调试经验,包括L和C的选择、VCO输出幅度计算、噪声分析、滤波电容的影响、PMOS使用注意事项、尾电流源设计以及变容管接入策略。还探讨了振幅不稳定的原因和解决方案,强调了电流镜噪声问题及MOS管作为电容的优缺点。

本文总结了Class-C VCO的调试经验,包括L和C的选择、VCO输出幅度计算、噪声分析、滤波电容的影响、PMOS使用注意事项、尾电流源设计以及变容管接入策略。还探讨了振幅不稳定的原因和解决方案,强调了电流镜噪声问题及MOS管作为电容的优缺点。

3570

3570

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?