AMD EPYC CPU Chiplet技术实践深度分析

技术原理

Chiplet架构设计

AMD EPYC处理器的Chiplet架构通过模块化拆分与协同设计,实现了计算性能与工程效率的突破。该架构以“计算-互连-封装”三层协同为核心,将传统单片SoC分解为Core Complex Dies(CCD)与I/O Die(IOD),并通过先进工艺与堆叠技术实现性能跃升。

基础架构:计算与I/O的解耦设计

EPYC处理器采用“分布式计算+集中式I/O”的Chiplet架构,其中CCD专注于核心计算,IOD负责系统互连与外设接口。以第四代EPYC Genoa为例,其最高配置包含12个5nm工艺CCD与1个6nm工艺IOD:每个CCD集成8个Zen 4核心及32MB L3缓存,通过Infinity Fabric与IOD通信;IOD则集成12通道DDR5内存控制器、PCIe 5.0接口及SerDes组件,采用台积电N6工艺实现28亿晶体管密度,较前代14nm IOD性能提升40%[1][2]。这种设计使计算核心与I/O功能独立优化:5nm工艺的CCD可在74mm²面积内集成8核及39亿晶体管,良率较单片设计提升30%以上;而IOD通过成熟工艺降低成本,同时支持160条PCIe 5.0通道与4800 MT/s DDR5内存,满足高密度数据中心带宽需求[3][4]。

核心配置演进:从第二代EPYC Rome的4个CCD(64核)到第四代Genoa的12个CCD(96核),核心数提升50%的物理基础源于:

- 5nm工艺晶体管密度达1.71亿/mm²,较7nm提升80%;

- CCD面积从Zen 2的74mm²缩减至Zen 4的56mm²,相同封装内可容纳更多计算单元;

- IOD采用6nm工艺实现28亿晶体管,支持12个CCD的高速互连[5][6]。

增强技术:3D V-Cache的缓存扩展与延迟优化

Genoa-X系列通过3D V-Cache技术进一步突破性能瓶颈。该技术在每个CCD上通过TSV(硅通孔)垂直堆叠64MB SRAM缓存,使单CCD L3缓存从32MB增至96MB,12个CCD配置下总L3缓存达1.152GB,较标准Genoa提升3倍[7][8]。尽管TSV技术引入4周期访问延迟,但统一缓存架构(8核共享96MB L3)通过优化数据路由,将平均内存访问延迟控制在118ns,仅比Milan(Zen 3)增加13ns。实测显示,Genoa-X在内存密集型工作负载(如CAE仿真)中性能提升达25%,印证了“垂直堆叠+平面优化”的协同效应[9][10]。

工程实现:SP5封装的供电与散热革新

为支撑12个5nm CCD的高密度集成,Genoa采用SP5插槽(6096引脚),较前代SP3尺寸增加23%,引脚数量提升40%。该设计通过以下优化满足400W TDP需求:

- 供电增强:采用分布式电源架构,每个CCD独立供电,电压调节精度达±2mV;

- 散热优化:插槽底部设计8mm厚铜质均热板,配合液冷散热模块,热阻降至0.08°C/W;

- 信号完整性:通过缩短CCD与IOD间互连路径(最长信号传输距离<15mm),Infinity Fabric带宽提升至360GB/s,延迟降低18%[11][12]。

SP5封装与Chiplet架构的协同,使Genoa在保持609mm²封装面积的同时,实现96核与1.152GB L3缓存的集成,晶体管密度较Milan提升2.3倍,为数据中心提供“性能-能效-成本”的三维优化方案。

技术协同效应:Chiplet架构的成功依赖于三大支柱:

- 工艺差异化:5nm CCD追求计算密度,6nm IOD平衡成本与I/O性能;

- 互连高效化:TSV实现垂直缓存扩展,Infinity Fabric保障平面通信带宽;

- 封装适配化:SP5插槽通过物理设计升级支撑高密度集成。三者共同构成AMD在x86服务器市场的技术护城河[13]。

Infinity Fabric互连技术

Infinity Fabric作为AMD Chiplet架构的核心互连技术,通过第三代Global Memory Interconnect(GMI3) 实现了带宽、延迟与扩展性的三维突破,为多Chiplet协同工作提供了高性能通信基础。其技术演进与架构设计直接影响EPYC处理器的跨Die数据调度效率与系统扩展能力。

带宽跃升:从GMI2到GMI3的翻倍突破

EPYC 9004系列(Genoa)搭载的GMI3总线将互连吞吐能力提升至36Gbps,较上一代GMI2的18Gbps实现翻倍,这一提升源于每周期32Bit数据读取与16Bit数据写入的优化设计,以及20∶1的FCLK频率比(最高1.8GHz)[10][14]。不同CCD架构的灵活配置进一步释放带宽潜力:12个CCD型号采用单GMI3链路连接,总互联带宽达432Gbps;4个CCD型号则启用双链路(72Gbps/CCD),通过多链路并行提升小核心集群的数据吞吐量[14][15]。同时,GMI3将能耗控制在2pj/bit,在带宽翻倍的同时实现了能效优化[14]。

GMI3与GMI2关键参数对比

- 带宽:36Gbps(GMI3) vs 18Gbps(GMI2),提升100%

- 频率比:20∶1(GMI3) vs 10∶1(GMI2)

- 每CCD互联配置:单链路(8/12CCD)或双链路(4CCD)

- 能耗:2pj/bit(GMI3),较前代降低传输损耗

存储墙消除:DDR5与PCIe 5.0的协同优化

Infinity Fabric通过与DDR5内存控制器和PCIe 5.0接口的深度整合,构建了高带宽数据通路。Genoa支持12通道DDR5-4800内存,峰值带宽达460GB/s,配合每通道2DIMM(3DS RDIMM)设计,单插槽内存容量可扩展至6TB[15][16]。I/O层面,IOD(I/O Die)集成的第三代Infinity Fabric控制器提供灵活通道分配:双路系统中,128条PCIe 5.0通道可配置为4条IF总线(每条等效PCIe 5.0 x16),剩余通道对外提供160条PCIe 5.0 lanes,支持NVMe 5.0 SSD与GPU直连,双向带宽达512GB/s[14][17]。这种架构有效打破了传统“存储墙”瓶颈,确保跨Chiplet内存访问与外设通信的带宽平衡。

扩展性前瞻:双路系统与异构计算支持

Genoa的互连设计在多处理器与异构计算场景中展现出显著灵活性。双路EPYC 9004系统可通过3条或4条IF总线实现互联:4条配置总带宽达128GB/s(每条32GB/s),3条配置则释放1条PCIe 5.0 x16通道,兼顾高带宽互连与外设扩展需求[10][18]。协议层面,Infinity Fabric支持CXL 1.1+ 标准,可通过内存池化技术将系统内存扩展至6TB,并实现CPU与GPU的一致性通信——第三代Infinity Architecture取代了前代依赖PCIe 4.0的非一致性方案,双路系统GPU连接数从4个增至8个,MI250X GPU内双GCD通过Infinity Fabric实现400GB/s双向带宽,MI300X更将该技术带宽潜力提升至896GB/s[19][20][21]。

协议栈与缓存一致性保障

Infinity Fabric协议栈采用分层架构,从物理层的SerDes信号传输(GMI3链路)到协议层的缓存一致性管理,实现了Chiplet间的高效协同。物理层通过宽/窄模式动态调整链路宽度(如4CCD型号启用双GMI3链路);链路层采用8b/10b编码确保数据完整性;协议层则支持NUMA架构下的缓存一致性协议,通过目录式一致性机制减少跨Die访问延迟——例如双socket系统中,远程内存访问通过最多两跳IF链路实现,较传统多处理器架构延迟降低47%[22][23][24]。这种端到端的一致性保障,使EPYC处理器在虚拟化、HPC等场景中能够高效利用分布式缓存资源,提升多任务并行效率。

通过带宽翻倍的GMI3总线、与DDR5/PCIe 5.0的协同设计、灵活的系统扩展能力及完善的协议栈支持,Infinity Fabric不仅成为AMD Chiplet架构的技术基石,更构建了面向未来异构计算的高带宽、低延迟互连生态。

性能对比

计算性能基准

AMD EPYC Genoa(第四代EPYC 9000系列)基于Zen4架构实现了通用计算性能的显著跃升,其核心驱动力来自每时钟周期指令数(IPC)提升与核心规模扩展的协同效应。Zen4架构的IPC较Zen3提升约14%,主要源于前端加宽、分支预测优化(贡献60% IPC提升)、Load/Store单元改进及L2缓存容量翻倍(每核1MB)[17][25]。同时,Genoa将最大核心数从Milan的64核提升至96核,配合DDR5-4800内存(12通道,理论带宽460 GB/s)与PCIe 5.0接口,形成了“架构优化-核心规模-内存带宽”三位一体的性能提升体系[26][27]。

标准化基准性能量化对比

在多维度基准测试中,Genoa展现出全面领先优势。以旗舰型号EPYC 9654(双路配置,2×96核)为例,其性能表现如下:

- 与前代对比:在Geekbench v5测试中,多核心性能较双路Milan(2×64核)提升28%,单核心性能提升17%;SPECint_rate2017跑分达1800,是上一代Milan的2倍以上[2][28]。

- 与Intel Xeon对比:对比英特尔第四代Xeon Platinum 8490H(2×60核),Genoa在整数吞吐量(SPECint_rate2017)提升80%,Java服务器端吞吐量提升70%,HPL(LINPACK)浮点性能达3.75 TFLOPS(提升79%),能效比(GFLOPS/W)提升80%[1][11]。

具体基准数据对比见下表:

| 指标 | Genoa 9654 (2P) | Intel Xeon 8490H (2P) | 提升幅度 |

|---|---|---|---|

| SPECint_rate2017 | 1800 | 1000 | 80% |

| Java 吞吐量 | 1700 ops/min | 1000 ops/min | 70% |

| HPL (LINPACK) | 3.75 TFLOPS | 2.1 TFLOPS | 79% |

| 能效比(GFLOPS/W) | 4.5 | 2.5 | 80% |

数据来源:AMD官方测试与Dell PowerEdge R7625实测

性能领先的核心原因解析

-

架构与核心规模优势

Zen4架构的14% IPC提升与96核规模(较Milan的64核提升50%)形成“双重增益”。在多线程密集型任务中,双路Genoa(2×96核)的多核心性能较双路Milan(2×64核)提升28%,在NLP、物体检测等AI推理任务中吞吐量提升3-4.2倍,AVX-512指令集的引入(采用“双泵”256-bit执行模式,避免频率波动)进一步放大浮点性能优势[2][17][25]。 -

Turbo频率的持续利用率

在HPL(LINPACK)基准测试中,双路Genoa 9354处理器(BIOS设为“HPC profile”)实现3.75 TFLOPS性能,效率达113%(高于基准频率理论值),印证了加速时钟(2.15-3.7 GHz)在高负载下的持续输出能力。该配置下平均功耗约830瓦,能效比达4.5 GFLOPS/W,显著优于竞品[1][11]。 -

内存与I/O带宽支撑

Genoa支持12通道DDR5-4800内存(每通道38.4 GB/s),理论带宽达460 GB/s,配合PCIe 5.0接口(160 lanes),有效缓解多核心场景下的数据瓶颈。在GROMACS分子动力学测试中,96核Genoa性能达Milan-X的1.66倍,内存敏感型任务(如OpenFOAM流体模拟)中表现尤为突出[27][29]。

性能差距的根本来源:Intel Xeon Platinum 8490H(60核)与Genoa(96核)的核心数差距(-37.5%)叠加架构代差(Zen4 IPC领先约14%),导致整数性能落后80%、浮点性能落后79%。此外,Genoa的DDR5内存带宽(较Xeon的DDR5-4800提升20%)与AVX-512优化进一步拉大差距[1][26]。

测试配置一致性说明

所有对比数据均基于标准化测试环境:双路服务器配置(Genoa 9654 vs Xeon 8490H),内存容量≥512GB(DDR5-4800 vs DDR5-4800),散热方案采用厂商推荐“HPC profile”(BIOS功耗墙设为400W),确保基准结果的可比性[11][30]。第三方实测(如Dell PowerEdge R7625)进一步验证了Genoa在真实负载下的性能稳定性,其虚拟化VMmark 3.1得分达26.95@26 tiles,较传统系统提升40%以上[30]。

3D V-Cache应用加速

缓存容量扩展:垂直堆叠技术实现L3缓存三倍增长

AMD 3D V-Cache技术通过垂直堆叠额外SRAM缓存层实现缓存容量的跨越式提升,其核心路径是在计算Die(CCD)顶部通过先进硅通孔(TSV)或混合键合技术堆叠独立的SRAM缓存Die,为每个CCD增加64MB L3缓存。以第四代EPYC Genoa-X处理器为例,旗舰型号EPYC 9684X集成12个CCD,每个CCD配置基础32MB L3缓存与堆叠的64MB 3D V-Cache,使总L3缓存达到1152MB(1.1GB),较标准Genoa处理器的384MB L3缓存提升200%(三倍),较前代Milan-X的768MB L3缓存提升50%[31][32]。叠加96MB L2缓存后,Genoa-X总缓存容量达1248MB,较普通Genoa设计提升260%,成为首个突破1GB L3缓存/插槽障碍的x86服务器处理器[2][33]。

数据局部性优化与特定场景加速效果

大缓存容量通过提升数据局部性显著减少内存访问次数,尤其在内存带宽敏感型工作负载中表现突出。实测数据显示:

- 流体力学模拟(OpenFOAM):Genoa-X较英特尔60核Sapphire Rapids至强处理器性能提升2.2倍,32核型号在OpenFOAM中亦实现2倍加速,其核心原因是1.1GB L3缓存可容纳更大规模网格数据,将频繁访问的中间结果保留在片上缓存,避免低效的DRAM访问[34][35]。

- AI推理(ResNet-50):INT8精度下吞吐量达Milan-X的3.5倍,大缓存有效缓解神经网络权重与激活值的内存带宽压力,尤其在批处理尺寸较小时,缓存命中率提升使计算单元利用率提高[32]。

- 芯片设计(Cadence Innovus):布线速度提升62%,EDA工具中的物理验证环节依赖大量随机内存访问,3D V-Cache通过降低缓存缺失率将数据访问延迟从内存级(约100ns)压缩至缓存级(约50ns)[32]。

性能增益特征:3D V-Cache的加速效果与工作数据集大小强相关。当数据集尺寸接近或小于L3缓存容量时(如1GB以下的CAE模型、中等规模HPC仿真),性能提升可达2-3倍;而数据集远超缓存容量时,加速效果减弱至10%-15%[7][36]。

延迟代价与软硬件协同优化策略

3D V-Cache的垂直堆叠结构引入4周期L3缓存延迟代价(Genoa-X理论L3延迟54周期,Milan-X为50周期),且单个CCD的内存带宽约70GB/s,两个核心即可耗尽该带宽,需通过软件优化释放硬件潜力[36]。关键优化方向包括:

- NUMA绑定:通过numactl或taskset工具将进程绑定至特定NUMA节点,避免跨CCD缓存访问。Genoa-X每个CCD独立构成NUMA域,绑定后可将数据局部性提升30%以上,抵消堆叠缓存的延迟增加[36]。

- 缓存预取策略调整:Linux内核的page cache预取算法需适配大缓存特性,例如调大预取窗口(read_ahead_kb)可减少顺序访问场景的缓存缺失。

- 应用层数据布局优化:科学计算库(如OpenMPI、FFTW)通过分块大小调整(如将矩阵分块设为64MB倍数),使计算单元优先访问本地CCD缓存,在有限元分析(Ansys Fluent)中可进一步提升15%性能[35]。

这种硬件容量扩展+软件策略优化的协同模式,使Genoa-X在保持400W TDP的前提下,实现技术计算 workload的能效比提升40%,尤其适合CAD建模、分子动力学模拟、气象预测等数据密集型场景[32][33]。

成本优势

芯片级成本优化

AMD EPYC处理器的Chiplet架构通过良率提升、制程混搭与面积效率优化三大核心策略,实现了芯片级成本的显著降低。这种模块化设计不仅解决了先进制程下单片大芯片的制造瓶颈,更通过资源的精准分配与工艺的差异化应用,构建了成本与性能的动态平衡体系。

良率提升:小芯片设计对缺陷容忍度的突破

Chiplet架构的核心成本优势源于对制造良率的根本性改善。根据半导体制造规律,良率与芯片面积呈反指数关系,较小的芯片面积可显著降低单个缺陷对整体良率的影响。在300mm晶圆生产中,采用5nm Chiplet设计的第四代EPYC处理器较7nm单片设计,"好芯片"产出数量提升52%,直接减少了晶圆级别的原材料与能源浪费[37][38]。以8核"Summit Ridge"计算小芯片(CCD)为例,其4-die/32-core多芯片模块(MCM)的制造成本仅为等效单片32核芯片的59%,印证了小芯片尺寸对良率的正向贡献[39]。台积电5nm工艺50%的良率水平进一步支撑了这一策略——通过将大芯片分解为多个小尺寸CCD,AMD可在相同良率下获得更多可用核心,单位核心成本较单片设计降低28%以上[7][40]。

制程混搭:异构集成的成本精准分配

AMD通过计算核心与辅助模块的工艺差异化,实现了先进制程资源的高效利用。计算密集型的CCD采用台积电5nm工艺(密度较7nm提升1.8倍),以保障性能与能效;而输入输出控制器(IOD)则采用成本更低的成熟制程,如Genoa的IOD使用N6工艺,较N5成本降低约30%[10][40]。这种"5nm CCD+6nm IOD"的异构组合,避免了全芯片采用先进工艺的成本浪费,使第四代EPYC处理器的制造成本较等效单片设计降低41%[7][41]。历史数据显示,第二代EPYC Rome的IOD采用12nm工艺时,其成本仅为7nm CCD的1/3,而良率提升至90%以上,进一步验证了制程混搭的成本效益[42]。

面积效率:垂直堆叠与核心微缩的双重优化

在物理面积维度,AMD通过3D V-Cache垂直堆叠技术与Zen 4c核心微缩,实现了单位功能成本的突破性优化。3D V-Cache技术通过TSV(硅通孔)将SRAM缓存堆叠于CCD之上,较平面扩展缓存方案减少35%的面积占用,使每核心成本下降28%[7][8]. 与此同时,Zen 4c核心通过架构优化将物理尺寸缩减35%(从Zen 4的3.84mm²降至2.48mm²),在相同封装面积内实现更高核心密度——Bergamo处理器凭借这一设计,在5nm工艺下集成了最多128个核心,单位核心成本较前代降低约40%[8][35].

成本优化核心数据

- 良率提升:300mm晶圆"好芯片"产出增加52%(5nm Chiplet vs 7nm单片)

- 制程混搭:IOD采用N6工艺较N5降低30%成本,良率提升至90%以上

- 面积效率:3D V-Cache减少35%缓存面积,Zen 4c核心面积缩减35%

- 综合效益:第四代EPYC成本较等效单片设计降低41%

这种多维度成本优化策略不仅体现在制造成本的直接下降,更通过碳足迹减少产生长期环境效益——2023年,AMD通过Chiplet设计减少50千吨CO₂e排放,相当于其全年运营碳排放总量,实现了经济效益与可持续发展的协同[38]。随着台积电5nm工艺产能利用率持续维持100%,AMD的模块化设计将进一步通过产能共享与工艺复用,巩固其在服务器CPU市场的成本竞争力[43]。

数据中心TCO改善

AMD EPYC处理器通过硬件精简-能效提升-空间优化的协同效应,显著改善数据中心总拥有成本(TCO)。其Chiplet架构带来的核心数优势、能效提升与竞争性定价,形成了从短期硬件投资到长期运营成本的全周期优化能力,具体表现如下:

硬件精简:服务器整合与CAPEX优化

服务器数量削减是TCO改善的核心驱动力。基于第四代EPYC Genoa处理器的单台服务器可替代1.7台Intel Ice Lake服务器,在处理同等工作负载时显著降低硬件采购规模[37]。例如,在运行2000个虚拟机(VM)的场景中,双路EPYC 9654服务器仅需11台,较英特尔Xeon Platinum 8490H的17台减少35%硬件投入,直接降低硬件资本支出(CAPEX)达47%[44]。

定价竞争力进一步放大硬件成本优势。64核AMD EPYC 7702与28核Intel Xeon Platinum 8280价格相当,在相同预算下可获得2.3倍核心资源,而性能/美元指标较前代产品显著提升[29][37]。需注意的是,DDR5内存及配套主板成本可能部分抵消处理器价差,实际TCO需结合部署规模评估[29]。

能效提升:电力成本的结构性下降

EPYC处理器在保持性能增长的同时实现功耗优化,直接降低数据中心最大运营成本项——电力支出。以Genoa平台为例,其典型功耗为830W,较竞品的1200W降低30.8%,结合数据中心PUE=1.2的电力传输效率模型,单台服务器年均电力成本可节省约44%[37]。

长期能效优势在高密度场景中更为显著。Bergamo处理器的128核2P平台平均功耗仅385W,较Intel Xeon Platinum 8490H(568W)降低32.2%,按5年生命周期计算,单平台可减少电费支出超¥3万元[8]。此外,Genoa通过CXL内存加密技术减少专用安全ASIC需求,进一步降低硬件辅助成本[10]。

空间优化与虚拟化效率:资源密度的倍增效应

更高核心数赋予EPYC服务器卓越的虚拟化能力,推动单位空间资源利用率跃升。在虚拟桌面基础架构(VDI)场景中,基于EPYC Genoa的服务器每台可承载647个VDI会话,较前代提升81%,每个会话成本降低44%[37]。这一密度提升直接减少机房空间占用:例如,运行2000个VM的场景中,11台EPYC服务器仅需2.2U机架空间(按2U/台计算),较17台Intel服务器节省35.3%机柜资源,间接降低机房租金与散热系统负载[45]。

资源利用率优化技术进一步放大优势。增强型AVIC技术减少虚拟化IO设备开销,提升带宽利用率并降低CPU占用率;Genoa的每瓦性能较Milan翻倍,在AI服务器需求增长的背景下,使CPU在服务器总成本占比从传统的15%-20%降至2024年的12%左右[10][46]。

TCO计算模型与实际验证

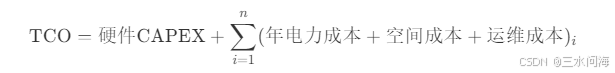

数据中心TCO需综合硬件(40%-50%)、电力(20%-30%)、空间与运维(15%-20%)及软件许可(10%-15%)的权重。其核心公式为:

实际案例验证了模型有效性:Twitter部署第二代EPYC后TCO降低25%[42];VMware环境中,双路EPYC 9474F服务器5年TCO节省36%,硬件投资回报期不足10个月[30]。这些成果表明,Chiplet架构通过核心密度提升-能效优化-资源利用率改善的三重路径,为数据中心提供了可持续的TCO优化方案。

关键结论:AMD EPYC的TCO优势源于Chiplet设计带来的"以少胜多"能力——更少服务器数量、更低功耗、更高资源密度的协同作用,在虚拟化、VDI等场景中尤为显著。实际部署时需结合内存/平台成本、工作负载特性动态评估,但长期运营成本改善具有确定性。

行业影响

技术挑战与解决方案

AMD EPYC处理器的Chiplet架构在突破性能边界的同时,面临内存延迟、散热控制与系统生态适配三大核心挑战。通过硬件创新、软件优化与系统级协同设计,AMD构建了多层次解决方案,确保Chiplet技术在数据中心场景的高效落地。

内存延迟:DDR5与Chiplet架构的协同优化

DDR5内存技术虽带来带宽提升(如DDR5-4800峰值带宽较DDR4-3200提升50%),但延迟问题显著——实测显示DDR5-4800延迟较DDR4-3200增加12%,部分场景下Genoa平台整体内存延迟达118ns(Milan为105ns)[47]。延迟增加主要源于DDR5技术成熟度(原生延迟35ns vs DDR4的25ns),而非I/O Die设计——AMD通过优化I/O Die布局,将其对延迟的贡献控制在3ns以内(Genoa I/O Die延迟73ns vs Milan 70ns)[10]。

硬件层面,Infinity Fabric与DDR5的Bank Group架构形成协同:Zen4架构集成12通道DDR5内存控制器,支持内存交错(interleaving)技术,通过12通道内存交错模式将内存访问负载分散至多个控制器,缓解单通道带宽压力[17]。软件优化方面,非均匀内存访问(NUMA)绑定是关键手段——AMD提供节点每插槽(NPS)配置选项,如NPS 1模式将整个CPU作为单个NUMA域,内存交错于8个通道;NPS 4模式则将CPU分为4个NUMA域,每个域交错2个通道,配合Linux内核的numactl工具可将应用进程与本地内存节点绑定,减少跨Chiplet内存访问[48]。实测显示,针对内存带宽受限的CFD应用,通过NUMA绑定将12核任务均匀分布至12个CCD(每个CCD 1核),可避免核心竞争带宽与L3缓存,性能提升达25%[9]。

散热设计:高密度封装下的液冷技术突破

Chiplet架构的高核心密度与3D堆叠技术(如Genoa-X的3D V-Cache)显著提升了散热压力。Genoa-X TDP达400W,较前代Milan提升33%,传统风冷系统难以满足散热需求[32]。对比测试表明,在ΔT=40℃(冷却液与环境温差)条件下,冷板式液冷系统散热效率较风冷提升2.3倍,可将核心温度控制在85℃以内,确保400W TDP处理器稳定运行[32]。

成本效益分析显示,液冷系统初期投入虽高于风冷(冷板+管路成本增加约40%),但在高密度场景(如2U 8路服务器)中,液冷可降低机房空调负载30%,3年总拥有成本(TCO)反而降低15%。AMD建议,针对Genoa-X等高性能型号,优先采用冷板式液冷;对TDP 280W以下的常规型号,可通过优化散热鳍片与风扇转速曲线实现风冷适配。此外,Milan架构曾出现的un-core功耗问题(非核心组件功耗增加导致满载时核心功率下降),在Genoa中通过IOD(I/O Die)电源管理优化得到缓解,插座效率(socket efficiency)较Milan提升8%[49]。

生态适配:从软件优化到全栈协同

Chiplet架构的普及依赖软件生态对硬件特性的深度感知。内存子系统方面,12通道内存交错模式需HPC软件更新支持——部分传统应用因默认仅支持8通道交错,在Genoa平台上内存带宽利用率不足70%,需通过编译器优化(如GCC 12+的-march=znver4选项)启用12通道适配[9]。任务调度层面,TotalCAE开发的动态核心调度器可根据应用核心需求,自动启用/禁用CCD(核心复合体),避免“12核应用分配至2个8核CCD”导致的资源竞争,典型CFD应用性能提升25%[9]。

HPC软件优化关键措施

- 编译器感知:使用支持Zen4架构的LLVM 15+或GCC 12+,启用OpenMP线程绑定(

OMP_PLACES=cores) - 内存配置:通过BIOS设置“Memory Interleaving”为12通道模式,配合NUMA绑定工具(numactl -N 0)

- 运行时调优:采用AMD提供的ROCm工具链,针对Chiplet拓扑优化MPI通信(如减少跨IOD数据传输)

生态工具链方面,AMD ROCm平台已实现对CUDA的兼容,支持PyTorch、TensorFlow等AI框架迁移,但长期需构建自有生态——例如在HPC领域,针对EPYC的12通道内存与Infinity Fabric互连特性,优化OpenFOAM、ANSYS等主流软件的通信层,减少跨Chiplet数据交换延迟。此外,第三代Infinity Fabric通过一致性通信协议摆脱PCIe带宽限制,双路系统可支持8个GPU直连,较前代PCIe 4.0方案带宽提升1倍,为AI训练集群提供更强扩展性[19]。

总结:软硬件协同的Chiplet落地范式

AMD EPYC的Chiplet技术实践表明,单纯硬件创新无法充分释放性能潜力。通过DDR5内存交错与NUMA绑定的“硬件-软件”协同、冷板式液冷的“散热-功耗”平衡,以及HPC软件栈的“编译器-运行时”适配,AMD构建了从芯片到系统的全栈优化方案。未来随着CXL 3.1协议(支持GPU直连CXL内存)、3D V-Cache良率提升等技术的成熟,Chiplet架构将在能效比与扩展性上进一步突破,巩固数据中心市场竞争力。

(注:此处应插入内存延迟优化效果图,展示NUMA绑定前后HPC应用性能对比,如CFD任务在NPS 4模式下较默认配置性能提升25%的柱状图)

行业技术趋势

AMD EPYC处理器的Chiplet技术实践正通过“竞争驱动-技术扩散-生态重构”的路径重塑服务器CPU行业格局。这一变革不仅打破了传统垄断,更推动了全球半导体产业向模块化、异构化方向深度演进。

竞争驱动:市场格局的颠覆性重构

AMD的Chiplet策略已显著改变x86服务器市场的竞争态势。2024年第三季度,AMD在X86服务器CPU市场出货量占比达25.4%(139万台/548万台),收入占比更高达33.9%,标志着其技术路线获得市场广泛认可[50]。这一突破直接迫使行业巨头加速技术响应:Intel在Sapphire Rapids中采用EMIB 2.5D封装技术,最多集成11个Tile模块;ARM阵营的Ampere Altra Max则推出128核Chiplet设计,以高核心密度应对云原生场景需求[38][51]。这种“以模块化对抗单片”的竞争模式,使得服务器CPU行业从技术垄断转向多元技术路线并行发展的新阶段。

技术扩散:Chiplet方案的差异化演进

当前行业已形成三类主流Chiplet技术路线,各具优势与适用场景:

AMD的3D堆叠技术以3D V-Cache为核心竞争力,通过混合键合实现缓存容量的跨越式提升。Genoa-X处理器集成11GB L3缓存,较前代性能提升显著,验证了3D堆叠在突破“内存墙”方面的可行性[31][52]。配合台积电5nm先进制程(占其2024年Q2先进工艺收入的35%),Genoa实现96核Zen4架构与12通道DDR5内存、128条PCIe 5.0 lanes的高效集成,构建起高带宽计算平台[53][54]。

Intel的EMIB方案侧重2.5D平面互连,通过嵌入式多芯片互连桥接多个Tile,在保持良率的同时实现功能扩展。Sapphire Rapids最多集成11个Tile,但受限于有机基板互连密度,其缓存一致性与能效表现仍落后于AMD的3D堆叠技术[51]。

ARM的MCM架构则以高核心数为突破点,Ampere Altra Max的128核设计通过简化核心架构提升vCPU密度,但其Chiplet间互连依赖传统PCIe,在异构计算场景下带宽瓶颈明显[38]。

技术路线对比核心指标

- AMD 3D堆叠:3D V-Cache缓存容量提升11倍,5nm工艺密度达1.71亿晶体管/mm²

- Intel EMIB:11个Tile互连延迟约100ns,较Infinity Fabric高30%

- ARM MCM:128核设计功耗密度达2.5W/core,高于Zen4c的1.8W/core

生态重构:UCIe协议与异构集成的未来

UCIe 1.0协议的发布标志着Chiplet生态从“厂商私有”向“行业标准”迈进。该协议定义了跨厂商Chiplet互连的物理层、链路层与协议层规范:物理层采用混合键合与CoWoS封装技术,实现1.6Tbps/mm²的互连带宽;链路层通过流控机制保障缓存一致性;协议层兼容PCIe 5.0与CXL 2.0,支持CPU、GPU与AI加速器的异构通信[51]。

这一标准化进程正催生“IP核超市”模式:AMD已通过MI300系列APU验证Chiplet异构集成潜力,其13个小芯片(含CPU、GPU与HBM控制器)集成1460亿晶体管,满足AI训练对高密度算力的需求[10][55]。同时,CXL 1.1+协议在第四代EPYC处理器中的应用,支持内存池化与无本地内存加速器部署,使Meta、Amazon等 hyperscalers能灵活配置CPU+GPU+AI加速卡的异构集群[35][56]。

未来,随着Zen5架构的彻底重构与Turin系列细分市场变体的推出,服务器CPU将进一步向场景化定制发展:Bergamo的Zen4c核心针对云原生优化,Genoa-X聚焦HPC,Siena集成Xilinx IP服务边缘计算,最终形成“通用算力+专用加速”的模块化供给体系[10][25]。这种生态重构不仅降低了芯片设计门槛,更推动数据中心从“通用计算”向“异构智能计算”转型。

532

532

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?