1,axi4基础知识

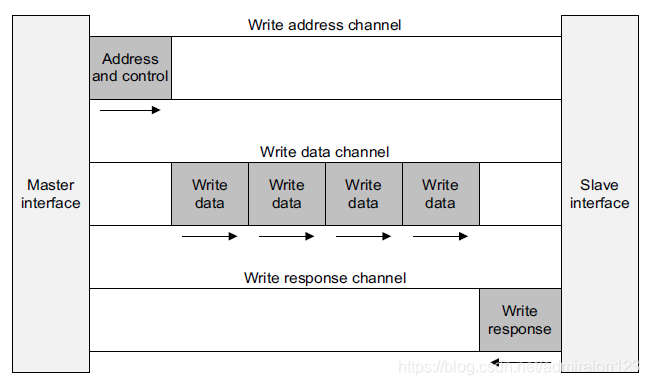

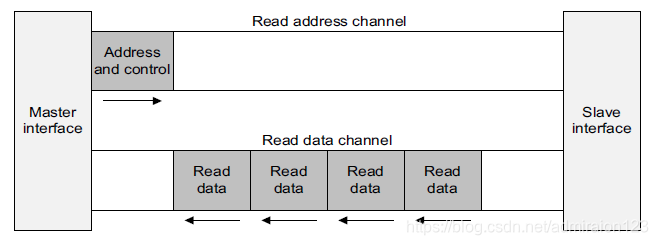

axi(advanced extensible interface)高级可扩展总线接口是一种总线,是ARM公司提出的AMBA(advanced microcontroller bus architecture)高级微控制器总线结构协议中的一部分,它是一种高性能、高带宽、低延迟片内总线结构。axi4协议可百度IHI0022G,然后找资源下载。axi总线有5个独立的事物通道(transaction channel),写结构包含3个通道,为写地址通道AW,写通道W,写响应通道B;读结构包含两个通道,为读地址通道AR,读通道R。地址通道包含控制信息,用于描述数据通道中数据的含义。数据通道包含实际传输的数据。写响应通道用于写流程中slave告知master数据接收完成。axi总线支持突发读写模式,支持多个事物处理(outstanding),支持事物按乱序完成(out of order)。下面两图为写结构和读结构。

1.1,握手机制

axi接口的5个通道都是基于握手原则进行数据传输的,即都拥有独立的valid和ready信号。valid用于表示源端(master)数据准备好。ready用于表示目的端(slave)已准备好接收数据。当valid和ready同时拉高时,即发生一次transfer。特别的,读、写数据通道包含last信号,用于表示一次传输事物的最后一个数据。这是一种双向的流控制机制,即主和从都可以控制他们之间数据传输的速率。aclk为全局时钟信号,axi中的所有信号都以aclk上升沿做同步,即目的端在aclk上升沿采样,源端在aclk上升沿后输出,因此axi总线两端的接口是不允许存在组合逻辑的。aresetn为全局复位信号,低有效,复位时不做要求,但复位释放时需要与aclk同步。

值得注意的是,valid信号在拉高前,不能够等待ready信号;且valid一旦拉高,就必须等待ready拉高,完成一次transfer才能拉低。而ready信号在拉高前,可以等待valid信号;且ready拉高后,也无需握手就可以拉低。

读流程的握手如下图所示,读流程握手比较简单,master在读地址通道将arvalid拉高,slave在读地址通道将arready拉高,两者没有必然前后关系。slave检测到读地址通道握手信号同时为高,则在读数据将rvalid信号拉高,master在读数据通道检测到握手信号同时为高,则开始接收数据。

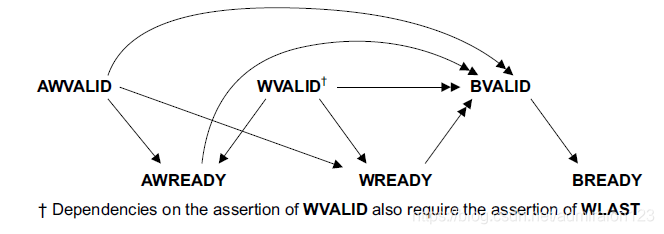

写流程的握手如下图所示,需要注意的是,slave需要在检测到写数据通道写有效信号wvalid,写准备信号wready和标志一次传输事务的最后数据标志wlast时,才在写响应通道将bvalid信号拉高。

1.2,通道信号

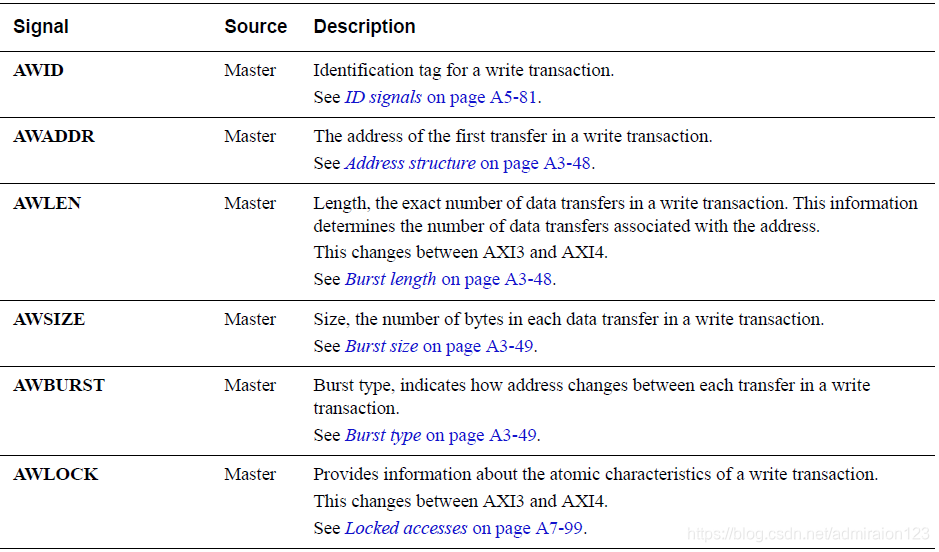

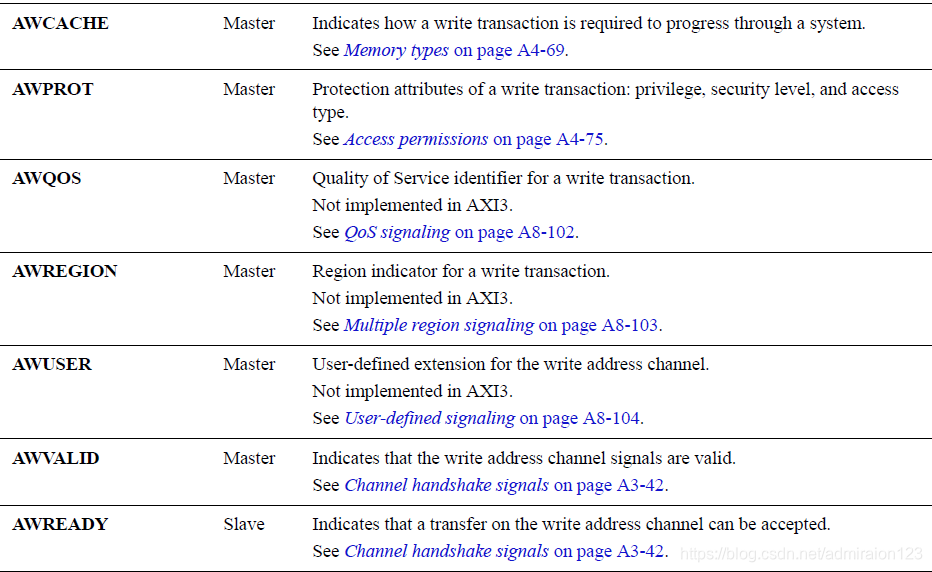

写地址通道AW中的信号如下图所示。awaddr是一次数据写事务中第一次写数据的初始地址;awlen是一次写数据事务中数据传输次数(the nubmber of transfers),具体次数为awlen[7:0]+1;awsize是一次写数据事务中一次数据传输(transfer)的长度,具体为2^awsize[2:0];awburst是一次写事务中突发类型(burst type)。突发类型一般使用INCR模式,即地址每次增加awsize大小。读地址通道AR类似。

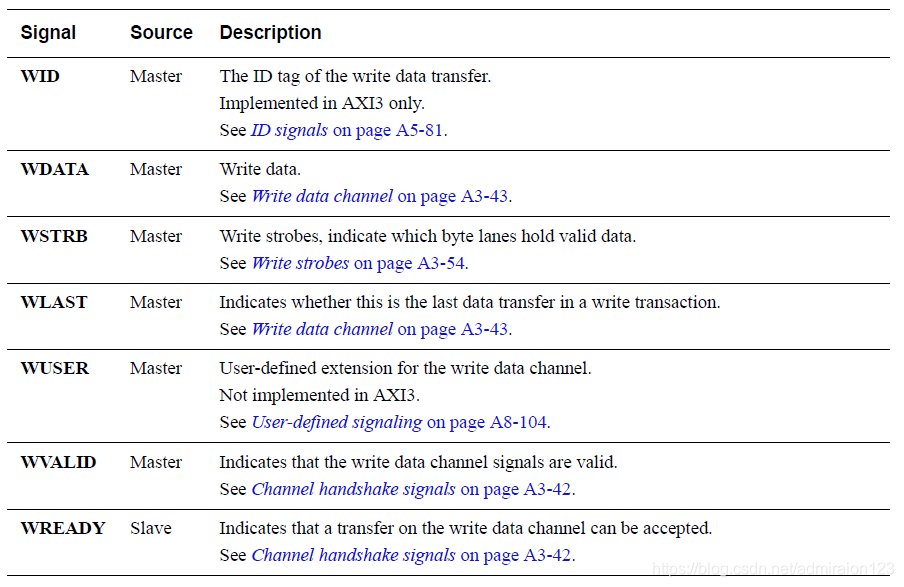

写数据通道W中的信号如下图所示,wdata是一次写事务中一次写传输的数据;wstrb是一次写事务中数据选通信号,wstrb[n]对应wdata[8n+7:8n];wlast是一次写事务中一次写事务中的最后一次数据传输。读数据通道R类似。只是多了rresp信号,表示读事务中数据传输成功与否。

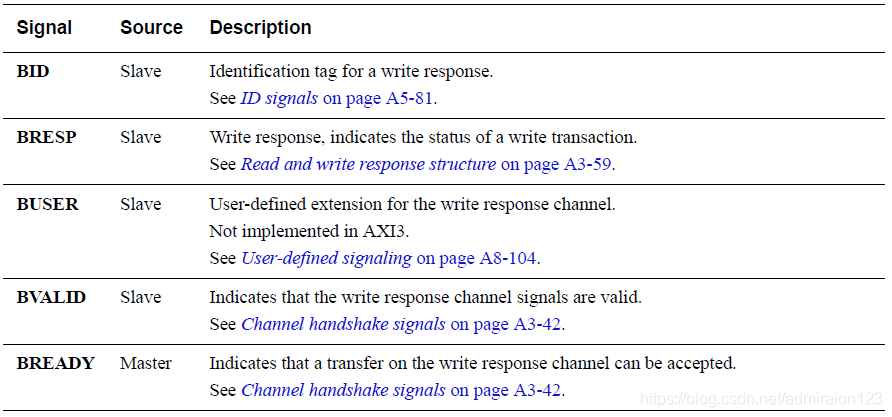

写响应通道B中的信号如下图所示,bresp是一次写事务当中的响应,axi4中只有bresp[1:0]有效,00代表正常。salve接收到写地址通道和写数据通道的信息后,都需要应答。

1.3,axi4_lite简介

axi4_lite与axi4相比,有以下几点不同:a,只支持burst长度为1的传输,即axlen信号为1;b,只支持32bit或者64bit数据位宽;c,只支持non-modifible、non-bufferable传输属性模式。

1.4,axi4_stream简介

axi4_stream协议可以百度IHI0051A,然后下载资源。该协议用于设备之间数据交互,没有地址的概念,数据是以流的形式存在。在总线上,数据类型有三种:a,data,即带有效信息的数据;b,position,表示字节相对位置信息,一般用于两个packet之间;c,null,表示无效字节。三种数据的划分使用tkeep[n-1:0]和tstrb[n-1:0]信号,都是按字节对应。tkeep用于表示数据必须从源端到目的端,而非null字节。tstrb用于表示数据是数据字节,而非位置字节。tlast信号用于表示一个包的结束。

axi4_stream中,需要明确几个概念:1,transfer,一次transfer就代表一次握手,传输一个数据单元;2,packet,由多个transfer构成,相当于axi4中的一次burst;3,frame,由多个packet构成,例如一个图像帧。4,data stream,axi_stream总线上的数据,可以是多个单独的transfer,也可以是一系列packet。

1603

1603

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?