到中流击水—MIG-DDR3

一、到中流击水—DDR3时钟部分

(重点,这一部分时钟关系,能够进一步帮助理解DDR3预读取工作)

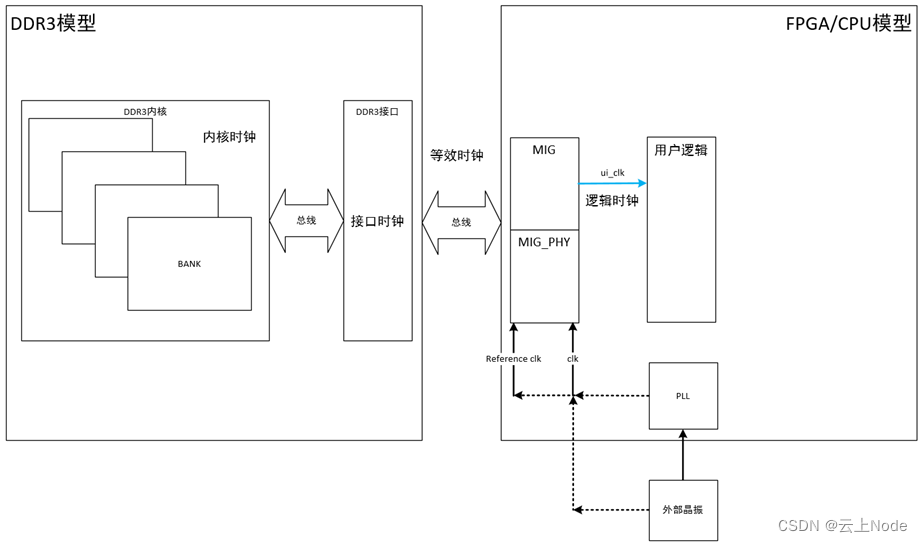

DDR3 FPGA时钟框图搭建

DDR3部分三个时钟(上图左侧部分)

1.DDR3内核时钟:DDR3内部逻辑部分使用的时钟,用户侧无需关心,跟DDR3芯片内核性能相关。

2.DDR3接口时钟:DDR3与外界通信实际使用的时钟(实际时钟),跟DDR3芯片接口性能相关。

3.DDR3等效时钟:DDR3与外界通信实际的有效时钟(双倍速率)。

FPGA部分三个时钟(上图右侧部分)

1.FPGA参考时钟:FPGA用于MIG IP数据传输的参考时钟,固定频率200MHz;

可以由PLL提供、系统时钟(200MHz外部时钟)、外部差分(单端)输入。

2.FPGA IP时钟:FPGA用于MIG IP内部逻辑的时钟;

它可以由PLL提供、外部差分(单端)输入。

3.FPGA用户时钟:FPGA用于给用户提供设计的时钟;

它是由MIG控制器输出给用户的时钟。

DDR3芯片预读取原理

上图分析可知,内核,接口所用的时钟频率不同,所以可以有如下假设:

假设内核工作在100MHz,接口工作在400MHz。内核一次把8bit’数据准备好,来满足接口双沿传输使用(8:1);这就是预读取原理。在不提升内核工作频率情况下,通过预读取方法提高数据传输带宽。

上述部分内容参考了部分网友分享的资料

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1724

1724

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?