赋值操作将赋值操作符右侧的值放入赋值操作符左侧的网络(nets)和变量(variables)。赋值有两种基本形式:

- 连续赋值(continuous assignment):为网络赋值

- 过程赋值(procedural assignment):为变量赋值

另外,还有两种不常见的赋值形式:赋值/去赋值(assign/deassign)和强制/释放(force/release),这两种赋值形式被称为过程性连续赋值,有时间后面博客再介绍这两种不常见赋值形式,我们还是先来看看最常用的连续赋值和过程赋值吧~

赋值操作由左侧和右侧两部分组成,两部分之间用等号 ( = ) 字符隔开;如果是非阻塞过程赋值,则用小于等于号 ( <= ) 字符对隔开。右侧可以是任何求值的表达式,左侧表示要为其赋值的网络(nets)或变量(variables)。根据赋值类型是连续赋值还是过程赋值,左侧可以采用下表1所示的形式之一。

|

赋值形式 |

左侧表示 |

|

连续赋值 |

网络(矢量或标量) 矢量网络的位选择 矢量网络的部分位选择 矢量网络的索引部分选择 上述任何连接或嵌套连接 |

|

过程赋值 |

变量(矢量或标量) 矢量reg、integer或time变量的位选择 矢量reg、integer或time变量的部分位选择 矢量reg、integer或time变量的索引部分选择 内存字(Memory word) 上述任一左侧的连接或嵌套连接 |

表1:赋值语句中的左侧合法形式

连续赋值(Continuous assignments)

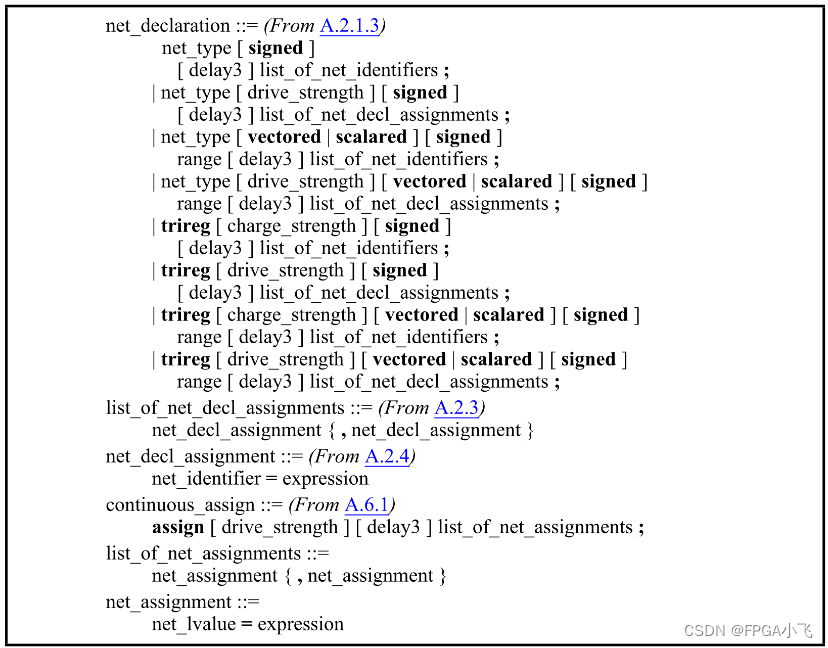

连续赋值将右侧的数值驱动到左侧的矢量net或标量net中,每当右边的数值发生变化时,就会执行这种赋值操作。连续赋值为组合逻辑建模提供了一种无需指定门互连的方法,相反该模型指定了驱动net的逻辑表达式。连续赋值的语法规则如下表2所示:

表2:连续赋值的标准语法

网络声明赋值(The net declaration assignment)

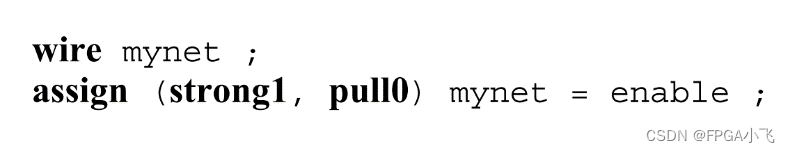

根据表1的标准语法,我们很容易理解通用的网络声明,例如:

wire (strong1, pull0) mynet;

表1的标准语法还给出了网络声明赋值,即允许在声明网络的同一语句中对网络进行连续赋值,例如:

wire (strong1, pull0) mynet = enable;

连续赋值声明(continuous assignment statement)

连续赋值声明在net数据类型上进行连续赋值,赋值操作是连续和自动的。换句话说,每当表达式右侧中的一个操作数的值发生变化时,都要对整个右侧表达式进行评估,如果新值与前值不同,则应将新值赋值给表达式左侧。

例如下面是对先前已声明的网络进行连续赋值的示例1:

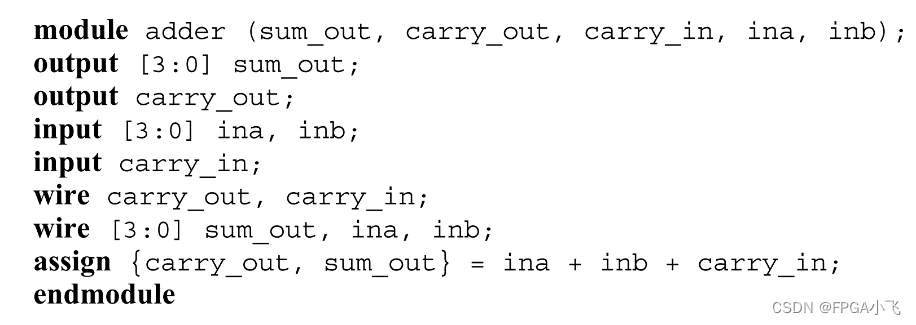

示例2-下面是一个使用连续赋值来模拟带进位的 4 位加法器的示例。该赋值不能直接在网络声明中指定,因为它需要在左侧进行连接:操作

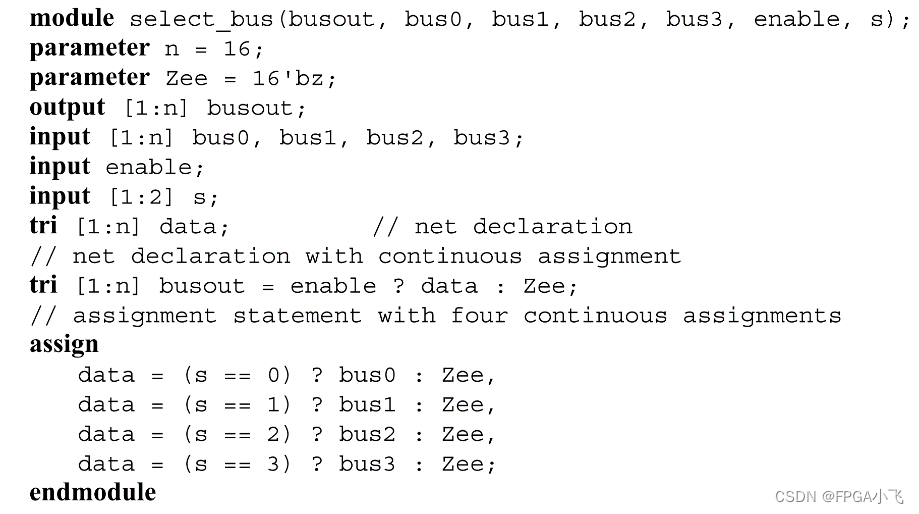

示例3-下面描述了一个具有16位输出总线的模块。它从四条输入总线中选择一条,并将所选总线连接到输出总线:

在本例的模拟过程中,发生了以下一系列事件:

a) 在赋值语句中检查总线选择器输入变量s的值。根据s的值,网络data从四条输入总线bus0~bus3之一接收数据。

b) 网络data的设置触发了busout输出网络声明中的连续赋值。如果使能enable为1,data的内容将被赋值给busout输出;如果使能为 0,Zee 的内容将被赋值给busout输出。

过程赋值(Procedural assignments)

连续赋值与过程赋值之间有很大的区别。如前所述,连续赋值驱动网络net的方式与门驱动网络net的方式类似,其右侧的表达式可以看作是连续驱动网络net的组合电路,与此相反,过程赋值将右侧值放入变量variable中。net连续赋值没有保持时间,相反变量variable会保持赋值的值,直到下一次过程赋值更新该variable变量的值,而且过程赋值只发生在过程块中,如always、initial、task和function,可以看作是 "触发 "赋值。

变量(variable)声明赋值

变量声明赋值是过程赋值的一种特殊情况,它允许在声明变量的同一语句中为变量赋初始值,初始值是一个常量表达式,且赋值没有保持时间;相反,变量在下一次赋值之前一直保持该值。另外,verilog不允许对数组(array)进行变量声明赋值。如果同一变量在初始化模块和变量声明赋值中被赋予了不同的值,则该变量值是不确定的。下面我们举例说明变量的声明及赋值操作:

示例1-声明一个 4 位寄存器并赋值 4:

reg [3:0] a = 4'h4;

等价于

reg [3:0] a;

initial a = 4'h4;

示例2-非法的数组变量声明赋值:

reg [3:0] array [3:0] = 0;

示例3-声明两个integer变量,第一个integer赋值值为0:

integer i = 0, j;

示例4-声明两个real变量,赋值分别为 2.5 和 300000:

real r1 = 2.5, n300k = 3E6;

示例5-声明具有初始值的time变量和realtime变量:

time t1 = 25;

realtime rt1 = 2.5;

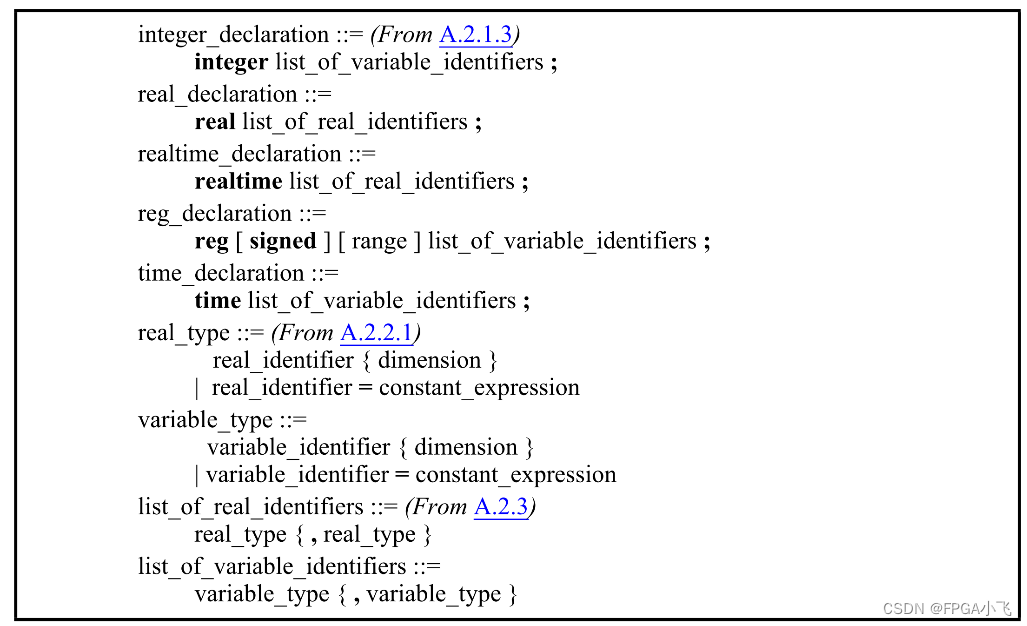

如下表3所示为变量(variable)声明赋值的标准语法总结:

表3:变量声明赋值标准语法

点赞加关注博主(ID:FPGA小飞)的博文,咱们一起系统学习verilog最终标准IEEE Std 1364-2005吧!

&spm=1001.2101.3001.5002&articleId=139940871&d=1&t=3&u=b4ca51e665d945d298555550689ed388)

592

592

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?