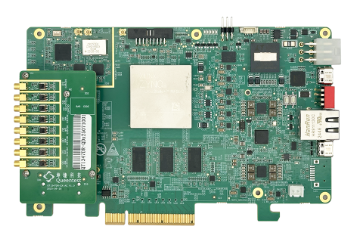

基于PCIe架构的多通道射频收发卡:板卡选用高性价比的Xilinx的Zynq UltraScale+ RFSoC系列中XCZU47DR-FFVE1156作为处理芯片((管脚可以兼容XCZU48DR-FFVE1156,主要差别在有无FEC(信道纠错编解码)),其PS端搭配一组4颗16bit的DDR4颗粒,总容量达到4GB;PL端搭配一组2颗16bit的DDR4颗粒,总容量达到2GB。

板卡直接支持8通道AC耦合的14bit 9.85GS/s的DA采样输出,预留有高速信号接口,可适配DC或者AC耦合的8通道14bit 5GS/s的AD输入子卡。板卡同时还支持外部触发信号、外部参考时钟和外部同步时钟输入3个独立接口,通过PCIe 4.0 x8高速接口与上位机互联互通。

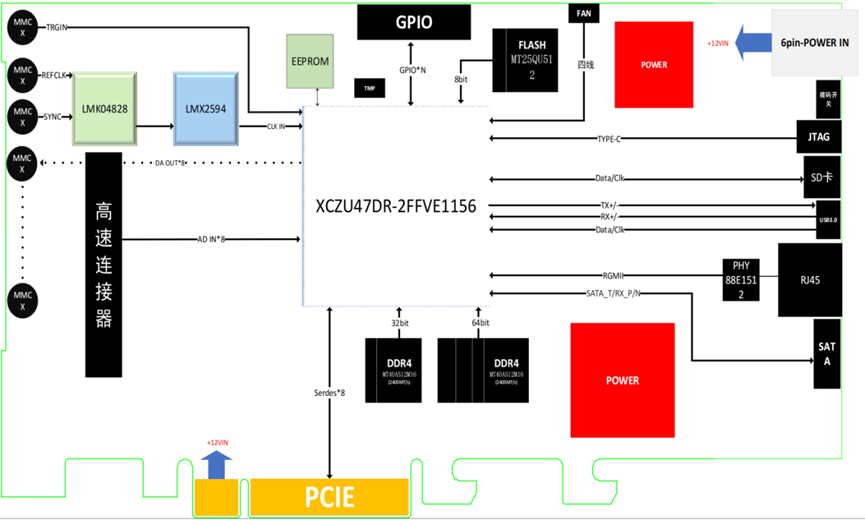

- 载板8个MMCX接口,支持8路14bit,9.85GS/s模拟信号输出,AC耦合;

- 子卡8个MMCX接口,支持8路14bit,5GS/s模拟信号输入,AC/DC耦合可选;

- 主芯片XCZU47DR-FFVE1156(管脚兼容XCZU48DR-FFVE11561);

- PS端搭配一组4颗16bit的DDR4颗粒;PL端搭配一组2颗16bit的DDR4颗粒,总容量达到6GB;

- 支持外部触发信号、外部参考时钟和外部同步时钟输入3个独立接口;

- 支持一个SATA接口,一个RJ45千兆网口,一个USB3.0接口,一个SD卡接口,一个TYPE-C形式的JTAG调试口以及一个6pin的外部电源输入口;

- 板载温度传感器电路,支持温度监控;

- 2颗512Mb 4bit的QSPI Flash并成一个8bit的SPI Flash存储;

- 一个2x9的牛角座可支持13路标准GPIO信号;

- 一个6pin单排针,可支持PS和PL的各一路UART信号;

- 一组PCIe 4.0 x 8金手指形态的高速接口;

- 金手指供电,也支持外置12V电源供电;

板卡主要由时钟管理模块、FPGA控制模块、DDR存储模块、AD/DA模块、接口配置电路模块及电源管理模块组成。其中,时钟管理模块支持外参考、外同步和外触发功能,提供各种功能模块需要的相应时钟信号;FPGA控制模块通过PS向外部提供1路UART、千兆网口、USB3.0、SATA、JTAG、SD等外设接口,PL向外部提供1路UART接口,1组PCIe 4.0 x 8高速接口,可支持各种数据的交互与控制。

DDR存储模块部分,PS提供一组64bit/4GB的DDR4,PL提供一组32bit/2GB的DDR4,整板一共6GB的板载缓存空间,极大地提高了整个板卡的处理能力。

FPAG集成了数字上下变频,插值,抽取等功能,支持最多8路ADC IN和8路DAC OUT,频率接收范围3M~ 6G,发送最大频率6 G。

接收器当采用单通道模式时,最大采样率为5Gsps,最大接收通道为8个;正交模式时,接收通道为4个,最大采样率为10Gsps,ADC量化位数为14位。

发送器最大采样率为9.85Gsps,八个发送通道,量化位数为14位。配置电路模块支持FPGA程序的在线下载和SPI FLASH的烧写,可以方便用户进行实时多算法处理的在线测试验证。

1688

1688

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?