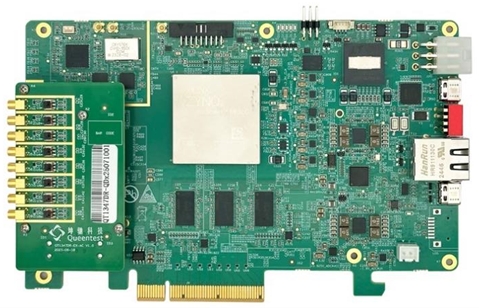

基于RFSOC47DR的射频采集卡,是集ADC、DAC、ARM、FPGA及丰富外设的的软件无线电产品。其分辨率为14bit,AD/DA采样率为5GS/s,支持8个通道采集与播放。提供快速的PCI Express 3.0 x8数据传输接口,可实现5GB/s的传输速率,以实时传输采集数据。板载FPGA具备实时信号处理能力,这些特性使其成为雷达通信、软件无线电等领域信号采集和分析的理想工具。基于RF SOC的软件无线电产品,广泛应用于雷达、软件无线电等领域。

规格

- AD采样率:5GS/s

- DA采样率:5GS/s

- AD/DA分辨率:14bit

- AD/DA通道数:8/8

- 连接器:MMCX

- 耦合方式:AC

- 输入/输出阻抗:50ohm

- 支持外部触发输入

- 支持多个用户自定义扩展IO

- PCIe 4.0 x8统

-

编程语言

Windows10/11

C&C++

软件支持

PCIe 4.0 x8

QT Spectrum Analyzer

9.8 GB/s

采集和播放时钟发生器

- 内部参考时钟输入

使用板载10MHz TCXO作为时钟模块的参考时钟,可以使板卡进行独立的采集工作。

- 外部参考时钟输入

采用外部输入的参考时钟作为时钟模块的参考时钟,默认10MHz,可以使ADC的采样时钟同参考时钟系统同步。

外部同步

通过使用外部同步时钟接口,系统能够避免时钟漂移、相位误差,确保数据的完整性与时序的一致性。预留一路外部同步输入,可以控制数据流的时序,确保数据在适当的时刻被发送和接收。

触发模式:

软件触发、内部脉冲触发、外部脉冲触发、通道触发、预触发、延迟触发。

采集模式:

有限点单次采集、有限点多次采集、无限点多次采集、时间戳.

数据源模式 :

内部DDS播放模式、外部文件播放模式

2258

2258

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?