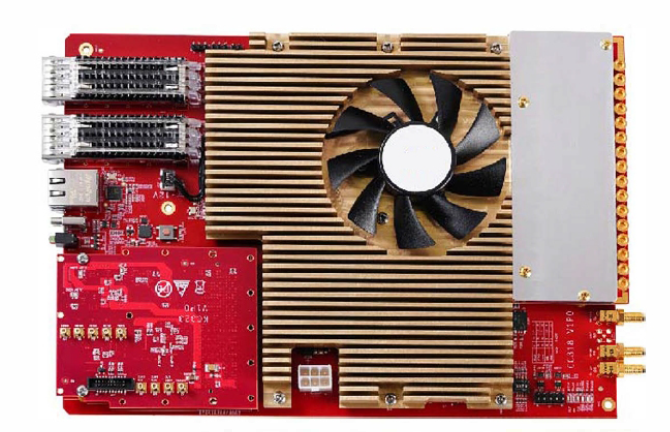

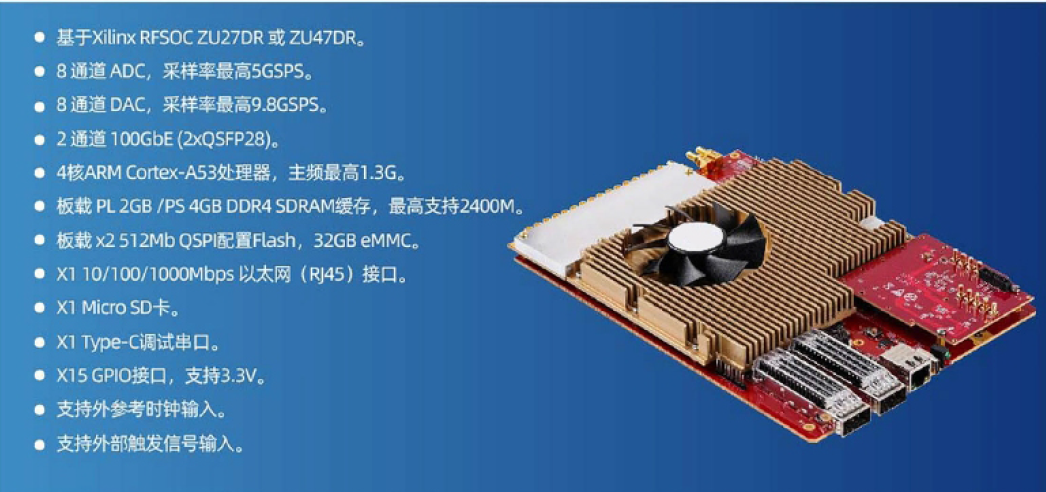

基千Xilinx Zynq UltraScale+ RFSoC主芯片(内部已集成高速ADC和DAC)的高性能板卡,尺寸为167mm *253mm。板卡最大提供8个9.8GSPS 14位DA输出通道与8个SGSPS 14位ADC输入通道。板卡支持外部Sync同步信号输入,外部Refclk参考时钟输入和2个外部Trig触发信号输入,可以完成多板卡同步输入 同步输出和同步采祥功能。除此之外,还提供一个FMC插座,提供PL侧GPIO和PS侧GTR的扩展功能。

网络侧最高支持2路100GbE以太网接口,支持拆分为8x25GbE, 为板卡提供了大带宽的数据

传输。RFSoC PL侧支持2GB DDR4 SDRAM, PS侧支持4GB DDR4 SDRAM。面板侧除100GbE以太网外还提供一个10/100/1000MBASET以太网接口和一个Type-C调试串口。板卡可以从Micro-SD卡启动 QSPI Flash启动 eMMC启动或者由JTAG仿真器动态加载Bit文件件启动。

2185

2185

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?