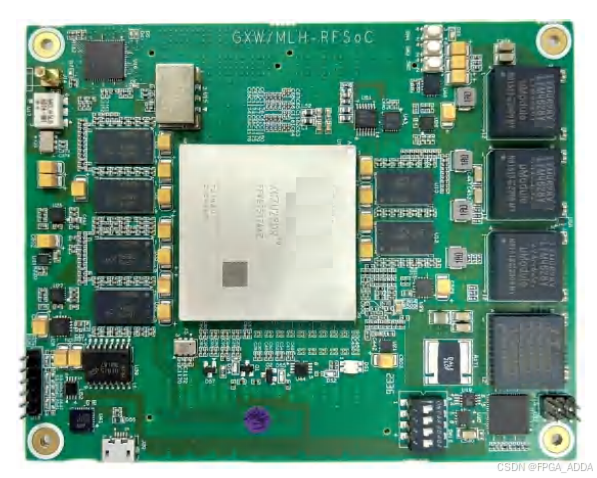

采用FDW复旦微电子FMZQ28DR-RFSoC处理器,兼容Gen1 ZU28/27、Gen3 ZU48/47DR

RFSoC,拥有8个RF-ADC、8个RF-DAC通道。提供完整的应用示例源代码和性能分析工具,

主要用于小尺寸、低功耗、实时处理RF系统的快速集成与应用部署,缩短产品开发周期。

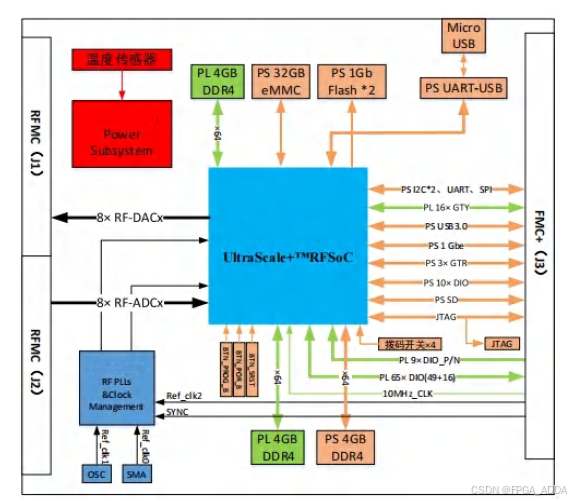

主要技术指标:

- 核心处理器:Gen3 ZU48(47)DR- 2FSVG1517I RFSoC

- 8xADCs, 14-bit up to 5GSPS;

- 8x SD-FEC硬核(47无此硬核)8

- x DACs, 14-bit up to 9.85GSPS;

- RF Input Freq. Max:6GHz;

- Quad-core Arm Cortex-A53 MPCore with CoreSight;

- Dual-core Arm Cortex-R5F with CoreSight;

- PS I/O:支持UART,CAN2.0B,USB2.0,I2C,GigeE10/100/1000,SDIO,SPI 协议;

- 4x PS-GTR:支持PCIe Gen1/2、Serial ATA 3.1、DisplayPort 1.2a、USB 3.0 和SGMII 协议;16x PL-GTY:PCIe Gen4、100G Ethernet、150G Interlaken 等协议;

- 72x PL-GPIO:用户自定义IO;

- 调试接口:JTAG、usb2UART、PMBus;

- 适配Gen1 ZU28(27)DR RFSoC 芯片时,变化参数如下:

- 8x ADCs, 12-bit up to 4.096GSPS

- 8x DACs, 14-bit up to 6.554GSPS

- RF Input Freq. Max:4GHz

- 8x SD-FEC 硬核(27无此硬核)

- 16x PL-GTY:支持PCIe Gen3、100G Ethernet、150G Interlaken 等协议

板载存储:

2 组4GB 64bit DDR4 @ Programmable Logic

32GB eMMC Persistent Storage

4GB 64bit DDR4 @ Processor Subsystem

1Gb QSPI Boot Storage

独立时钟管理网络

超低抖动可编程时钟网络:外部或板载参考100MHz(可更换)可选;

支持板间时钟同步;

33.33MHz@PS、200MHz@PL 独立工作时钟;

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?