时序问题

- 时序逻辑电路中,触发器在时钟上升沿到达时将D复制到输出Q,这个过程称为在时钟沿对D进行采样。

- D在进行采样的时候必须保持稳定

- 类似于拍照片,物体在相机的孔径时间必须保持稳定,如果不稳定,会发生亚稳态现象

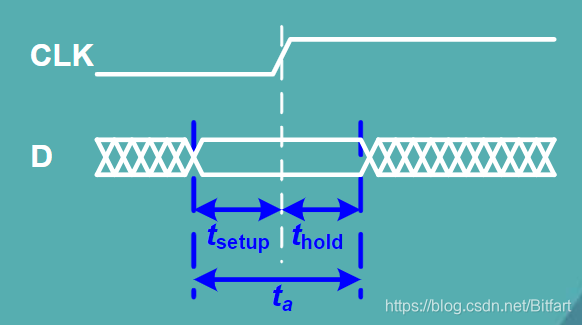

输入时序约束

- 建立时间:tsetup=数据在时钟沿之前必须保持稳定的时间(稳定,即不改变)

- 保持时间:thold=数据在时钟沿之后必须保持稳定的时间

- 孔径时间:t=数据在时钟沿附近必须保持稳定的时间(ta= tsetup + thold)

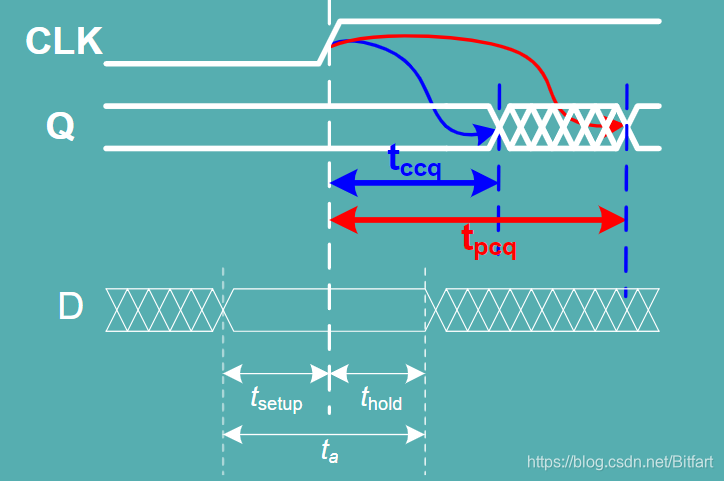

输出时序

- 最小延迟(clock-to-Q contamination delay):tccq=CLK上升沿到输出Q开始改变的时间

- 传播延迟(clock-to-Q propagation delay):tpcq = CLK上升沿到输出Q稳定到最终值的时间(Q不再改变)

动态约束

- 同步时序电路的输入必须在时钟沿附近的孔径时间(建立和保持)保持稳定

- 特别的, 输入必须在如下时间稳定

- 在时钟沿上升之前,输入必须在建立时间tse

本文介绍了时序逻辑电路中的时序问题,包括输入时序约束的建立时间和保持时间,以及输出时序的延迟。强调了在时钟沿附近数据必须保持稳定的重要性,讨论了同步时序电路动态约束的满足条件,并给出了建立时间和保持时间的计算公式。还提及了在实际设计中如何考虑这些约束来确保系统的可靠性。

本文介绍了时序逻辑电路中的时序问题,包括输入时序约束的建立时间和保持时间,以及输出时序的延迟。强调了在时钟沿附近数据必须保持稳定的重要性,讨论了同步时序电路动态约束的满足条件,并给出了建立时间和保持时间的计算公式。还提及了在实际设计中如何考虑这些约束来确保系统的可靠性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?