《FPGA基础知识》系列导航

本专栏专为FPGA新手打造的Xilinx平台入门指南。旨在手把手带你走通从代码、仿真、约束到生成比特流并烧录的全过程。

本篇是该系列的第十七篇内容

上一篇:FPGA基础知识(十六):Xilinx Block Memory IP核完全指南(1)--核心定位与基础配置-优快云博客

下一篇:关注我,第一时间获取更新!!

1 引言

在 FPGA 设计中,Block Memory Generator (BMG) 是一个功能强大的 IP 核,它能够高效地利用 FPGA 内部的 Block RAM 资源构建各种类型的内存结构。今天,我们将深入探讨 Single Port RAM(单端口 RAM) 的三种关键操作模式:No Change(无更改)、Read First(读优先) 和 Write First(写优先)。

2 什么是单端口 RAM

单端口 RAM 是一种只有一个访问端口的内存结构,该端口可用于读取和写入操作。这意味着在同一时刻,只能执行读或写中的一种操作。这种内存适用于许多场景,如处理器暂存 RAM、查找表等。

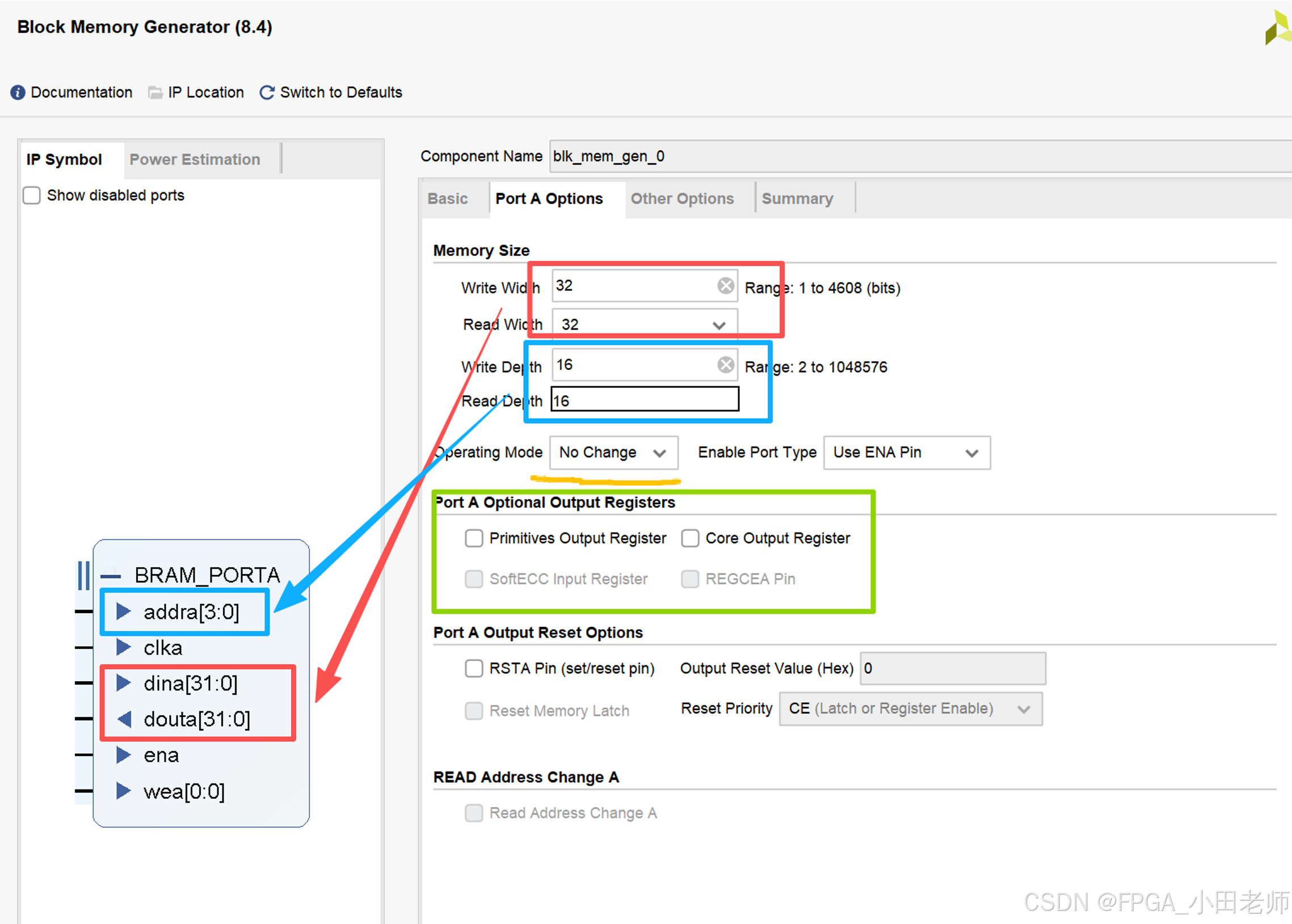

在配置单端口 RAM 时,我们需要关注两个基本参数:

-

Width(宽度):数据的位宽,决定了每次读写操作的数据大小

-

Depth(深度):地址的位宽,决定了内存可以存储多少个数据单元

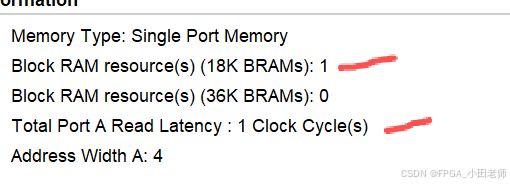

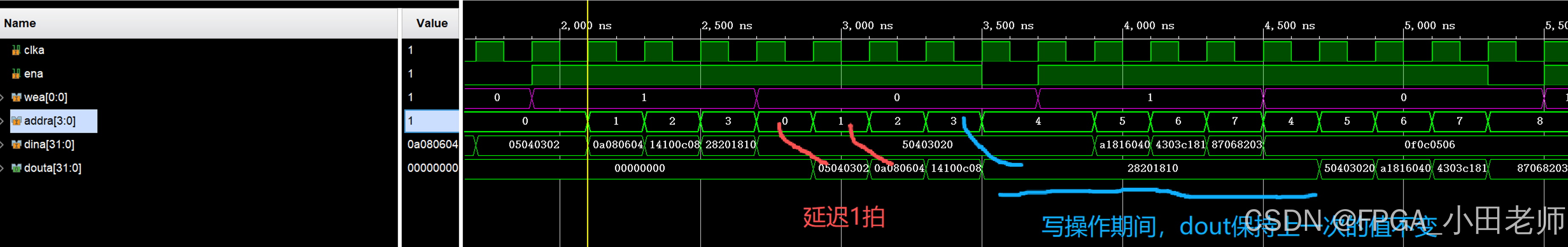

配置消耗一个18Kb的BRAME , 读会有一个周期的延迟(延迟与Port A Option Register有关),我们之后再进行详细说明。

3 三种操作模式的核心区别

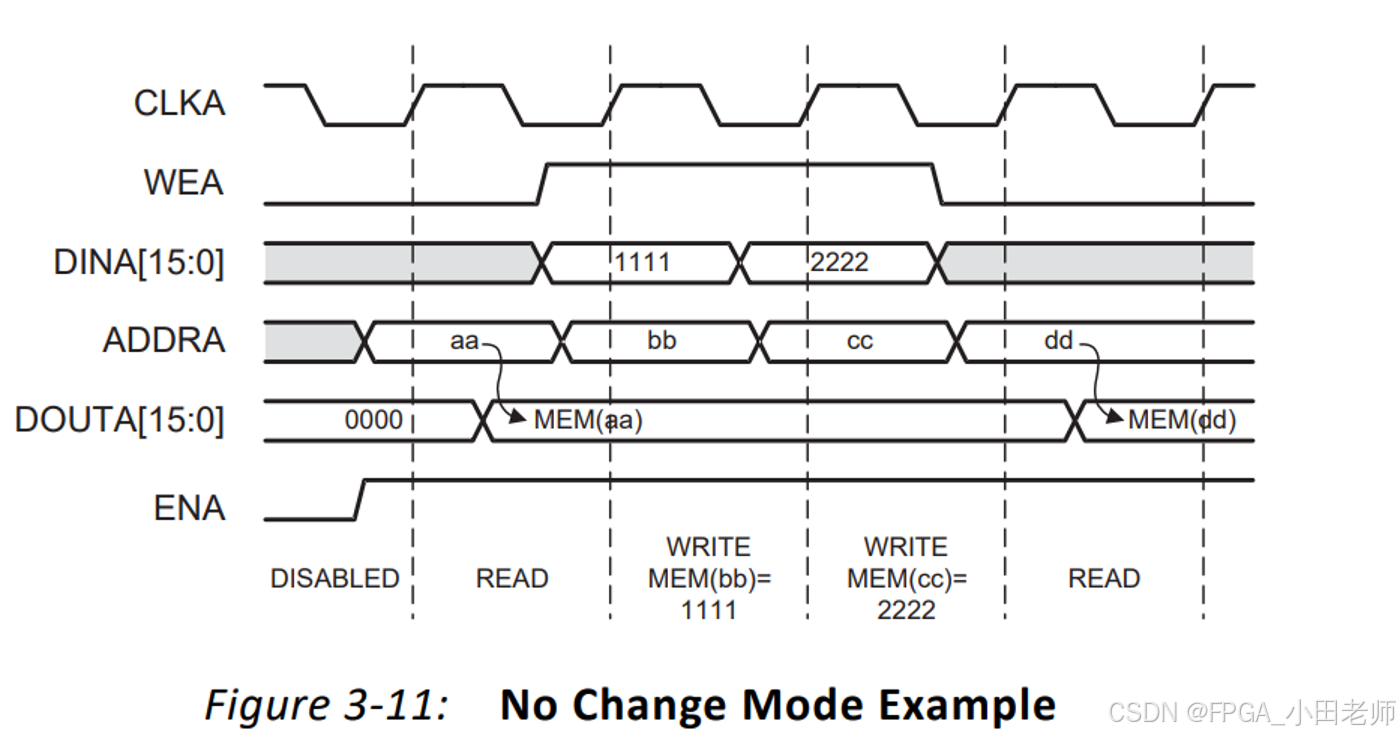

3.1 No Change(无更改)模式

在 No Change 模式下,执行写操作时,数据输出(Dout)保持不变。输出仍然是上一次读取的数据,并且完全不受同一端口上写操作的影响。

工作时序特征:

-

写操作期间,输出端口上的数据不会更新

-

输出始终保持上一次有效读操作的结果

-

只有当执行读操作时,输出才会更新

适用场景:

-

需要保持输出稳定的应用

-

写操作频繁但不需要立即读取新数据的场景

-

作为缓冲区,在特定时刻才读取数据

关键优势:输出稳定性高,不会因写操作而产生数据抖动。

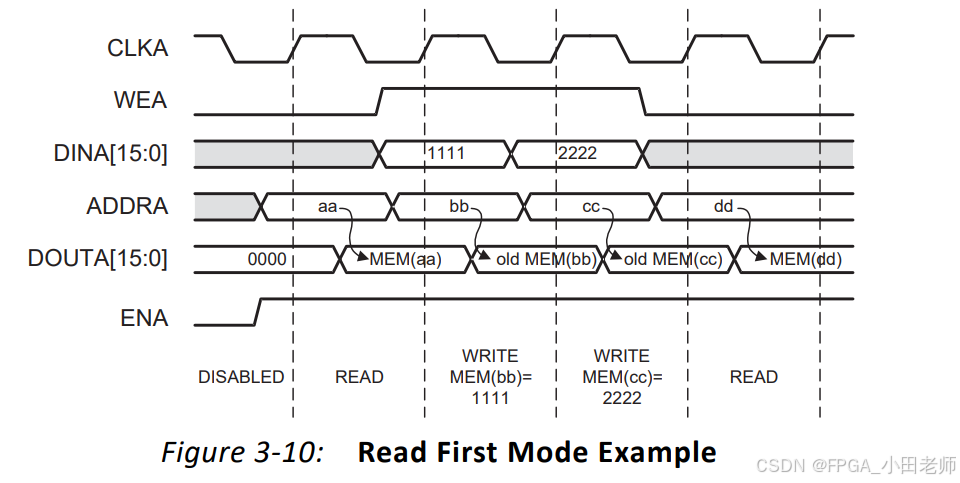

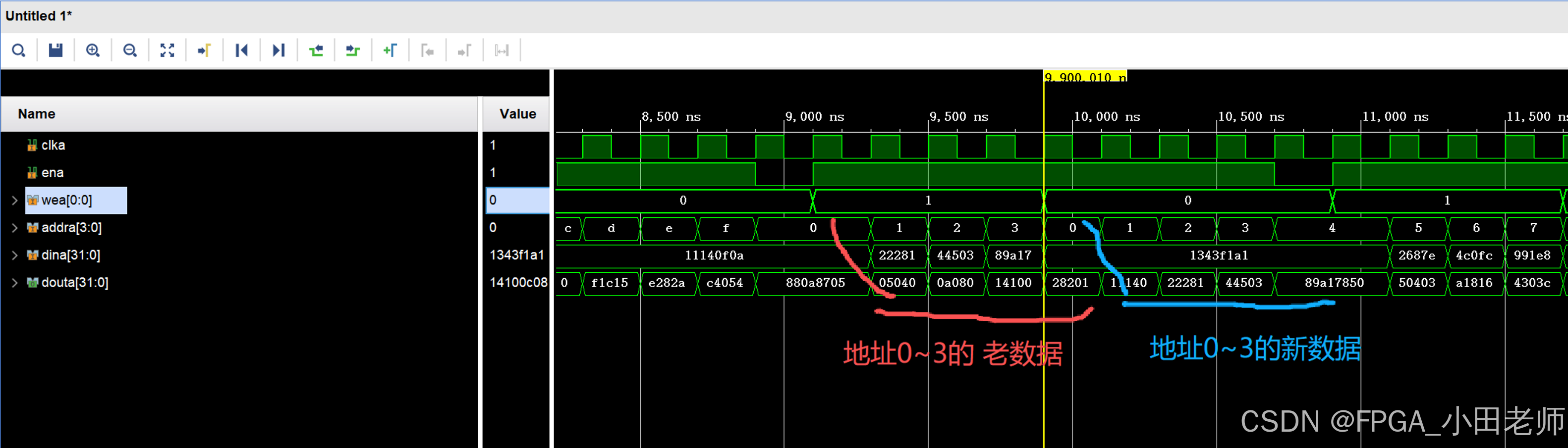

3.2 Read First(读优先)模式

Read First 模式下,执行写操作时,先前存储在写地址处的数据会出现在数据输出端,同时输入数据会被存储到存储器中。这种"先读后写"的行为确保了你总是能看到被覆盖前的旧数据。

工作时序特征:

-

写操作发生时,首先读取该地址的当前值并输出

-

然后才将新数据写入同一地址

-

输出反映了写操作前的内存内容

适用场景:

-

需要记录被覆盖数据的应用

-

实现堆栈或队列等数据结构

-

需要保持数据一致性的系统

关键优势:不会丢失旧数据,提供了数据变更的历史记录。

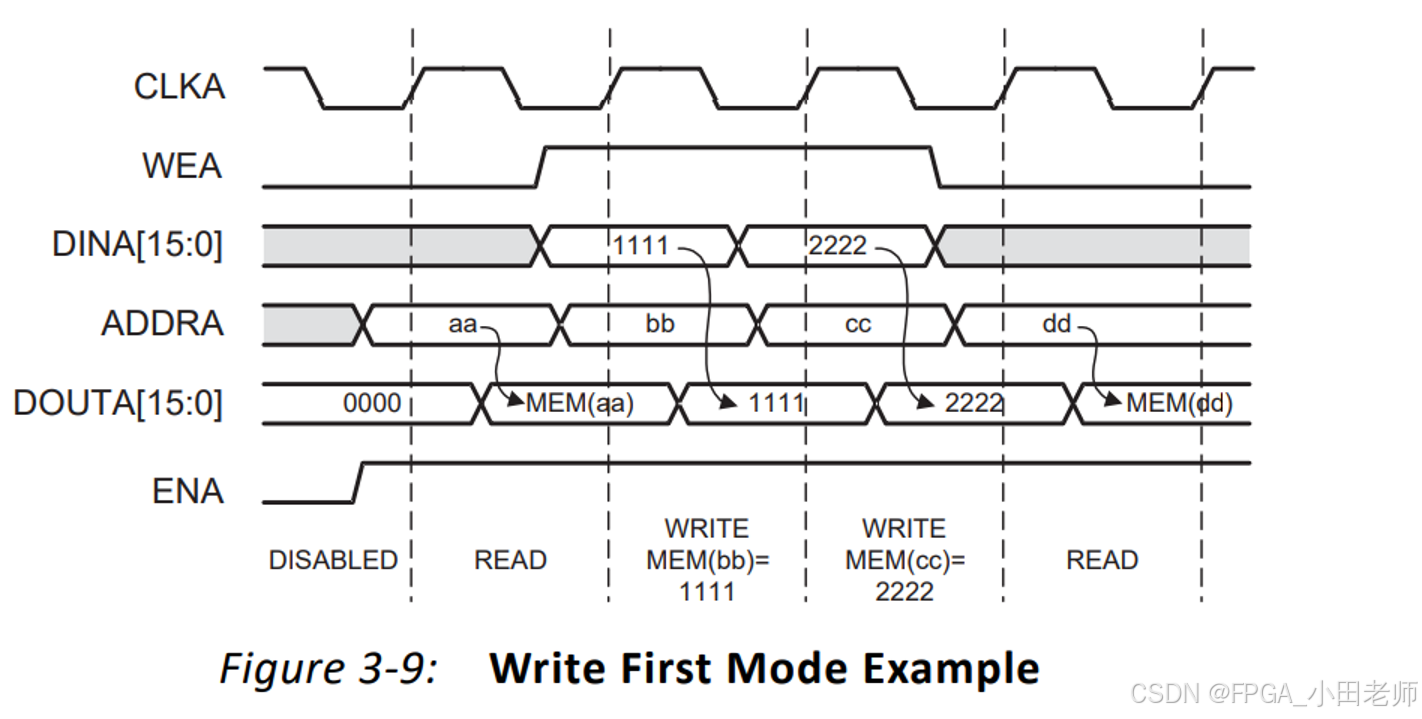

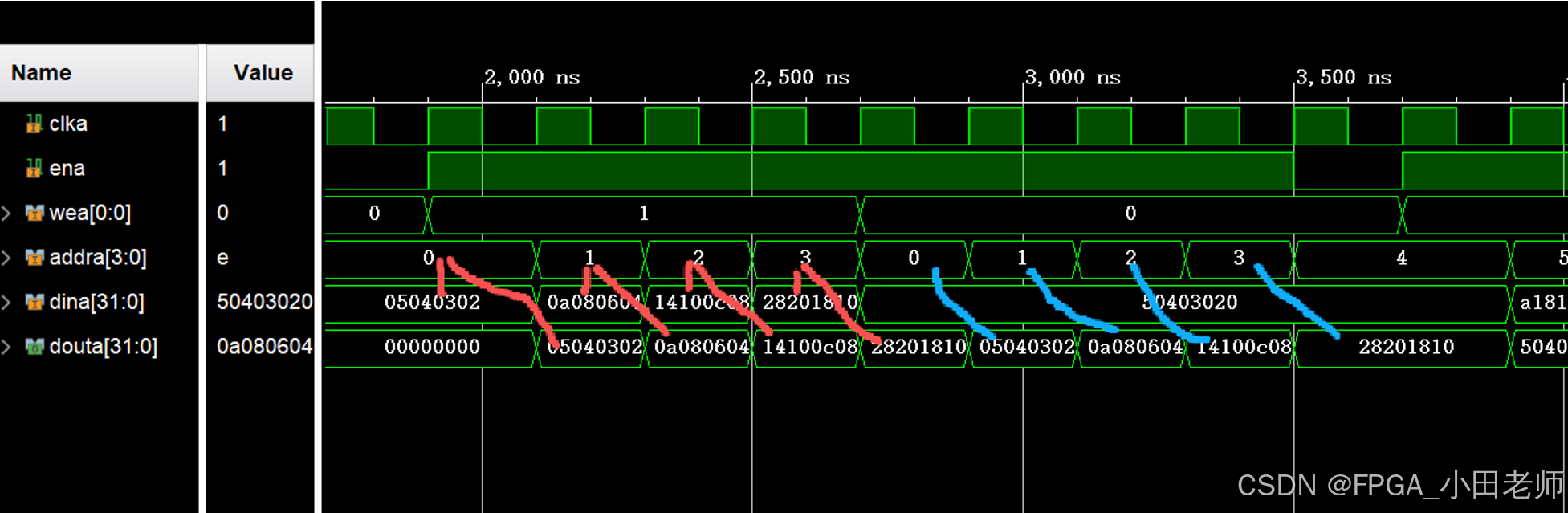

3. Write First(写优先)模式

在 Write First 模式下,输入数据会同时写入存储器并驱动至数据输出端。这是一种透明的传输模式,输出立即反映正在写入的数据。

工作时序特征:

-

写操作发生时,输入数据直接呈现在输出端

-

数据同时被写入内存

-

输出与输入几乎同步(考虑一个时钟周期延迟)

适用场景:

-

需要数据旁路功能的应用

-

实时数据处理流水线

-

实现透明缓冲区

关键优势:提供最低的写操作延迟,输出立即反映写入的数据。

4 重要注意事项:地址映射的理解

请注意一个关键区别:在 Block RAM 中,每个地址对应的是一个完整的数据字(例如 32 位(Data Width)),而在 AXI4 总线协议中,每个地址对应的是 1 个字节(8 位(固定的))。

这意味着:

-

如果你配置了一个 32 位宽的单端口 RAM,地址 0 对应 32 位数据

-

在 AXI4 系统中访问相同的物理内存时,地址 0-3 都映射到这个 32 位数据的四个字节

-

这种差异在系统集成时需要特别注意,确保地址空间正确对齐

5 如何选择合适的操作模式

选择哪种模式取决于你的具体应用需求:

-

选择 No Change 模式:当写操作不应干扰当前输出时,或者当你希望完全控制何时更新输出数据时。

-

选择 Read First 模式:当你需要知道被覆盖的数据是什么时,或者当数据一致性比实时性更重要时。

-

选择 Write First 模式:当需要最低的写延迟,或者希望输出立即反映写入的数据时。

6 总结

Block Memory Generator 的三种操作模式提供了灵活的内存访问策略,可以满足不同应用场景的需求。理解这些模式的细微差别对于设计高效、可靠的 FPGA 系统至关重要。通过正确选择操作模式,并合理配置输出寄存器,你可以在性能、资源和功能之间找到最佳平衡点。

无论你是在设计高性能计算系统、实时信号处理器还是嵌入式控制单元,深入理解这些内存操作模式都将帮助你构建更优秀的 FPGA 设计。

单端口RAM三种操作模式详解

单端口RAM三种操作模式详解

641

641

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?