1 引言

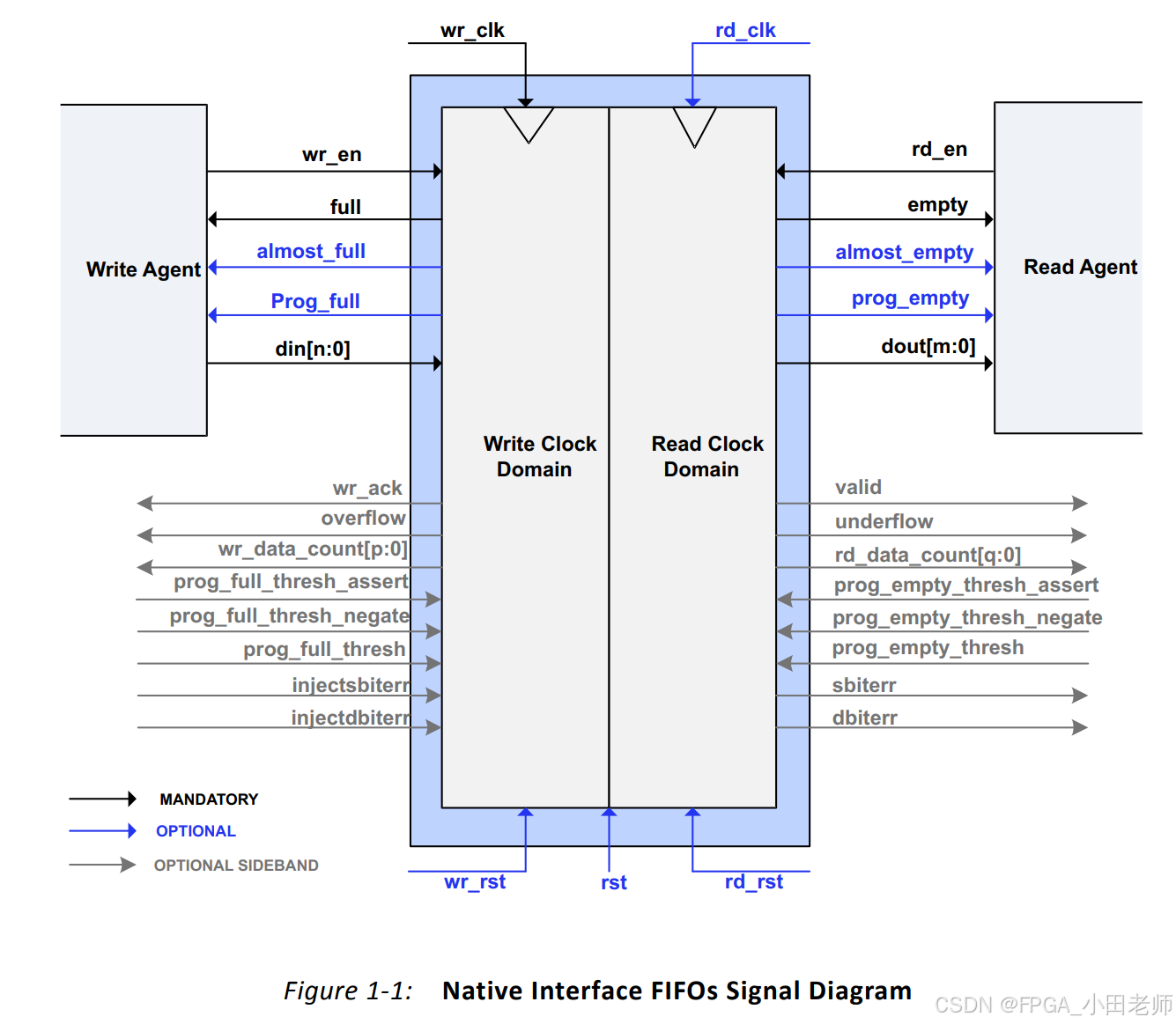

在现代FPGA设计中,FIFO(先进先出)队列是数据流控制的关键组件。Xilinx提供的FIFO Generate IP核是一个经过全面验证的先进先出内存队列,能够实现高性能且面积优化的设计。本文将深入解析该IP核在Native接口模式下的配置方法和特性。

2 FIFO Generate IP核概述

FIFO Generate IP核为所有FIFO配置提供优化解决方案,在使用最少资源的同时实现最高性能(高达500 MHz)。该IP核支持三种接口类型:

-

Native Interface FIFO(本文重点)

-

AXI Memory Mapped Interface FIFO

-

AXI4-Stream Interface FIFO

3 Native接口核心特性

Native接口FIFO具有以下突出特性:

-

数据宽度:1至1024位可配置

-

纵横比:支持对称或非对称(读写端口比率范围1:8到8:1)

-

复位选项:同步或异步复位

-

内存类型:可选块RAM、分布式RAM、移位寄存器或内置FIFO

-

操作模式:标准模式或首字直通(FWFT)模式

-

状态标志:满/空标志、几乎满/几乎空标志

-

高级功能:可编程状态标志、握手信号、ECC错误校正

4 IP核配置详解

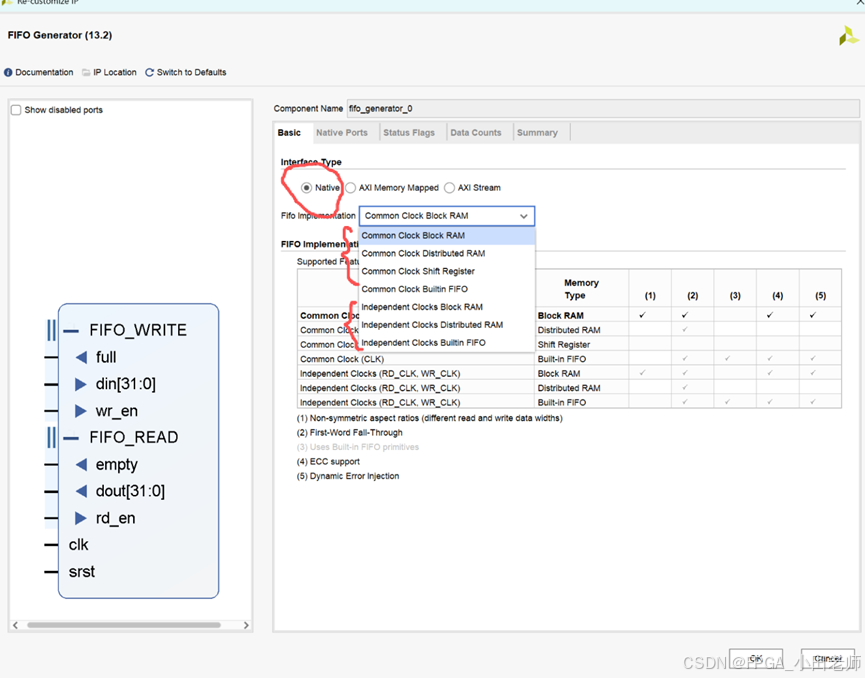

4.1 Basic页面配置

在Basic页面中,首先需要选择时钟域类型:

4.1.1 时钟域类型

公共时钟(Common Clock)

-

读写操作使用同一时钟

-

时序简单,资源消耗较少

独立时钟(Independent Clock)

-

读写使用不同的时钟(rd_clk和wr_clk)

-

适用于跨时钟域数据传输

-

需要同步电路,资源消耗稍多

4.1.2 FIFO实现方式选择

根据应用需求,可选择四种不同的实现方式,实现方式对比表如下,关于这四种实现方式的详细描述见:Xilinx FIFO Generate IP核(2):四种实现方式详解--从资源消耗到应用场景-优快云博客

| 实现方式 | 存储资源 | 逻辑资源 | 最大频率 | 功耗 | 典型应用场景 |

|---|---|---|---|---|---|

| Block RAM | 专用BRAM | 少 | 高 | 低 | 大数据量缓冲 |

| Distributed RAM | LUT | 多 | 中 | 中 | 小容量、灵活配置 |

| Shift Register | SRL32E | 少 | 高 | 低 | 固定延迟线、小深度 |

| Built-in FIFO | 专用硬件 | 极少 | 最高 | 最低 | 高速接口、硬核功能 |

4.1.2.1 Block RAM (BRAM) FIFO

-

资源特性:使用专用Block RAM块,逻辑资源消耗少

-

性能指标:频率450-550MHz,延迟2-3周期

-

适用场景:深度较大(>256)的FIFO

4.1.2.2 Distributed RAM FIFO

-

资源特性:使用CLB中的LUT作为存储,配置灵活

-

性能指标:频率300-400MHz,延迟1-2周期

-

适用场景:小容量(深度≤64)FIFO

4.1.2.3 Shift Register FIFO

-

资源特性:基于SRL32E移位寄存器,资源效率高

-

性能指标:频率500-600MHz,固定延迟

-

适用场景:固定延迟需求的应用

4.1.2.4 Built-in FIFO

-

资源特性:硬核实现,几乎不消耗逻辑资源

-

性能指标:可达I/O最高频率,极低延迟

-

适用场景:最高性能要求的场景

4.1.2.5 选择策略指南

基于容量需求的选择:

-

深度 > 256:推荐Block RAM(资源效率高)

-

深度 ≤ 64:考虑Distributed RAM(避免BRAM浪费)

-

固定延迟:选择Shift Register(性能最佳)

-

高速接口:使用Built-in FIFO(性能最优)

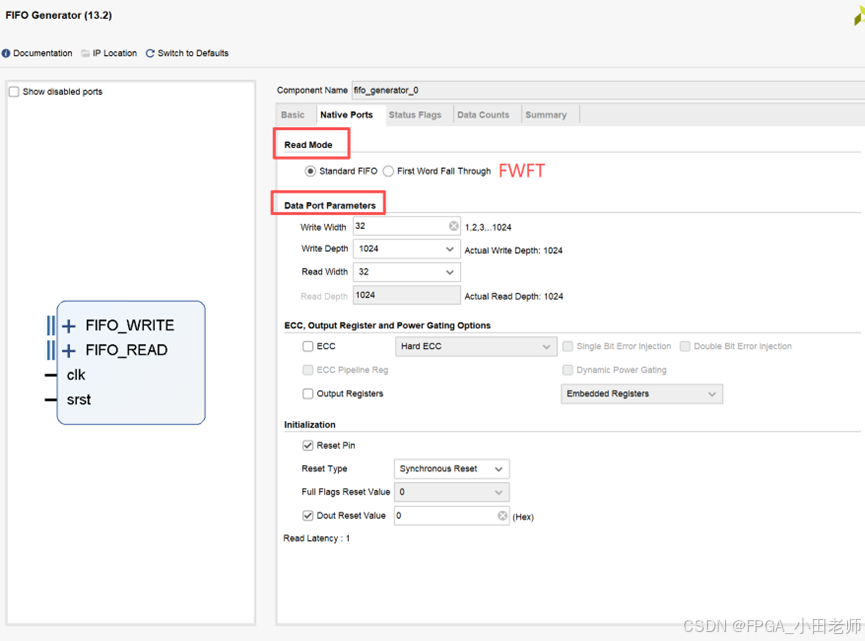

4.2 Native Port页面配置

4.2.1 读模式选择

关于FIFO读模式详解见:Xilinx FIFO Generate IP核(3):读模式详解--标准FIFO vs FWFT模式-优快云博客

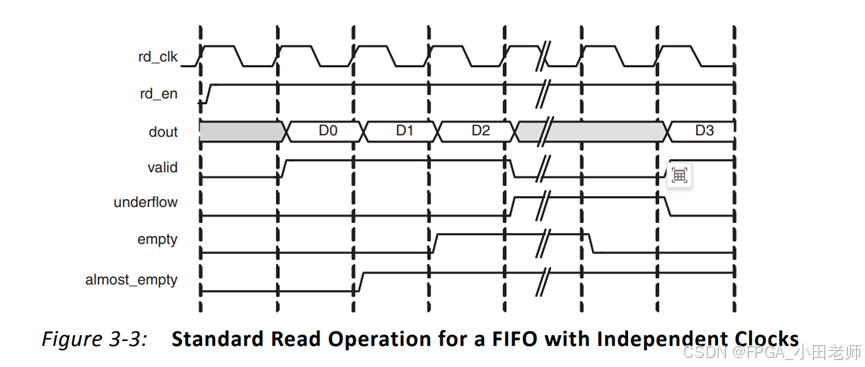

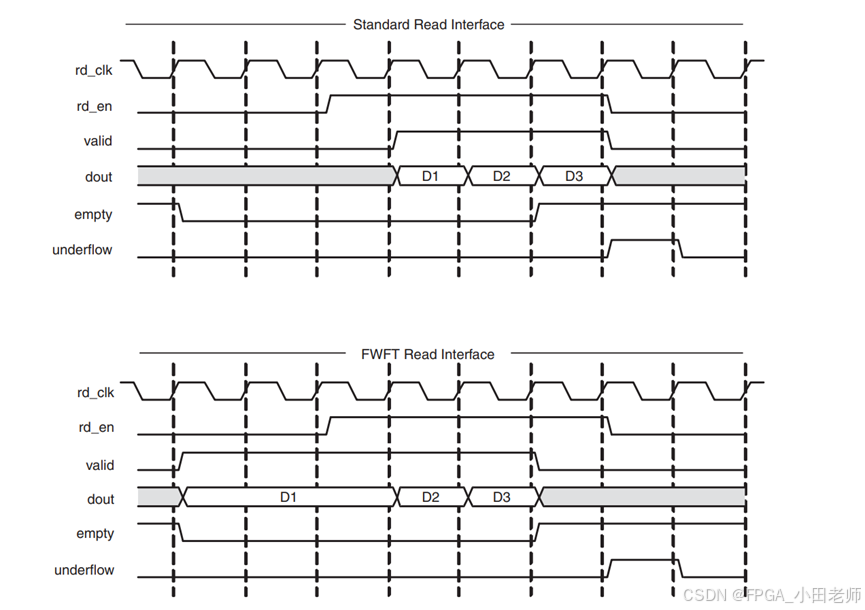

4.2.1.1 标准FIFO模式

-

数据在rd_en有效后出现在输出端口

-

需要先判断empty信号再发出读使能

-

至少1个时钟周期的读取延迟

标准FIFO模式时序

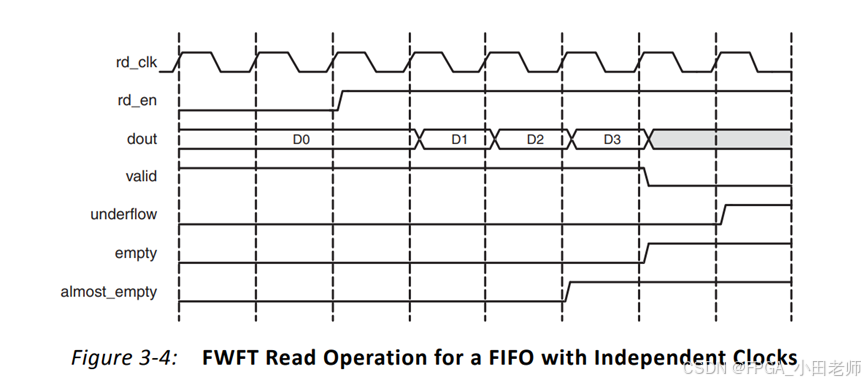

4.2.1.2 FWFT模式(首字直通)

-

数据写入后自动出现在输出端口(FIFO非空时)

-

零延迟读取,数据立即可用

-

通过rd_en确认数据消费

FWFT模式的时序

4.2.1.3 模式选择建议:

-

需要低延迟:选择FWFT模式

-

传统FIFO操作:选择标准模式

4.2.2 数据端口参数

-

Write Width:写数据位宽(1-1024位)

-

Write Depth:写深度配置

-

Read Width:读数据位宽(1-1024位)

-

Read Depth:读深度配置

支持非对称配置,读写位宽比率范围1:8到8:1。

4.2.3 高级选项

详细说明参考:

Xilinx FIFO Generate IP核(4):ECC、输出寄存器与电源门控详解-优快云博客

4.2.3.1 ECC(错误校正码)

-

检测和纠正存储器中的数据错误

-

保护Block RAM中的数据免受软错误影响

4.2.3.2 输出寄存器

-

改善输出路径时序

-

增加固定延迟但提高时序余量

4.2.3.3 电源门控

-

降低静态功耗的技术

-

在电路空闲时切断电源

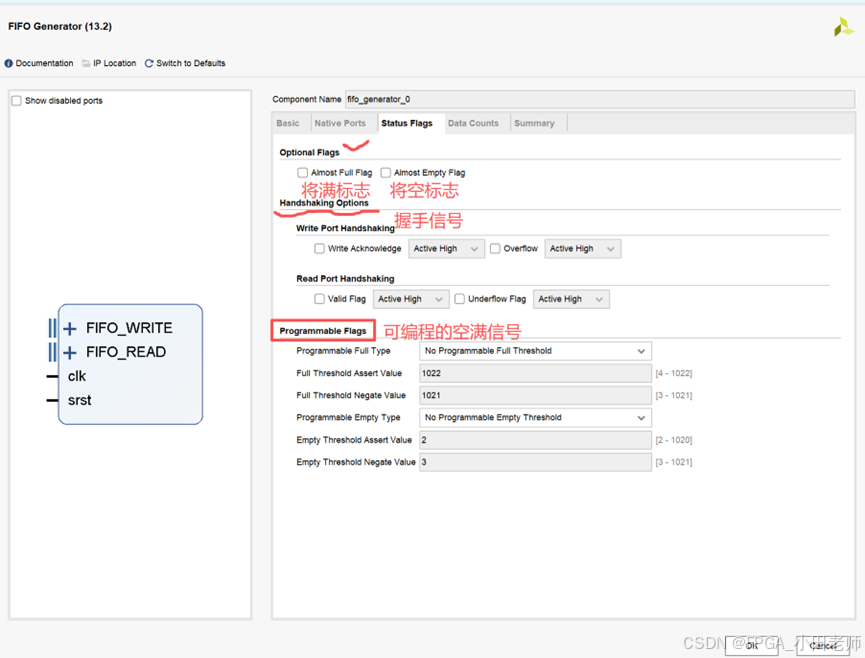

4.3 Status Flags页面配置

4.3.1 基本状态标志

-

full:FIFO已满,不可写入

-

empty:FIFO已空,不可读取

4.3.2 扩展状态标志

Almost Full Flag

-

再写一笔数据FIFO将满

-

高电平有效,与写时钟同步

Almost Empty Flag

-

再读一笔数据FIFO将空

-

高电平有效,与读时钟同步

4.3.3 可编程标志

提供多种可编程阈值配置:

-

无编程功能(No Programmable Full/empty Threshold):使用固定阈值

-

单常数阈值(Single Programmable Full/empty Threshold Constant):通过参数设置阈值,例如:在Full Threshold Assert Value里面输入Full的阈值,比如1022,即当fifo中数据超过1022时,prog_full拉高,低于1022时prog_full拉低

-

双常数阈值(Multiple Programmable Full/empty Threshold Constant):分别设置触发和取消触发的阈值,例如:在Full Threshold Assert Value和Full Threshold Negate Value里面分别输入Full的阈值,比如Full Threshold Assert Value为1022,Full Threshold Negate Value为1000,即当fifo中数据超过1022时,prog_full拉高,低于1000时prog_full拉低。

-

单输入端口(Single Programmable Full/empty Threshold Input Port):通过外部信号动态设置阈值,例如:从外部端口prog_full_thresh输入full的阈值,比如1022,即当fifo中数据超过1022时,prog_full拉高,低于1022时prog_full拉低。

-

双输入端口(Multiple Programmable Full/empty Threshold Input Port):外部信号分别控制触发和取消触发的阈值,例如:从外部端口prog_full_thresh_Assert和prog_full_thresh_Negate分别输入full的阈值。比如prog_full_thresh_Assert为1022,prog_full_thresh_Negate为1000,即当fifo中数据超过1022时,prog_full拉高,低于1000时prog_full拉低。

4.3.4 握手信号

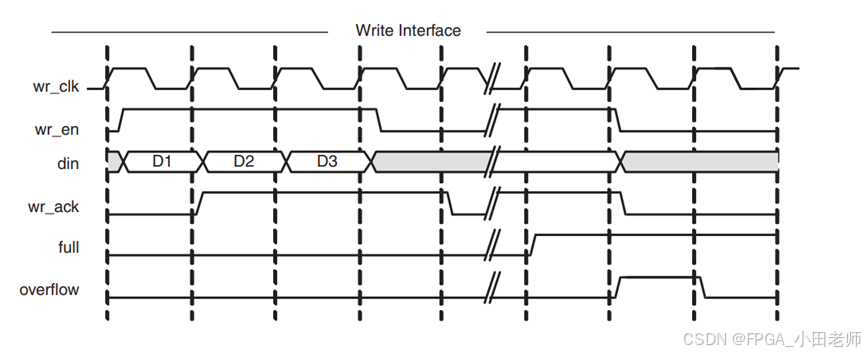

4.3.4.1 写握手:

-

wr_ack:成功写入确认

-

overflow:FIFO已满时继续写入触发

当成功写一笔数据后,wr_ack拉高,当full拉高之后还是在写数据,便会触发Overflow。

4.3.4.2 读握手:

-

valid:读数据有效标志

-

underflow:FIFO已空时继续读取触发

Valid信号始终与读数据保持同步,在通用fifo模式下,当收到rd_en之后,拉起valid信号,同时给出读数据,在FWFT模式下,非空的时候,valid和读数据同时准备好,当rd_en拉起的时候,直接就返回数据。

当empty的时候,还是发起了读使能,此时Underflow拉高,即读不到数据了。

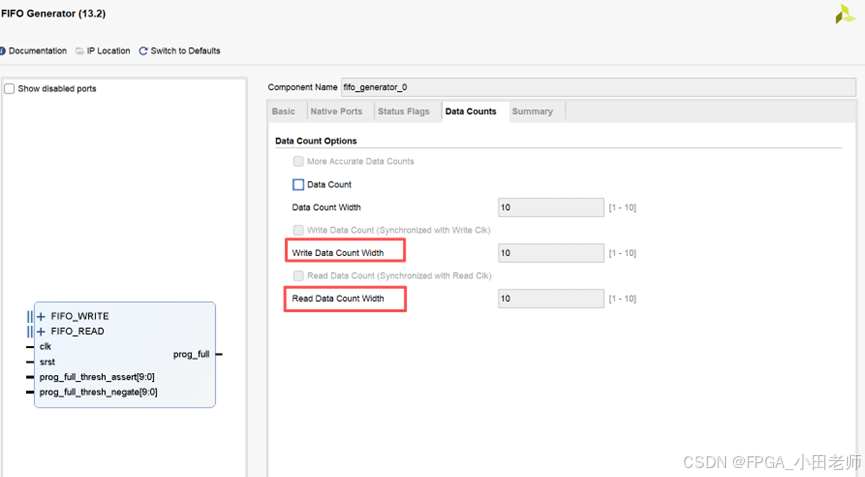

4.4 Data Counts页面

提供读写数据计数功能:

-

wr_data_count:写入数据计数

-

rd_data_count:读取数据计数

注意:输出计数可能存在一定延迟,适合参考使用但不建议用于精确控制。

5 配置建议总结

-

默认选择:Block RAM FIFO(性能与资源平衡)

-

小容量需求:Distributed RAM FIFO(配置灵活)

-

低延迟需求:Shift Register FIFO或FWFT模式

-

最高性能:Built-in FIFO(硬核优化)

-

时序考虑:添加输出寄存器改善时序

-

功耗优化:Built-in FIFO > Shift Register > Block RAM > Distributed RAM

结语

FIFO Generate IP核的Native接口提供了丰富灵活的配置选项,能够满足各种应用场景的需求。通过合理选择FIFO类型、读模式和状态标志,可以在资源消耗、性能和功能之间达到最佳平衡。在实际设计中,建议根据具体的数据流量、时序要求和资源约束进行针对性配置。

在后续文章中,我们将深入探讨FIFO Generate IP核的其他接口模式以及在实际工程中的应用实例。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?