1.SPI和I2C的区别

-

SPI和I2C的设计目的都是实现主控芯片和各种外挂芯片之间的数据交流

-

I2C的优点:I2C可以在消耗最低硬件资源的情况下,实现最多的功能。在硬件上,无论挂载多少个设备,都只需要两根通信线;在软件上,数据双向通信、应答位都可以实现。如果把通信协议比作是一个人的话,那I2C就属于精打细算、思维灵活这类型的人

-

I2C的缺点:由于I2C开漏外加上拉电阻的电路结构,使得通信线高电平的驱动能力比较弱,这就会导致通信线由低电平变到高电平的时候,这个上升沿耗时比较长,这会限制I2C的最大通信速度。所以I2C的标准模式只有100KHz的时钟频率,I2C的快速模式也只有400KHz的时钟频率

-

SPI的优点:SPI传输更快,SPI协议并没有严格规定最大传输速度,这个最大传输速度取决于芯片厂商的设计需求;SPI的设计比较简单,实现的功能没有I2C那么多

-

SPI的缺点:SP的硬件开销比较大,通信线的个数比较多,并且通信过程中,经常会出现资源浪费的现象。如果把通信协议比作是一个人的话,那SPI就属于富家子弟、有钱任性这类型的人

2.SPI介绍

1)简介

-

SPI (Serial Peripheral Interface)是由Motorola公司开发的一种通用数据总线

-

四根通信线:SCK(Serial Clock)串行时钟线、MOSl(Master Output Slave Input)主机输出从机输入、MISO (Master Input Slave Output)主机输入从机输出、SS (Slave Select)从机选择

-

SPI无应答机制设计

-

同步,全双工

-

支持总线挂载多设备(一主多从)不支持多主多从

2)硬件电路

-

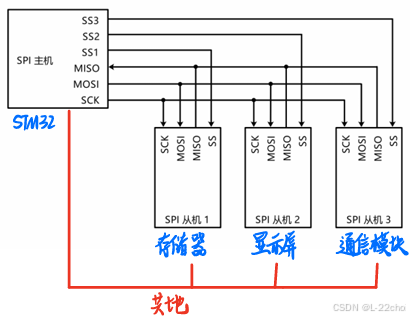

所有SPI设备的SCK、MOSl、MISO分别连在一起,数据传输方向如图

-

主机另外引出多条SS控制线,分别接到各从机的SS引脚

-

主机的SS线都是输出,从机的SS线都是输入,SS线低电平有效,从而进行通信

-

-

输出引脚配置为推挽输出,输入引脚配置为浮空或上拉输入

-

当从机的SS引脚为高电平时,MISO引脚必须切换成高阻态,相当MISO引脚断开不输出任何电平,这样就可以防止一条线有多个输出而导致电平冲突的问题;当从机的SS引脚为低电平时,MISO引脚才配置为推挽输出

-

3)移位示意图(核心)

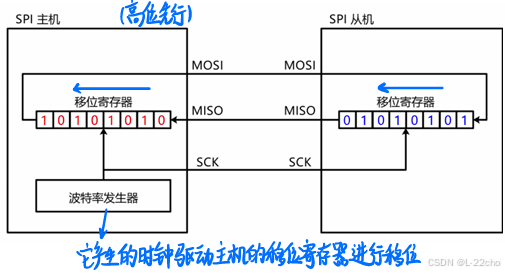

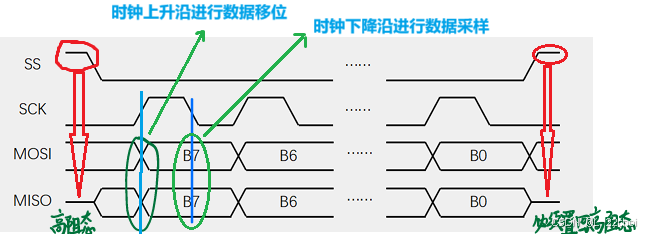

波特率发生器产生时钟,当时钟上升沿到来时,主机从机的移位寄存器都会左移一位,被移出去的位就会放在引脚上,时钟下降沿到来时,就会采样引脚上的数据输入到移位寄存器的最低位,这就完成了SPI字节交换的时序流程

4)SPI的时序基本单元

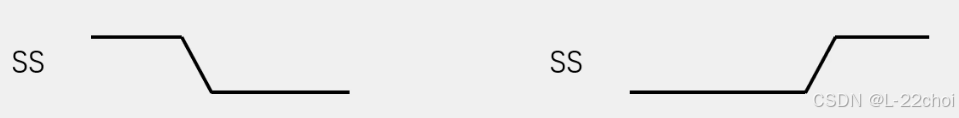

起始条件:SS从高电平切换到低电平

终止条件:SS从低电平切换到高电平

-

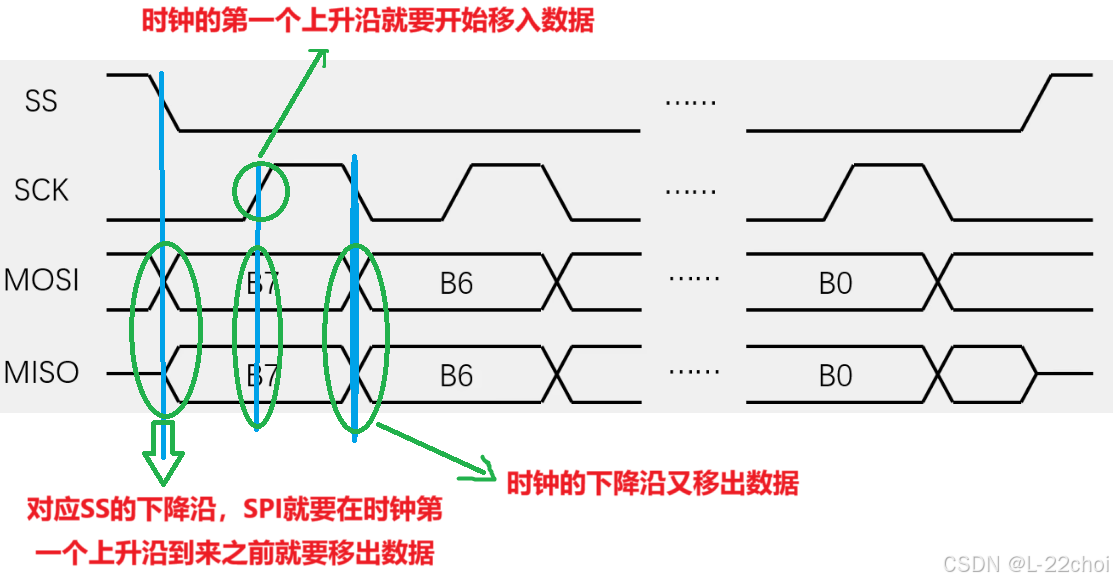

交换一个字节(模式0)【重点掌握模式0】

-

时钟极性 CPOL=0:空闲状态时,SCK为低电平

-

时钟相位 CPHA=O:SCK第一个边沿移入数据,第二个边沿移出数据

-

-

交换一个字节(模式1)

模式0和模式1的区别:模式0把数据变化的时机给提前了

-

CPOL=0:空闲状态时,SCK为低电平

-

CPHA=1:SCK第一个边沿移出数据,第二个边沿移入数据

-

5)SPI时序

-

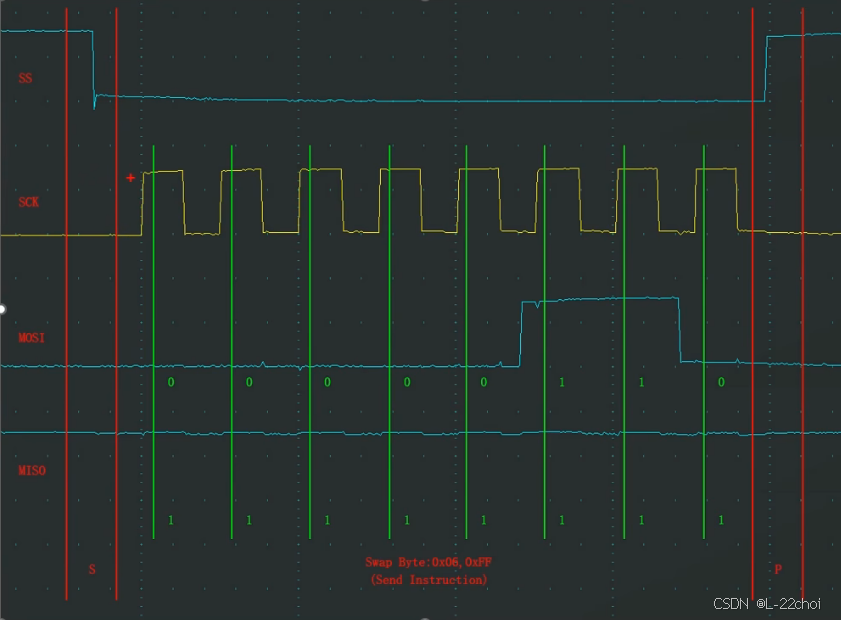

发送指令

-

向SS指定的设备,发送指令(0x06)写使能

-

-

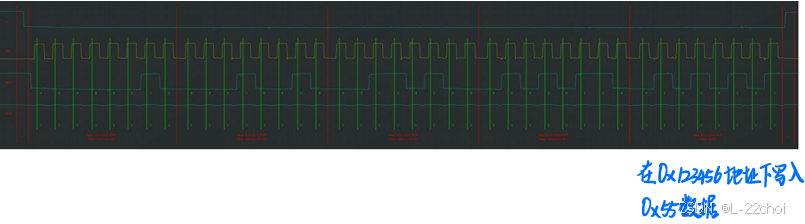

指定地址写

-

向SS指定的设备,发送写指令(0x02)

-

随后在指定地址(Address[23:0])下,写入指定数据(Data)

-

-

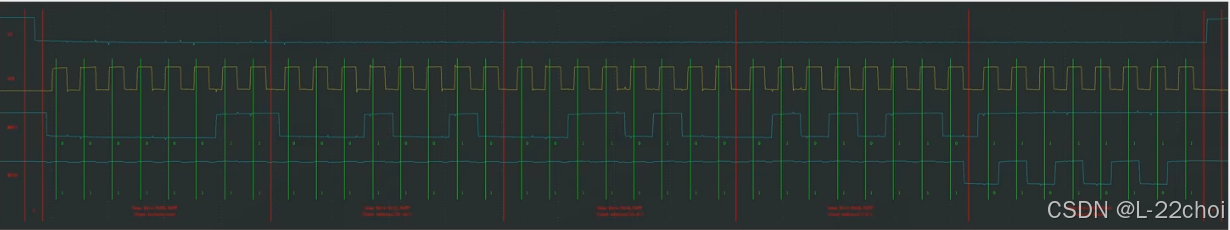

指定地址读

-

向SS指定的设备,发送读指令(0x03)

-

随后在指定地址(Address[23:0])下,读取从机数据(Data)

-

3.STM32的SPI外设介绍

1)SPI外设简介

-

STM32内部集成了硬件SP收发电路,可以由硬件自动执行时钟生成数据收发等功能,减轻CPU的负担

-

可配置8位/16位数据帧、高位先行/低位先行

-

时钟频率:fPCLK/(2,4,8,16,32,64,128,256)

-

支持多主机模型、主或从操作

-

可精简为半双工/单工通信

-

支持DMA

-

兼容I2S协议(数字音频信号传输的专用协议)

-

STM32F103C8T6硬件SPI资源:SPI1、SPI2

-

SPI1挂载在APB2上,PCLK=72MHz;SPI2挂载在APB1上,PCLK=36MHz

-

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3042

3042

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?