目录

一、前言

在时序约束中对clock的约束还存在一种特殊的延时约束set external delay。set external delay如字面含义,设置外部的时延值,但这个外部时延主要是指反馈时延,即信号从FPGA的output端口输出后经过外部电路回到输入端口的时延值。

二、约束用法

2.1 设置界面

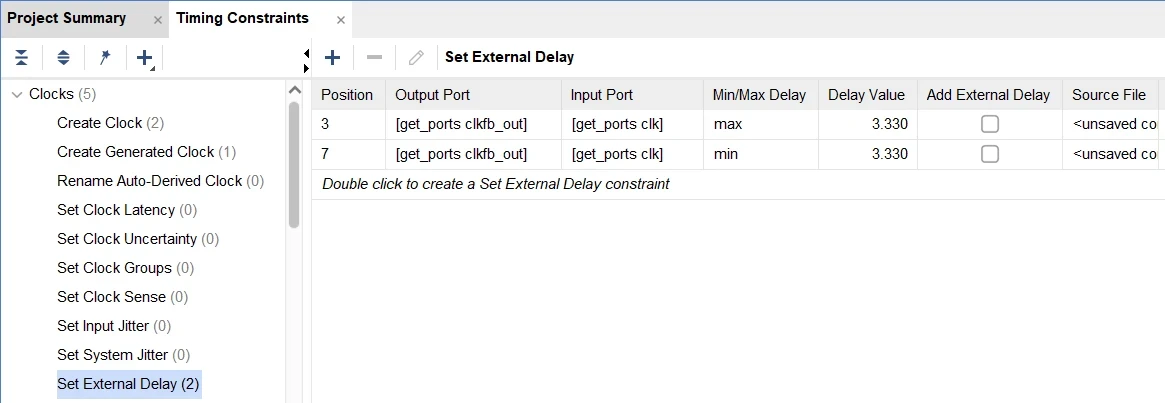

进入Timing Constraints界面,在左侧Clock栏中选中Set External Delay,右侧即显示Set External Delay

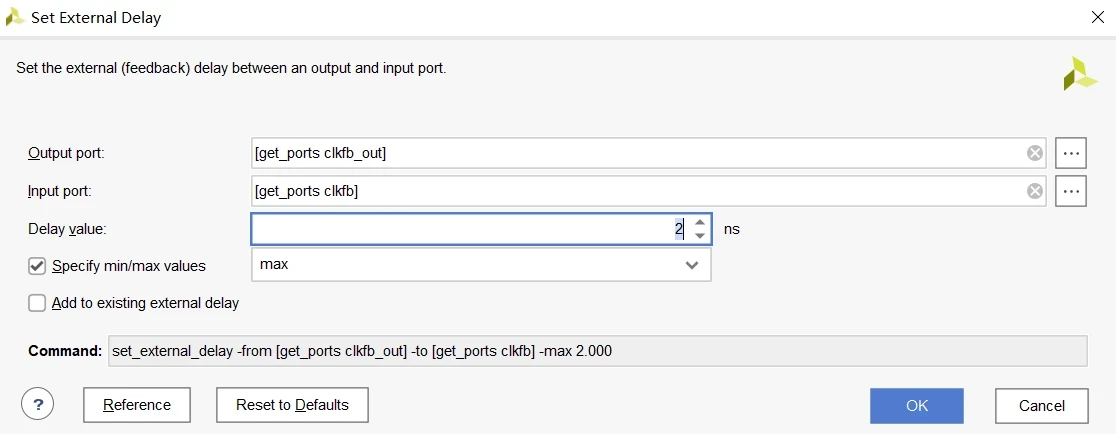

设置界面中需设置反馈路径中的输出端口output port和输入端口input port,delay value为设置的时延值。勾选“Specify min/max values”后可设置max和min,即指进行setup或hold分析,“Add to existing external delay”勾选后对于约束的端口如果存在其他的外部时延约束,则会将其覆盖。

2.2 命令语法

命令格式

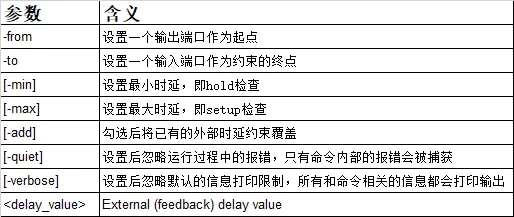

set_external_delay ‑from <args> ‑to <args> [‑min] [‑max] [‑add] [‑quiet] [‑verbose] <delay_value>参数含义

三、示例代码

3.1 工程示例

module set_external_delay(CLKIN1,CLKIN2,CLKINSEL,CLKFBIN,CLKFBOUT,rst,d,S,ff_clkout0_a,ff_clkout0_b);

input CLKIN1,CLKIN2,CLKINSEL,CLKFBIN,rst,d,S;

output reg ff_clkout0_a,ff_clkout0_b;

output CLKFBOUT;

reg ff_clkout0;

PLLE2_ADV #(

.BANDWIDTH("OPTIMIZED"), // OPTIMIZED, HIGH, LOW

.CLKFBOUT_MULT(8), // Multiply value for all CLKOUT, (2-64)

.CLKFBOUT_PHASE(90.0), // Phase offset in degrees of CLKFB, (-360.000-360.000).

// CLKIN_PERIOD: Input clock period in nS to ps resolution (i.e. 33.333 is 30 MHz).

.CLKIN1_PERIOD(0.0),

.CLKIN2_PERIOD(0.0),

// CLKOUT0_DIVIDE - CLKOUT5_DIVIDE: Divide amount for CLKOUT (1-128)

.CLKOUT0_DIVIDE(1),

.CLKOUT1_DIVIDE(2),

.CLKOUT2_DIVIDE(4),

// CLKOUT0_DUTY_CYCLE - CLKOUT5_DUTY_CYCLE: Duty cycle for CLKOUT outputs (0.001-0.999).

.CLKOUT0_DUTY_CYCLE(0.4),

.CLKOUT1_DUTY_CYCLE(0.5),

.CLKOUT2_DUTY_CYCLE(0.5),

// CLKOUT0_PHASE - CLKOUT5_PHASE: Phase offset for CLKOUT outputs (-360.000-360.000).

.CLKOUT0_PHASE(0.0),

.CLKOUT1_PHASE(0.0),

.CLKOUT2_PHASE(0.0),

.COMPENSATION("EXTERNAL"), // ZHOLD, BUF_IN, EXTERNAL, INTERNAL

.DIVCLK_DIVIDE(1), // Master division value (1-56)

// REF_JITTER: Reference input jitter in UI (0.000-0.999).

.REF_JITTER1(0.0),

.REF_JITTER2(0.0),

.STARTUP_WAIT("FALSE") // Delay DONE until PLL Locks, ("TRUE"/"FALSE")

)

PLLE2_ADV_inst (

// Clock Outputs: 1-bit (each) output: User configurable clock outputs

.CLKOUT0(CLKOUT0), // 1-bit output: CLKOUT0

.CLKOUT1(CLKOUT1), // 1-bit output: CLKOUT1

.CLKOUT2(CLKOUT2), // 1-bit output: CLKOUT2

// Feedback Clocks: 1-bit (each) output: Clock feedback ports

.CLKFBOUT(CLKFBOUT), // 1-bit output: Feedback clock

// Clock Inputs: 1-bit (each) input: Clock inputs

.CLKIN1(CLKIN1), // 1-bit input: Primary clock

.CLKIN2(CLKIN2), // 1-bit input: Secondary clock

// Control Ports: 1-bit (each) input: PLL control ports

.CLKINSEL(CLKINSEL), // 1-bit input: Clock select, High=CLKIN1 Low=CLKIN2

.RST(rst), // 1-bit input: Reset

// Feedback Clocks: 1-bit (each) input: Clock feedback ports

.CLKFBIN(CLKFBIN) // 1-bit input: Feedback clock

);

// End of PLLE2_ADV_inst instantiation

always@(posedge CLKOUT0,negedge rst)

if(!rst)

ff_clkout0<=1'b0;

else begin

ff_clkout0<=d;

end

always@(posedge CLKOUT0,negedge rst)

if(!rst)

ff_clkout0_a<=1'b0;

else begin

ff_clkout0_a<=ff_clkout0;

end

always@(posedge CLKOUT1,negedge rst)

if(!rst)

ff_clkout0_b<=1'b0;

else begin

ff_clkout0_b<=ff_clkout0;

end

endmodule 3.2 时序约束

create_clock -period 10.000 -name clkin1 -waveform {0.000 5.000} [get_ports CLKIN1]

create_clock -period 8.000 -name clkin2 -waveform {0.000 4.000} [get_ports CLKIN2]

create_generated_clock -name gen_clkout0 -source [get_ports CLKIN1] -multiply_by 2 -add -master_clock clkin1 [get_pins PLLE2_ADV_inst/CLKOUT0]

set_external_delay -from [get_ports CLKFBOUT] -to [get_ports CLKFBIN] 1.181

set_input_delay -clock [get_clocks clkin1] 0.222 [get_ports {d rst}]3.3 时序报告

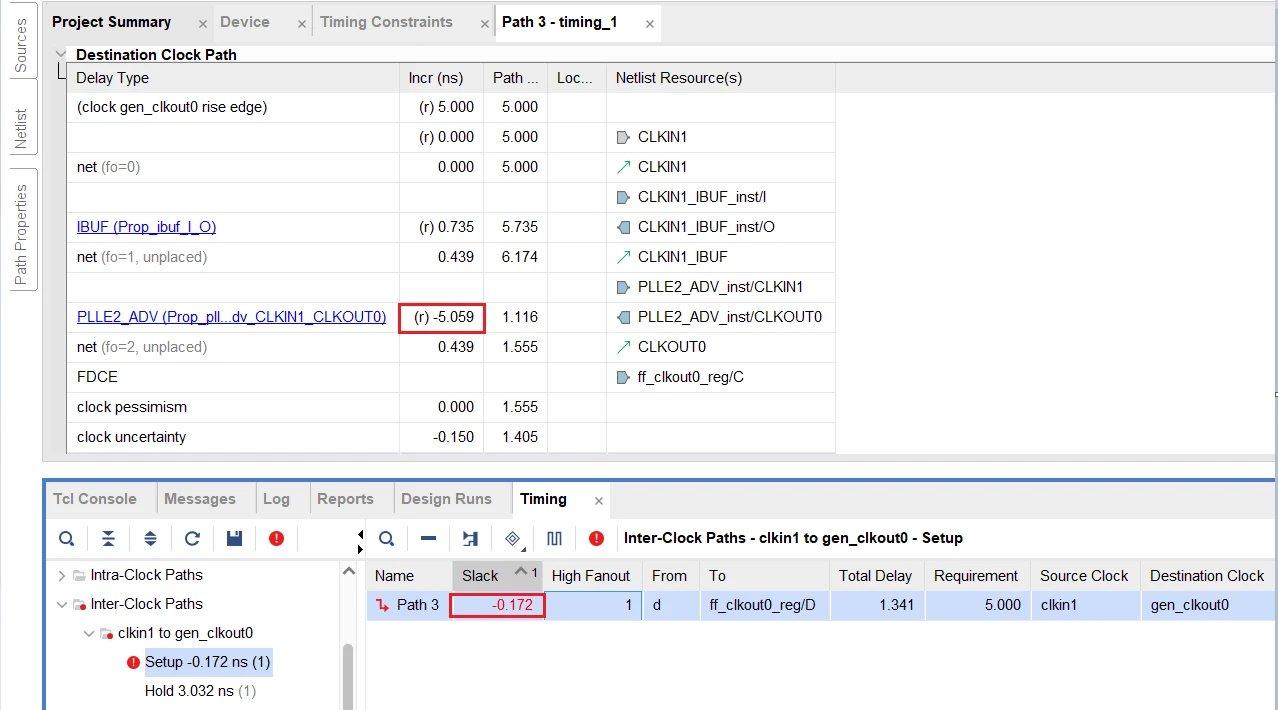

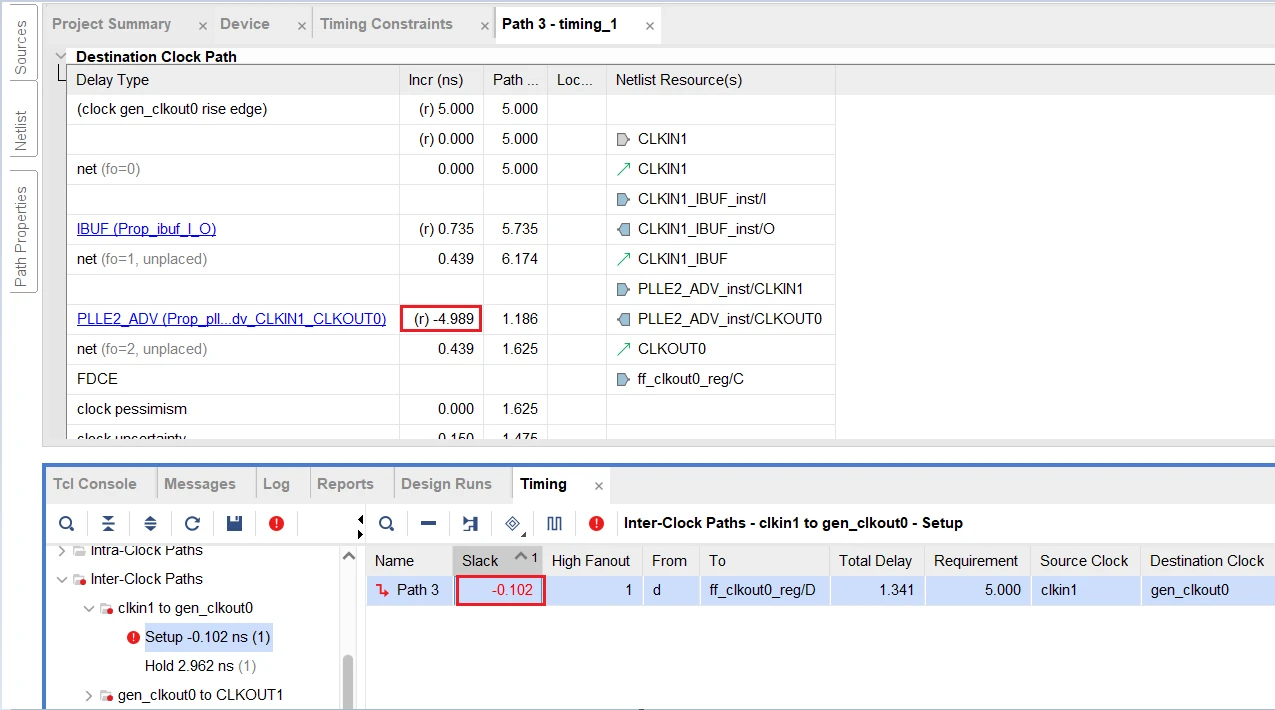

external_delay约束反馈延时为1.181ns时,PLLE2的Incr延时为-5.059ns,

修改external_delay约束值为1.111

set_external_delay -from [get_ports CLKFBOUT] -to [get_ports CLKFBIN] -min 1.111时序报告中其他路径延时不变,只有PLL的Incr延时变为-4.989ns,即体现了外反馈时延约束的影响

7723

7723

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?