目录

3.3.1 Clock Pair Classification

一、前言

本文介绍时序报告中关于时钟的两个报告:Report clock network和Report Clock interaction,Report clock network报告主要是以树状结构报告设计中各时钟驱动的load,Report Clock interaction则是报告设计中时钟间的关系,如同步时钟还是异步时钟等,与load无关。

二、Report Clock Network

2.1 Report Clock Network流程

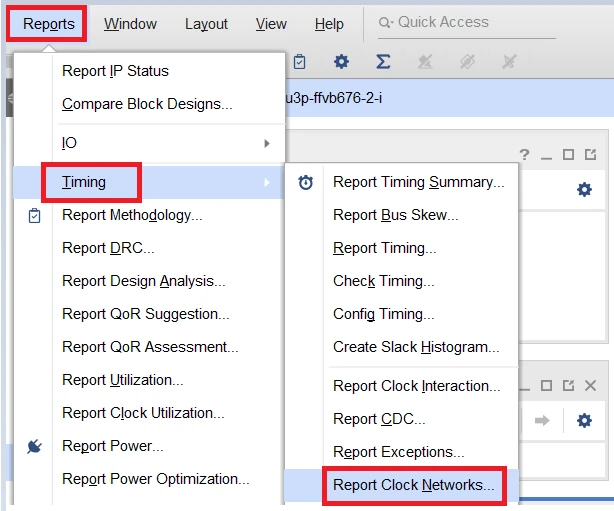

Report Clock Network从菜单栏的“Reports->Timing->Report Clock Networks”进入

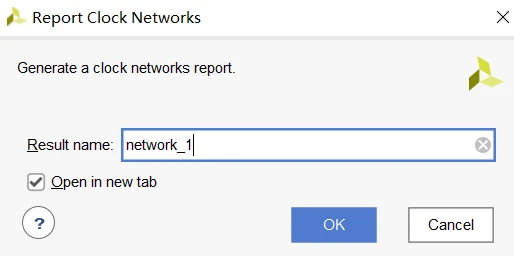

报告无特殊的配置项,主要是报告名称的设置

2.2 Report Clock Network报告

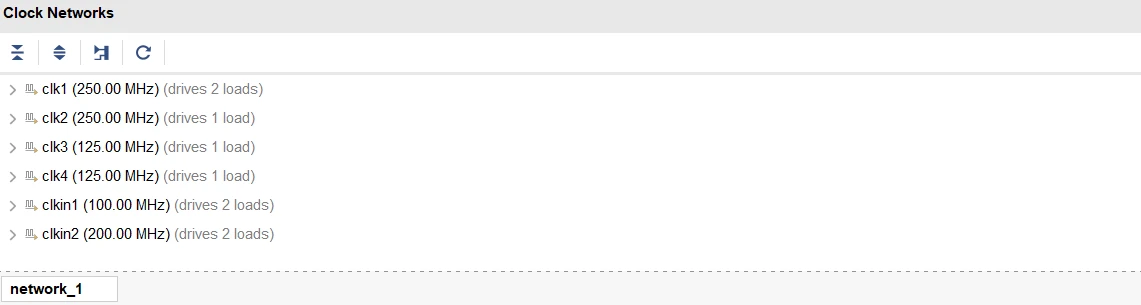

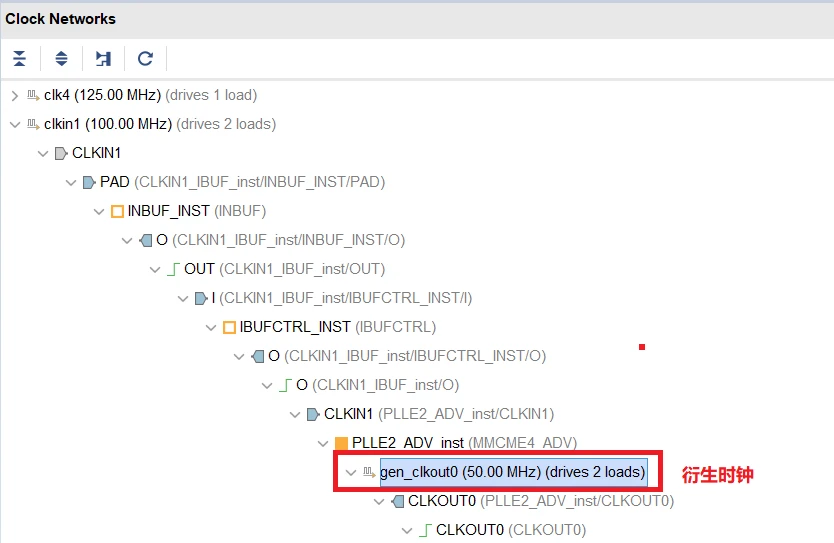

下图是clock network报告,包含了设计中的所有时钟及时钟所驱动的loads

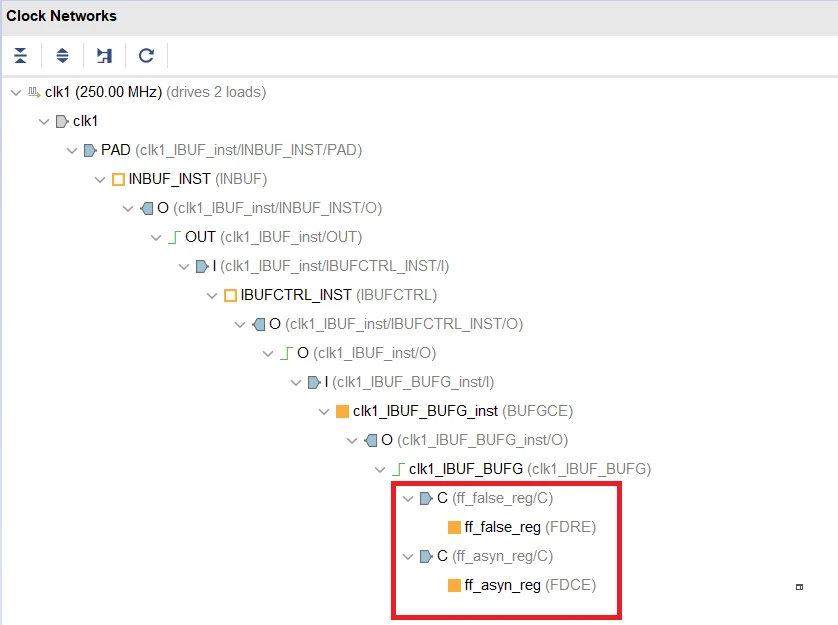

展开后可以查看时钟驱动的具体load单元

对于衍生时钟不会单独显示,统计到主时钟下面

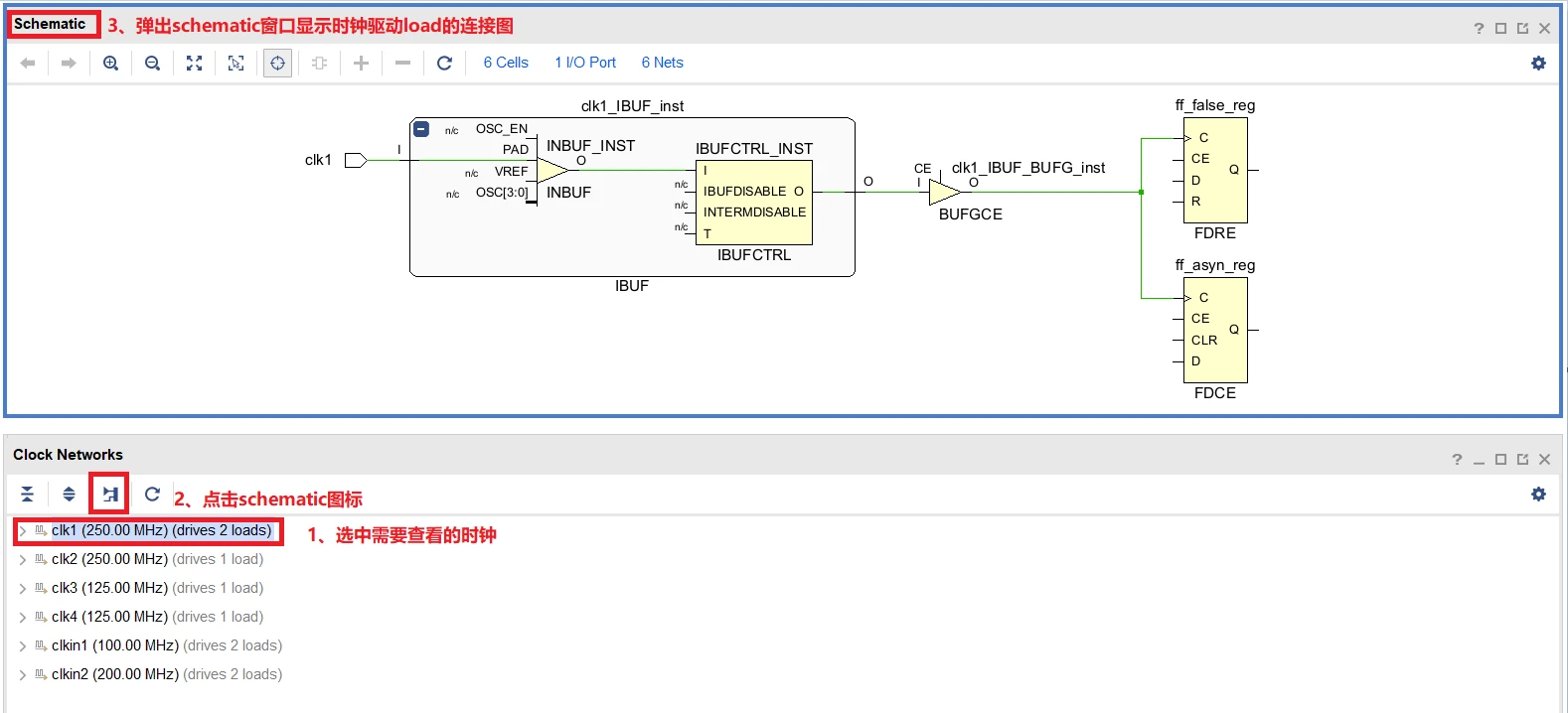

选中时钟后,通过schematic图标或按"F4"或者右键弹出弹框选择"Schematic"可以查看时钟驱动的load连接图

三、Report Clock Interaction

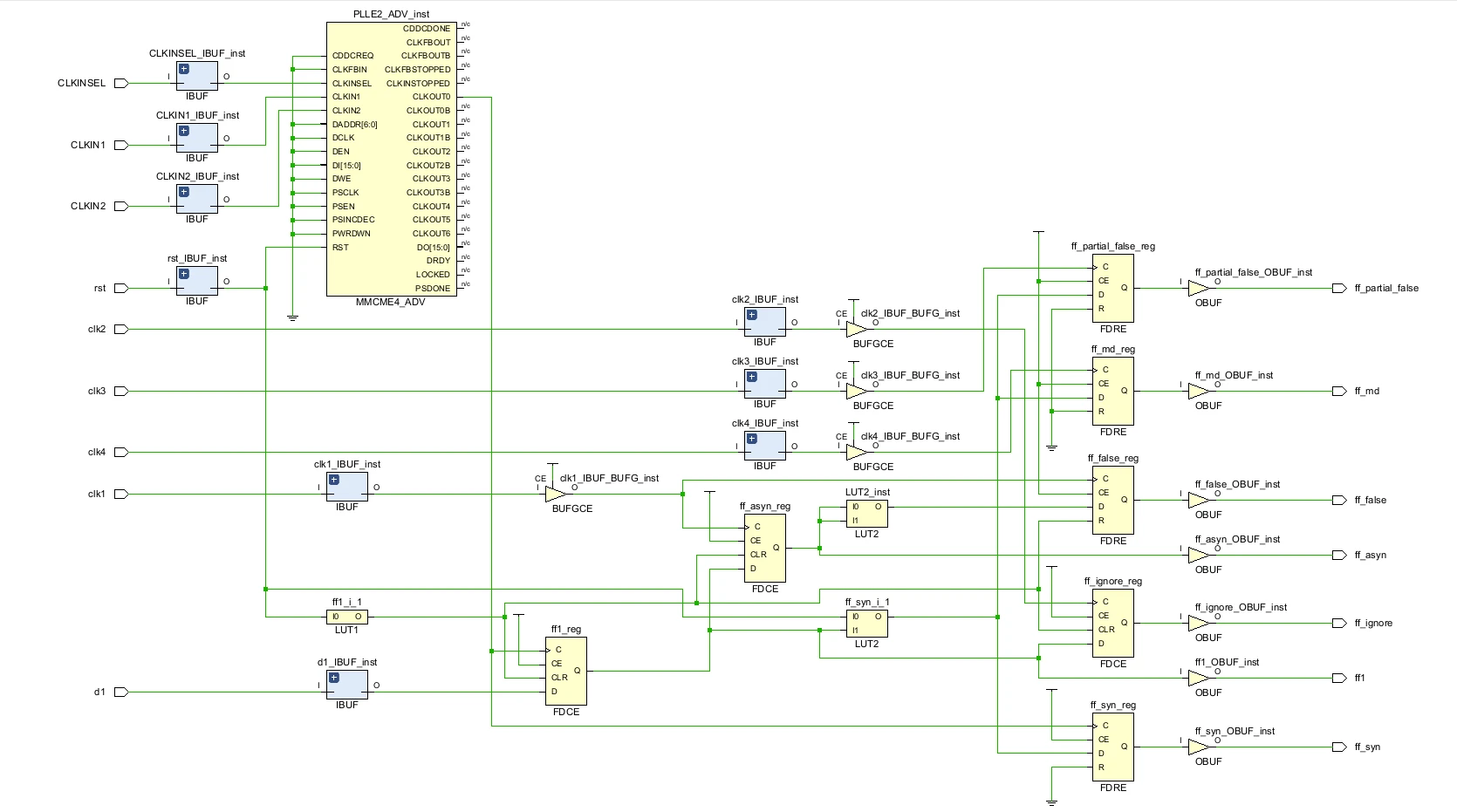

3.1 示例设计

module Report_clock(CLKIN1,CLKIN2,CLKINSEL,clk1,clk2,clk3,clk4,rst,d1,ff1,ff_syn,ff_asyn,ff_md,ff_ignore,ff_false,ff_partial_false);

input CLKIN1,CLKIN2,CLKINSEL,clk1,clk2,clk3,clk4,rst,d1;

output reg ff1,ff_syn,ff_asyn,ff_md,ff_ignore,ff_false,ff_partial_false;

wire o_lut;

PLLE2_ADV #(

.BANDWIDTH("OPTIMIZED"), // OPTIMIZED, HIGH, LOW

.CLKFBOUT_MULT(8), // Multiply value for all CLKOUT, (2-64)

.CLKFBOUT_PHASE(0.0), // Phase offset in degrees of CLKFB, (-360.000-360.000).

// CLKIN_PERIOD: Input clock period in nS to ps resolution (i.e. 33.333 is 30 MHz).

.CLKIN1_PERIOD(0.0),

.CLKIN2_PERIOD(0.0),

// CLKOUT0_DIVIDE - CLKOUT5_DIVIDE: Divide amount for CLKOUT (1-128)

.CLKOUT0_DIVIDE(1),

.CLKOUT1_DIVIDE(2),

.CLKOUT2_DIVIDE(4),

.CLKOUT3_DIVIDE(5),

.COMPENSATION("EXTERNAL"), // ZHOLD, BUF_IN, EXTERNAL, INTERNAL

.DIVCLK_DIVIDE(1), // Master division value (1-56)

// REF_JITTER: Reference input jitter in UI (0.000-0.999).

.STARTUP_WAIT("FALSE") // Delay DONE until PLL Locks, ("TRUE"/"FALSE")

)

PLLE2_ADV_inst (

// Clock Outputs: 1-bit (each) output: User configurable clock outputs

.CLKOUT0(CLKOUT0), // 1-bit output: CLKOUT0

.CLKOUT1(CLKOUT1), // 1-bit output: CLKOUT1

.CLKOUT2(CLKOUT2), // 1-bit output: CLKOUT2

.CLKIN1(CLKIN1), // 1-bit input: Primary clock

.CLKIN2(CLKIN2), // 1-bit input: Secondary clock

.CLKINSEL(CLKINSEL), // 1-bit input: Clock select, High=CLKIN1 Low=CLKIN2

.RST(rst) // 1-bit input: Reset

// Feedback Clocks: 1-bit (each) input: Clock feedback ports

);

always@(posedge CLKOUT0,negedge rst)

begin

if(!rst)

ff1<=1'b0;

else

ff1<=d1;

end

always@(posedge CLKOUT0)

begin

if(!rst)

ff_syn<=1'b0;

else

ff_syn<=ff1;

end

always@(posedge clk1,negedge rst)

begin

if(!rst)

ff_asyn<=1'b0;

else

ff_asyn<=ff1;

end

always@(posedge clk4)

begin

if(!rst)

ff_md<=1'b0;

else

ff_md<=ff1;

end

always@(posedge clk2,negedge rst)

begin

if(!rst)

ff_ignore<=1'b0;

else

ff_ignore<=ff1;

end

LUT2 #(

.INIT(4'h16) // Specify LUT Contents

) LUT2_inst (

.O(o_lut), // LUT general output

.I0(ff_asyn), // LUT input

.I1(ff_asyn) // LUT input

);

always@(posedge clk1)

begin

if(!rst)

ff_false<=1'b0;

else

ff_false<=o_lut;

end

always@(posedge clk3)

begin

if(!rst)

ff_partial_false<=1'b0;

else

ff_partial_false<=ff1;

end

endmodule 时序约束

create_clock -period 10.000 -name clkin1 -waveform {0.000 5.000} -add [get_ports CLKIN1]

create_clock -period 5.000 -name clkin2 -waveform {0.000 2.500} -add [get_nets CLKIN2]

create_clock -period 4.000 -name clk2 -waveform {0.000 2.000} -add [get_ports clk2]

create_clock -period 4.000 -name clk1 -waveform {0.000 2.000} -add [get_ports clk1]

create_clock -period 8.000 -name clk3 -waveform {0.000 4.000} [get_ports clk3]

create_clock -period 8.000 -name clk4 -waveform {0.000 4.000} [get_ports clk4]

create_generated_clock -name gen_clkout0 -source [get_ports CLKIN1] -divide_by 2 -add -master_clock clkin1 [get_pins PLLE2_ADV_inst/CLKOUT0]

set_clock_groups -name clk2_grp -asynchronous -group [get_clocks clk2]

set_max_delay -datapath_only -from [get_cells ff1_reg] -to [get_cells ff_md_reg] 2.000

set_false_path -hold -from [get_cells ff1_reg] -to [get_cells ff_partial_false_reg]

set_false_path -from [get_cells ff_asyn_reg] -through [get_pins LUT2_inst/I1] -to [get_cells ff_false_reg]schematic图,总的结构是pll->ff->各种interaction下的ff

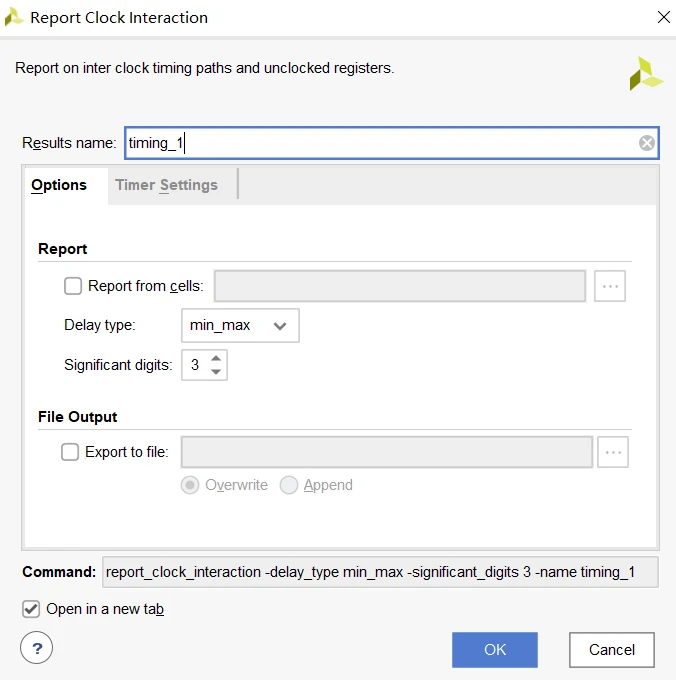

3.2 配置选项

3.2.1 Options

Report from cells: 指定对特定的cells单元进行分析,报告只包含与该单元有关的时序

Delay type: 设置运行分析的类型,可设为min,max,min_max,综合阶段和实现阶段默认max和min都会分析,如果选择min,则只进行hold和removal分析

Significant digits:控制报告中数字显示的精度,默认是3位小数

Export to file:默认的时序报告结果是写入时序窗口中,可以指定导出到指定的文件,写入时可以指定时覆盖overwrite或追加append写入

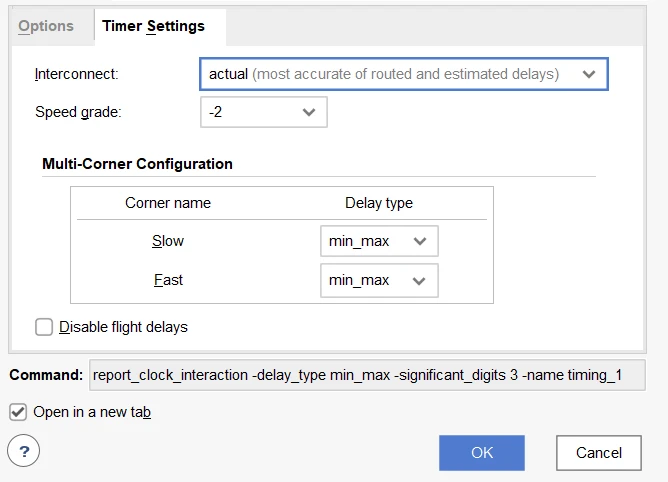

3.2.2 Timer_Settings

Interconnect:用于控制net的时延值的计算方式,可以是评估的cell间的布线距离,实际的布线或者时序分析时移除net的时延。默认情况下,综合后阶段是用估算的net延时值,实现阶段后是用实际的net时延。可以设置值:actual,estimated,none

Speed grade:设置器件的速度等级,通常情况下该值和工程创建时设置的速度一致,也可以不需要重新运行综合和实现,直接改变速度等级进行时序分析,等效的tcl命令为 set_speed_grade

Multi-corner configuration:指定fast/slow corner(可以理解为芯片运行的外部环境的好坏)下分析的路径时延类型,可以为none,min,max,min_max

Disable flight delays:勾选后时序分析不会考虑I/O端口的封装时延

3.3 Clock Interaction报告

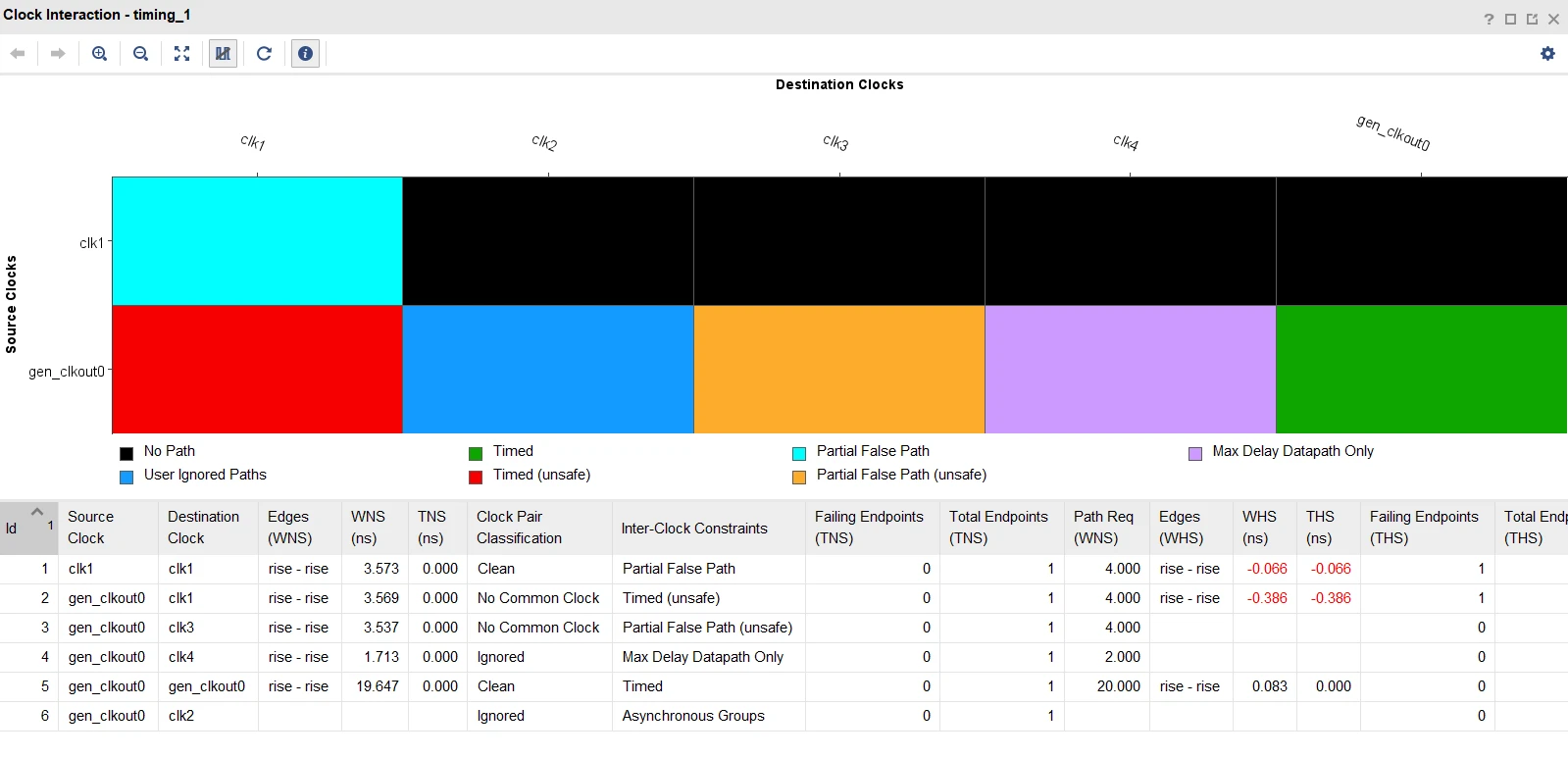

下图是上述设计默认配置下的interaction报告,覆盖率时钟interaction中的七种关系,横坐标为destination clock,纵坐标为source clock

对于报告主要解释几列关键的内容

Source clock:源时钟,时序路径的起点,也是launch时钟

Destination clock:目的时钟,时序路径的终点,也是capture clock

WNS(Worst Negative Slack):一对时钟组中最差时序的slack值,

TNS(Total Negative Slack):一对时钟组中所有slack为负的总和,如示例中gen_clkout0到clk3为0说明对应时钟路径都满足时序要求。

3.3.1 Clock Pair Classification

Clock Pair Classification时钟组分类提供有关两个时钟之间缺少公共主时钟、缺少公共节点、缺少公共相位以及缺少公共周期的信息, 以及是否有虚拟时钟。

下面从优先级最高到最低的顺序列出了可能的值,一旦检测到符合任一条件, 报告命令就不会执行剩余的检查。

Ignored : 当“Clock Group” (时钟组) 、“False Path” (伪路径) 或“Max Delay Datapath

Only” (仅最大延迟数据路径) 完全覆盖时钟对时, 将不会分析。

Virtual Clock : 至少有一个时钟是虚拟时钟, 并且不适用公共主时钟或公共节点检查。

No Common Clock: 两个时钟没有共同的主时钟。

No Common Period: 两个时钟的周期不可扩展。

Partial Common Node: 两个时钟为同步时钟, 但一小部分交汇路径不具有公共节点, 并且

没有安全的时间。

No Common Node : 两个时钟为同步, 但交汇路径无公共节点。

No Common Phase : 两个时钟没有共同的的相位关系。

Clean: 以上情况均不符合

3.3.2 Inter-clock Constraints

Inter-clock Constraints从时序约束角度来展示两个时钟间的关系

No Path(无路径): 源时钟与目的时钟不存在时序路径, 无需报告,黑色块。

Timed(已定时):源时钟与目的时钟存在同步关系, 并且时序约束正常。 时序分析工具根据 2 个时钟具有共同的主时钟和简单的周期比来判定是否符合此状态,绿色块。

User Ignored Paths(用户忽略的路径): 用户定义的伪路径false path或时钟组clock group 约束覆盖从源时钟到目的时钟的所有路径。当运行interaction报告仅仅是为了进行保持时间分析 (-delay_type min) 并且 set_max_delay -datapath_only 约束已覆盖源时钟和目的时钟, Clock Pair Classification(时钟对分类) 会报告为“ignored”,蓝色块 。

Partial False Path(部分伪路径): 用户定义的伪路径false path约束覆盖从源时钟到目的时钟的部分时序路径, 其中源时钟与目的时钟存在同步关系,浅蓝色。

Timed (Unsafe)已定时(不安全): 源时钟与目标时钟存在异步关系。在此情况下, 不存在公共主时钟, 也不存在可扩展周期 ,红色块。

Partial False Path (Unsafe)部分伪路径(不安全): 此类和Timed (Unsafe)相似, 区别在于从源时钟到目的时钟的至少 1 条路径因false path而被忽略,橙色块。

Max Delay Datapath Only(仅最大延迟数据路径): set_max_delay -datapath_only 约束覆盖从源时钟到目的时钟的所有路径,灰色块。

注意! 矩阵中单元颜色反映了时钟域之间约束的状态, 而不是时钟域之间时序路径最差slack的状态。如绿色块并不表示满足时序, 仅表示跨时钟域的所有时序路径已正确分析, 并且两时钟间具有已知的相位关系。

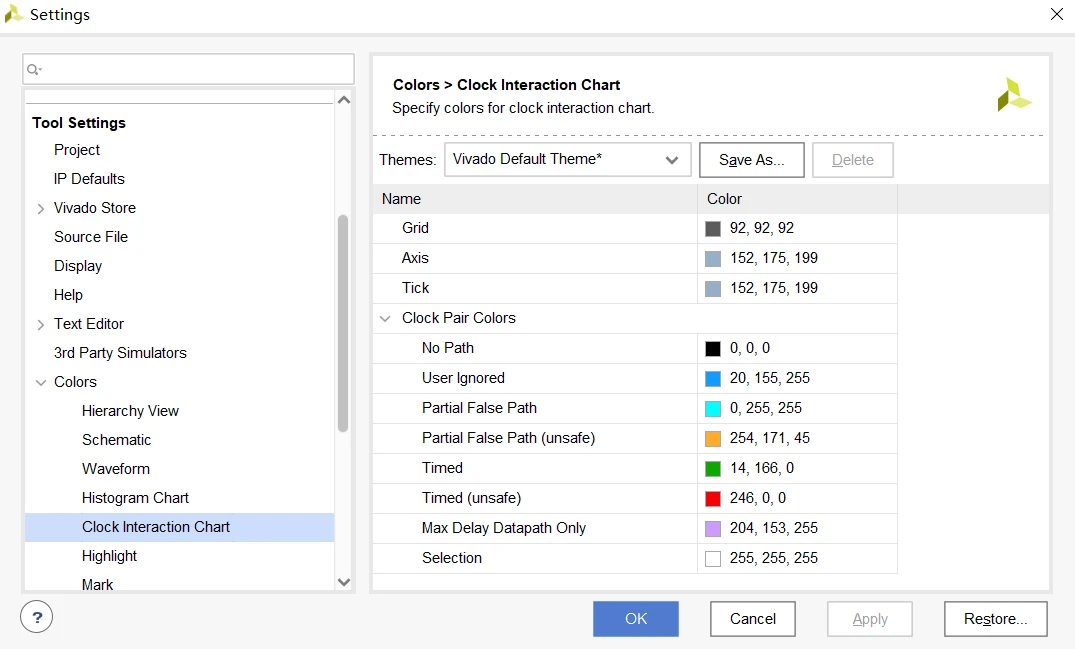

3.3.3 interaction图颜色调整

通过“Tools->Settings->Colors->Clock Interaction Chart”可进入颜色设置界面

3.3.4 示例报告解说

partial false path为ff_asyn_reg到ff_false_reg间存在两条路径,但只对其中的一条设置了set_false_path,对应的约束为

set_false_path -from [get_cells ff_asyn_reg] -through [get_pins LUT2_inst/I1] -to [get_cells ff_false_reg]Time(unsafe)的路径为gen_clkout0到clk1,两者为异步时序路径,无其他时序例外约束

Partial False path(unsafe)为gen_clkout0到clk3,两者为异步时序路径,但设置了set_false_path约束,

set_false_path -hold -from [get_cells ff1_reg] -to [get_cells ff_partial_false_reg]Max Delay Datapath Only为gen_clkout0到clk4,两者间的ff1_reg到ff_md_reg只存在data_path -only约束,约束如下

set_max_delay -datapath_only -from [get_cells ff1_reg] -to [get_cells ff_md_reg] 2.000Timed为gen_clkout0到gen_clkout0,为同步时钟域路径,故时序约束分析正常,无其他时序例外约束

Asynchronous Groups为gen_clkout0到clk2,对clk2设置了clock_group约束,约束如下

set_clock_groups -name clk2_grp -asynchronous -group [get_clocks clk2]

746

746

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?