1、复查时序路径详情

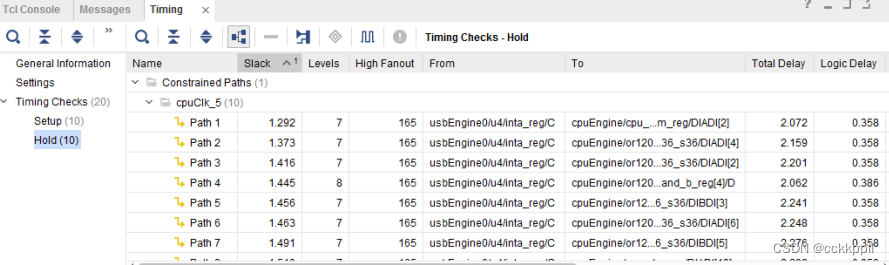

单击“OK”运行报告命令后,将打开一个新窗口。这样您即可复查其中内容。在其中可查看执行选定的每种类型 (min/max/min_max) 的分析之后所报告的 N 条最差路径。 下图显示的“Report Timing”(时序报告)窗口中已选中最小和最大分析(SETUP 和 HOLD),且 N=4。

选中其中任意路径即可在“Path Properties”(路径属性)窗口的“Report”(报告)选项卡下查看其详情。

2、Report Timing Summary

综合后即可在流程中随时执行时序分析。您可复查由综合和实现运行自动创建的“Timing Summary”(时序汇总)报告文件。 如果在存储器中已加载综合后设计或实现后设计,那么还可通过以下方式生成交互式“Timing Summary”报告:

• “Flow Navigator” → “Synthesis”(Flow Navigator > 综合)

• “Flow Navigator” → “Implementation”(Flow Navigator > 实现)

• “Reports” → “Timing” → “Report Timing Summary”(报告 > 时序 > 时序汇总报告)

等效的 Tcl 命令为 report_timing_summary。

在综合后设计中,AMD Vivado™ IDE 时序引擎会基于连接和扇出来估算信号线延迟。对于已由用户布局的单元之间的信号线,延迟准确性更高。在包含部分预布局单元(例如,I/O 和 GT)的路径上,时钟偏差可能更大。 在实现后设计中,基于实际布线信息来估算信号线延迟。对于已完全布线的设计,必须使用“Timing Summary”报告来实现时序验收。要验证设计是否已完全布线,请复查“Route Status”(布线状态)报告。 从 Tcl 控制台或从 GUI 运行此时序汇总报告时,可使用 -cells 选项将其限定于 1 个或多个层级单元。限定报告作用域后,将仅报告含如下数据路径部分的路径:数据路径开始或结束于此类单元、与此类单元交汇或者完全包含于此类单元内。

从 Tcl 控制台运行时,此报告的第一部分提供了来自最新的 report_methodology 运行的方法论违例汇总信息。从GUI 运行 report_timing_summary 时,这部分名为“Methodology Summary”(方法论汇总)。如果运行report_timing_summary 之前尚未运行 report_methodology,则这部分为空。如果自从上一次 report_methodology 运行后已实现任意设计更改,那么违例汇总信息可能并未提供最新信息。

3、“Report Timing Summary”对话框

在 Vivado IDE 中,“Report Timing Summary”(时序汇总报告)对话框包含以下选项卡:

• “Options”选项卡

• “Advanced”选项卡

• “Timer Settings”选项卡

位于“Report Timing Summary”对话框顶部的“Results name”(结果名称)字段用于指定在“Results”(结果)窗口中打开的图形化报告的名称。图形化版本的报告包含超链接,支持您将来自报告的信号线和单元交叉引用至“Device”(器件)和“Schematic”(板级原理图)窗口以及设计源文件。 如果该字段留空,那么报告将返回 Tcl 控制台,且在“Results”窗口中不会打开图形化版本的报告。 等效的 Tcl 选项:-name

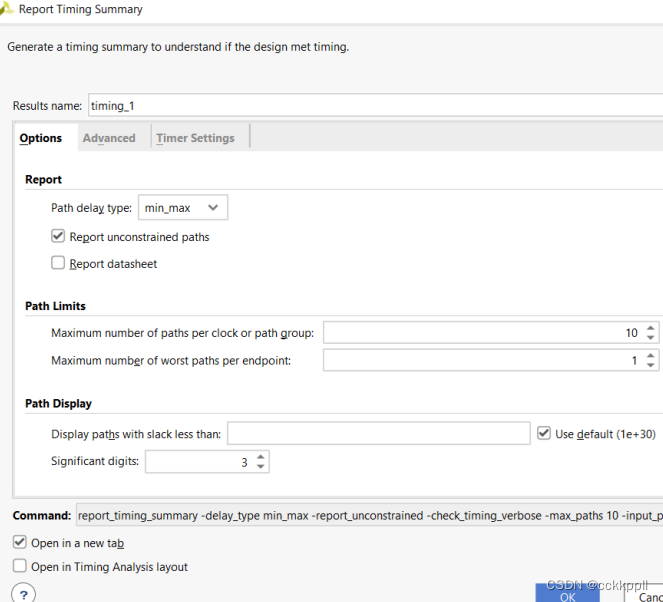

“Options”选项卡

“Report Timing Summary”(时序汇总报告)对话框中的“Options”(选项)选项卡如下图所示。

“Report”部分

“Report Timing Summary”(时序汇总报告)对话框的“Options”(选项)选项卡的“Report”(报告)部分包含 以下内容:

• “Path delay type”(路径延迟类型)

用于设置要运行的分析类型。对于综合后设计,默认情况下仅执行最大延迟分析(建立/恢复)。对于已实现的设计,默认情况下,将执行最小和最大延迟分析(建立/保持和恢复/移除)。要仅运行最小延迟分析(保持和移除),请选择延迟类型 min。 等效的 Tcl 选项:-delay_type

• “Report unconstrained paths”(报告未约束路径)

生成不含时序要求的路径的相关信息。默认情况下,在 Vivado IDE 中已选中该选项,但在等效的 Tcl 命令 report_timing_summary 中默认不开启该选项。等效的 Tcl 选项:-report_unconstrained

• “Report datasheet”(数据手册报告) 生成本章中的 Report Datasheet 中所定义的设计数据手册。 等效的 Tcl 选项:-datasheet

“Path Limits”部分

“Report Timing Summary”(时序汇总报告)对话框中“Options”(选项)选项卡的“Path Limits”(路径限制)部 分包括:

• “Maximum number of paths per clock or path group”(各时钟或路径组的最大路径数):控制每个时钟对或每个路径组所报告的最大路径数。 等效的 Tcl 选项:-max_paths

• “Maximum number of worst paths per endpoint”(各端点的最差路径的最大数量):控制每个路径端点可能报告的最大路径数。此限制受到每个时钟对或路径组的最大数量的限制。因此,报告的路径总数仍受到 -max_paths 数量的限制。 等效的 Tcl 选项:-nworst

“Path Display”部分

“Report Timing Summary”(时序汇总报告)对话框的“Options”(选项)选项卡的“Path Display”(路径显示) 部分包括:

• “Display paths with slack less than”(显示裕量小于指定值的路径):基于路径的裕量值筛选报告的路径。此选项不影响汇总表的内容。 等效的 Tcl 选项:-slack_lesser_than

• “Significant digits”(有效位数):控制报告中显示的数值的精确度。 等效的 Tcl 选项:-significant_digits

通用部分

以下控件为位于“Report Timing Summary”(时序汇总报告)对话框底部的全部 3 个选项卡通用的控件:

• “Command”(命令):显示等效于“Report Timing Summary”对话框中指定的各种选项的 Tcl 命令行。

• “Open in a New Tab”(在新选项卡中打开):在新选项卡中打开结果,或替换“Results”(结果)窗口中打开的最后一个选项卡。

• “Open in Timing Analysis layout”(在时序分析布局中打开):将当前视图布局复位为“Timing Analysis”(时序 分析)视图布局。

“Advanced”选项卡

Report”部分

• “Report from cell”(基于单元的报告):启用该选项即可将时序报告限制在设计的特定单元上。报告将仅包含数据路径部分始于指定单元、止于该单元、跨该单元或完全包含于该单元内的路径。

等效的 Tcl 选项:-cells

• “Show input pins in path”(显示路径中的输入管脚):显示用于路径的单元输入管脚。 等效的 Tcl 选项:-input_pins

• “Report unique Pins”(唯一管脚报告):针对每一组唯一的管脚仅显示 1 条时序路径。

等效的 Tcl 选项:-unique_pins

“File Output”部分

• “Write results to file”(将结果写入文件):将结果写入指定文件名。默认情况下,报告将写入 Vivado IDE 的 “Timing”(时序)窗口。

等效的 Tcl 选项:-file

• “Overwrite”(覆盖)或“Append”(追加):当报告写入文件时,这 2 个选项可用于确定 (1) 覆盖指定文件, 还是 (2) 向现有报告追加新信息。

等效的 Tcl 选项:-append

• “Interactive report file”(交互式报告文件):将结果以 AMD RPX 格式写入指定的文件中。RPX 文件是一个包含所有报告信息的交互式报告,可在 Vivado Design Suite 中使用 open_report 命令将其重新加载到存储器中。

“Miscellaneous”部分

• “Ignore command errors”(忽略命令错误):以静默方式执行命令,忽略所有命令行错误,不返回任何消息。此命令还会返回 TCL_OK,忽略执行期间遇到的所有错误。 等效的 Tcl 选项:-quiet

• “Suspend message limits during command execution”(命令执行期间暂挂消息限制):临时覆盖所有消息限制并返回所有消息。 等效的 Tcl 选项:-verbose

“Timer Settings”选项卡

如需执行定时器设置,请使用如下任一方法:(1) 任一 Vivado IDE 时序分析对话框;或者 (2) 本节中列出的任一 Tcl 命令。这些设置会影响同一 Vivado IDE 会话内运行的其他时序相关命令,但综合和实现命令除外。 定时器设置不保存为工具首选项。每个新会话都会复原默认值。请勿更改默认值。保留默认值将以最准确的延迟值来提供最大的时序分析覆盖范围。

“Interconnect”设置

该选项用于控制信号线延迟计算方式:根据估算的叶节点单元管脚间布线距离来计算,还是根据实际布线的信号线来计算,或者从时序分析中排除信号线延迟。对于综合后设计,该选项自动设置为“Estimated”,对于实现后设计,该选 项自动设置为“Actual”。

• “Estimated”(估算):对于未布局的单元,信号线延迟值对应于可能实现的最佳布局的延迟,基于驱动程序和负载的性质以及扇出来计算。在时序路径报告中,未布局的叶节点单元管脚之间的信号线标记为未布局 (unplaced)。 对于已布局的单元,信号线延迟取决于驱动程序和负载之间的距离以及扇出。此信号线在时序路径报告中标记为estimated。

• “Actual”(实际):对于已布线的信号线,信号线延迟对应于已布线的互连的实际硬件延迟。此信号线在时序路径报告中标记为 routed。

• “None”(无):在时序报告中不考虑互连延迟,信号线延迟强制为 0。 等效的 Tcl 命令: set_delay_model

“Multi-Corner Configuration”设置

指定要针对指定时序角分析的路径延迟类型。有效值包括 none、max、min 和 min_max。选择 none 为指定时序角禁用的时序分析。等效的 Tcl 命令:config_timing_corners

Disable Flight Delays

不将封装延迟添加到 I/O 延迟计算中。 等效的 Tcl 命令:config_timing_analysis

本文详细介绍了AMDVivado工具中的时序分析功能,包括如何复查时序路径、执行ReportTimingSummary报告、设置选项和参数,以及如何在综合后和实现后设计阶段进行准确的信号线延迟估计和路径验证。

本文详细介绍了AMDVivado工具中的时序分析功能,包括如何复查时序路径、执行ReportTimingSummary报告、设置选项和参数,以及如何在综合后和实现后设计阶段进行准确的信号线延迟估计和路径验证。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?