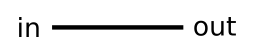

wire:

Implement the following circuit:

module top_module (

input in,

output out);

assign out=in;

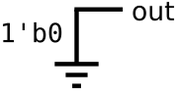

endmodulegnd:

Implement the following circuit:

.

module top_module (

output out);

assign out=1'b0;

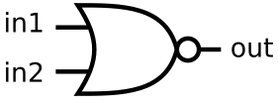

endmoduleNOR:

Implement the following circuit:

module top_module (

input in1,

input in2,

output out);

assign out=~(in1|in2);

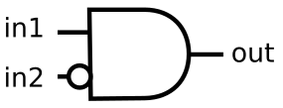

endmoduleanother gate:

Implement the following circuit

module top_module (

input in1,

input in2,

output out);

assign out=in1&(~in2);

endmoduletwo gates:

Implement the following circuit:

本文介绍了组合逻辑电路的设计,包括基本门电路如NOR、AND、OR等,以及通过这些门电路组合实现的复杂逻辑功能。内容涵盖7420芯片的功能实现,真理表的应用,两比特相等检测电路,简单电路模块设计,如实现特定逻辑关系的电路,并讨论了在实际应用场景中的电路设计,如手机振铃控制和恒温器控制。同时,还涉及到了人口计数电路和多位输入向量的相关逻辑关系检测。

本文介绍了组合逻辑电路的设计,包括基本门电路如NOR、AND、OR等,以及通过这些门电路组合实现的复杂逻辑功能。内容涵盖7420芯片的功能实现,真理表的应用,两比特相等检测电路,简单电路模块设计,如实现特定逻辑关系的电路,并讨论了在实际应用场景中的电路设计,如手机振铃控制和恒温器控制。同时,还涉及到了人口计数电路和多位输入向量的相关逻辑关系检测。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4215

4215

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?