Cortex-A510——Cache

小狼@http://blog.youkuaiyun.com/xiaolangyangyang

1、M7 Cache基本参数

ARM Cortex-A510系列Cache参数如下:

Cache Level:L1/L2/L3/SLC

L1 ICache/DCache

size:64K、32K

cache-line:4B、64B、512B

L2 Cache

size:1M、512K、256K

cache-line:16B

L3 Cache

size:16M

cache-line:128B

SLC Cache

size:4M * 4

cache-line:64B

2、Cortex-A510 Cache组织结构

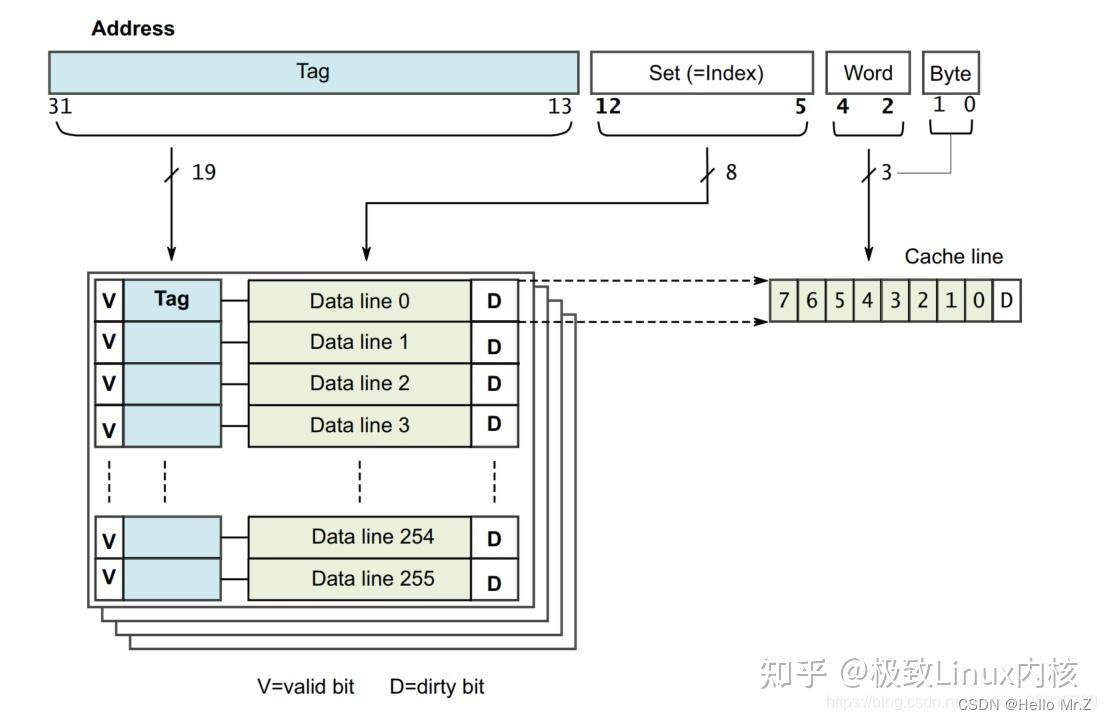

以cache-size为32k,cache-line为32Byte为例:

- 组相连(常用结构):4-way,256-set

- 直接映射:相当于1-way,1024-set的组相连

- 全相连:相当于1024-way,1-set的组相连

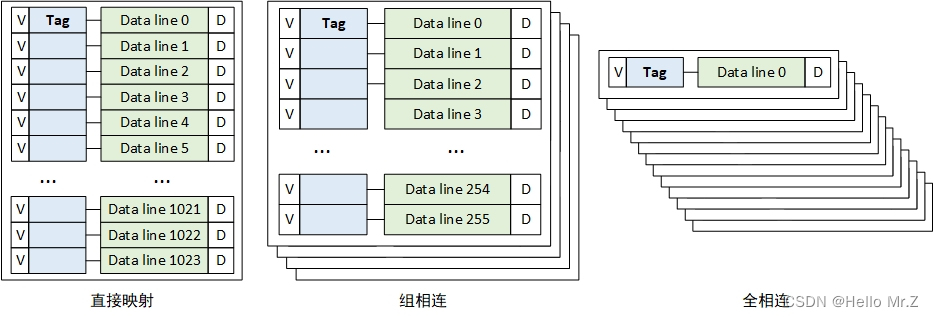

3、组相连

如果一个数据可以放在n个line,则称这个Cache是n路组相连的Cache(n-wayset-associativeCache),如下图所示为4-way,4-set的Cache。

组相连结构图

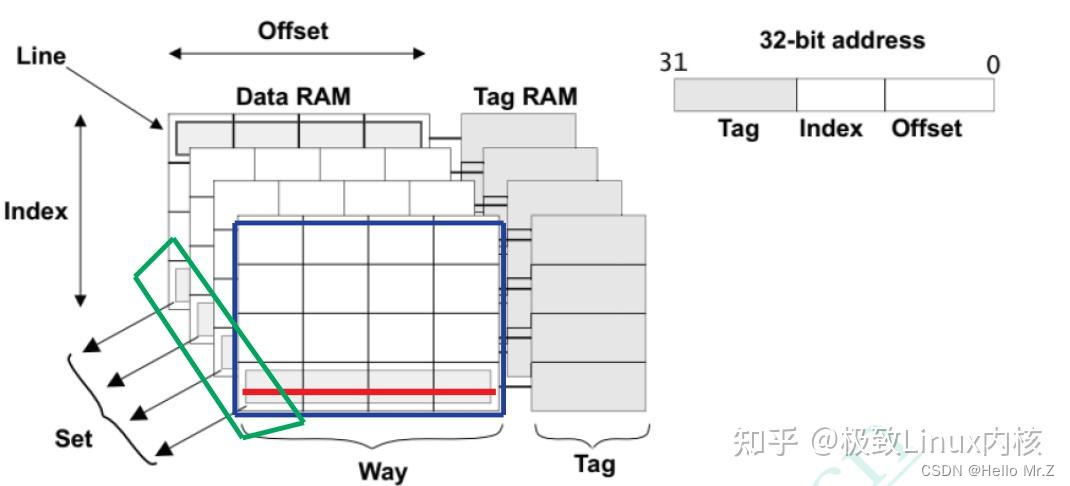

组相连映射图

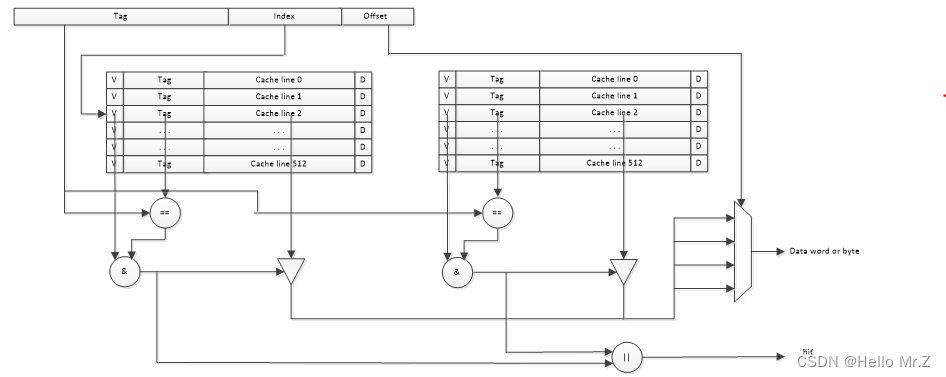

- offset:确定cache-line中数据位置,offset为图中Word+Byte;

- set:确定way中cache-line位置,即哪个组,如果数据被缓存,则V标志为1;

- tag:确定cache中way的位置,如果数据被缓存,tag中保存有地址信息,与处理器地址进行比对;

- V:cache-line有效标记;

- D:脏数据标记。

组相连映射硬件逻辑图

4、VIVT/VIPT/PIPT

VIVT(Virtual Index Virtual Tag):使用虚拟地址Index域和虚拟地址Tag域

多个VA可能映射到同一PA,导致多个cache line组(VA不同,index域不同,查找

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

497

497

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?