Cortex-A510——GIC

小狼@http://blog.youkuaiyun.com/xiaolangyangyang

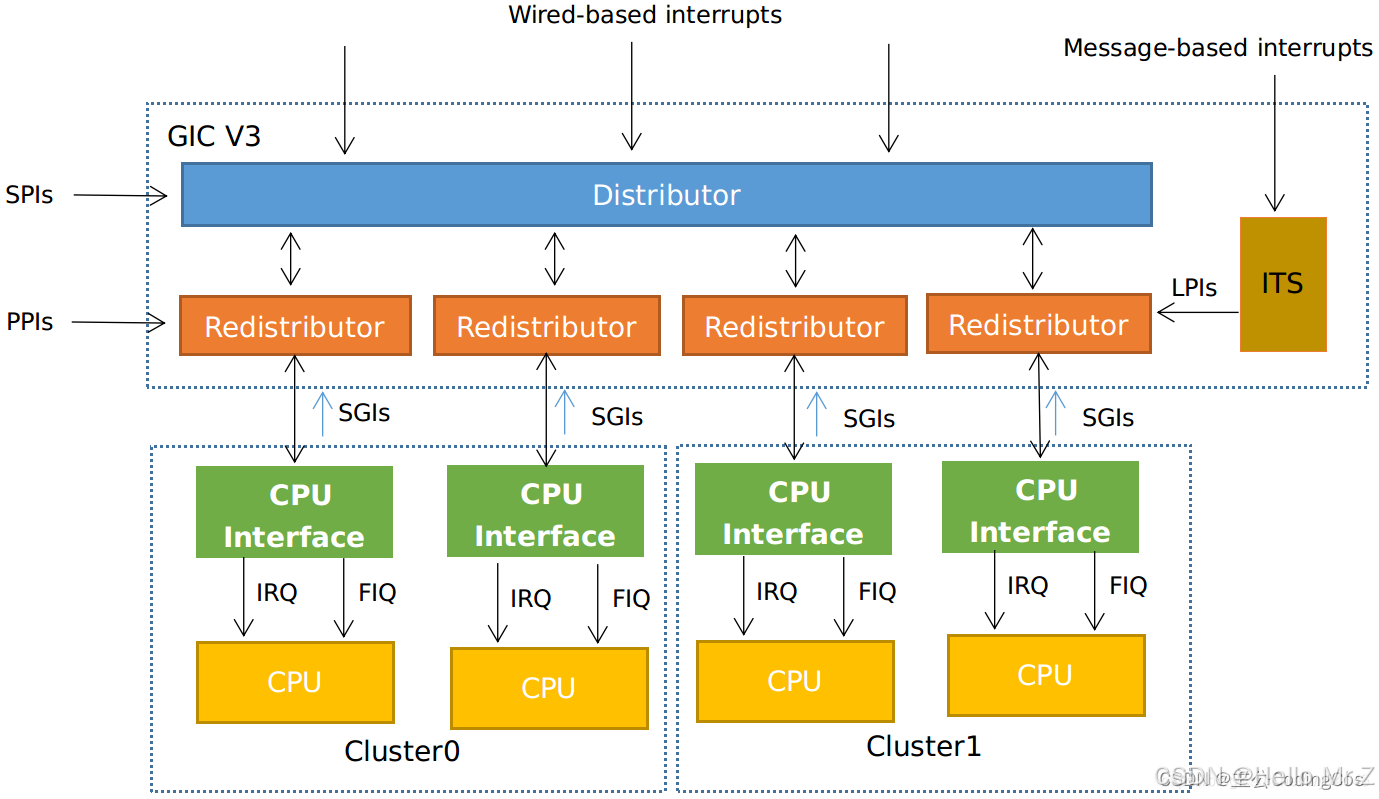

1、中断类型

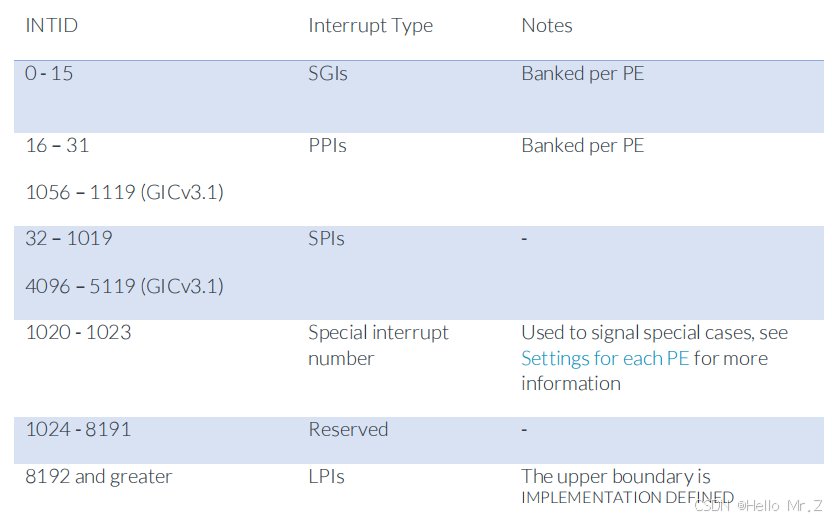

- SGIs:Software Generated Interrupt(0~15)

- PPI:Per-Processor Interrupt(16~31,1056~1119)

- SPI:Shared Phripheral Interrupt(32~1019,4096~5119)

- LPI:Locality-Specific Peripheral Interrupt(GIC-V3之后增加的Feature,8192~)

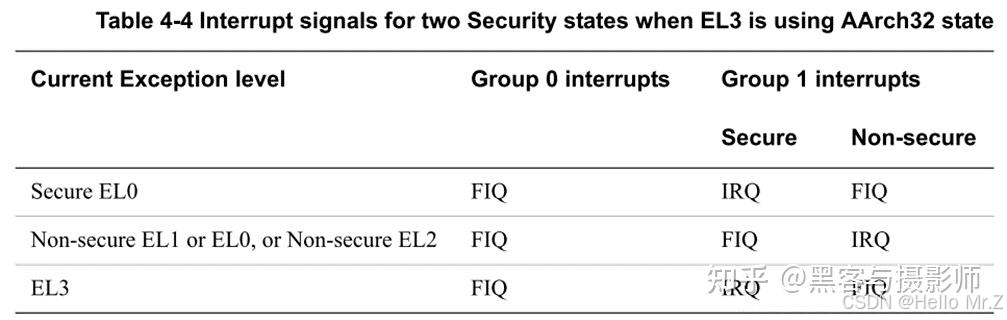

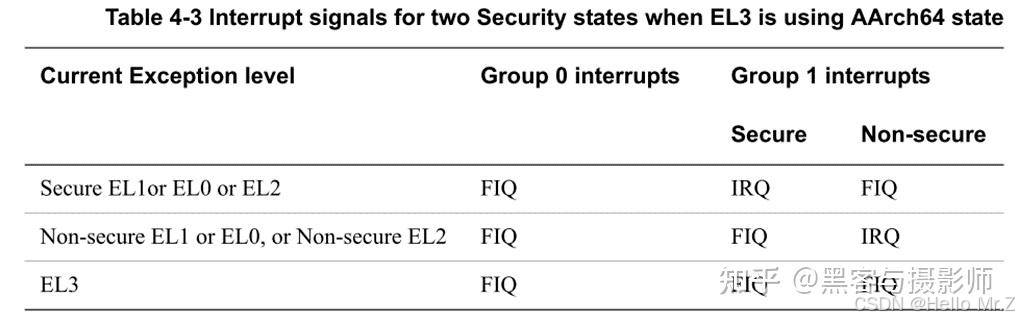

2、中断分组

中断分组的目的就是使不同Group的中断,在CPU不同状态下可分别被路由到IRQ或FIQ上,在AARCH32/AARCH64状态下,中断的路由方式如下:

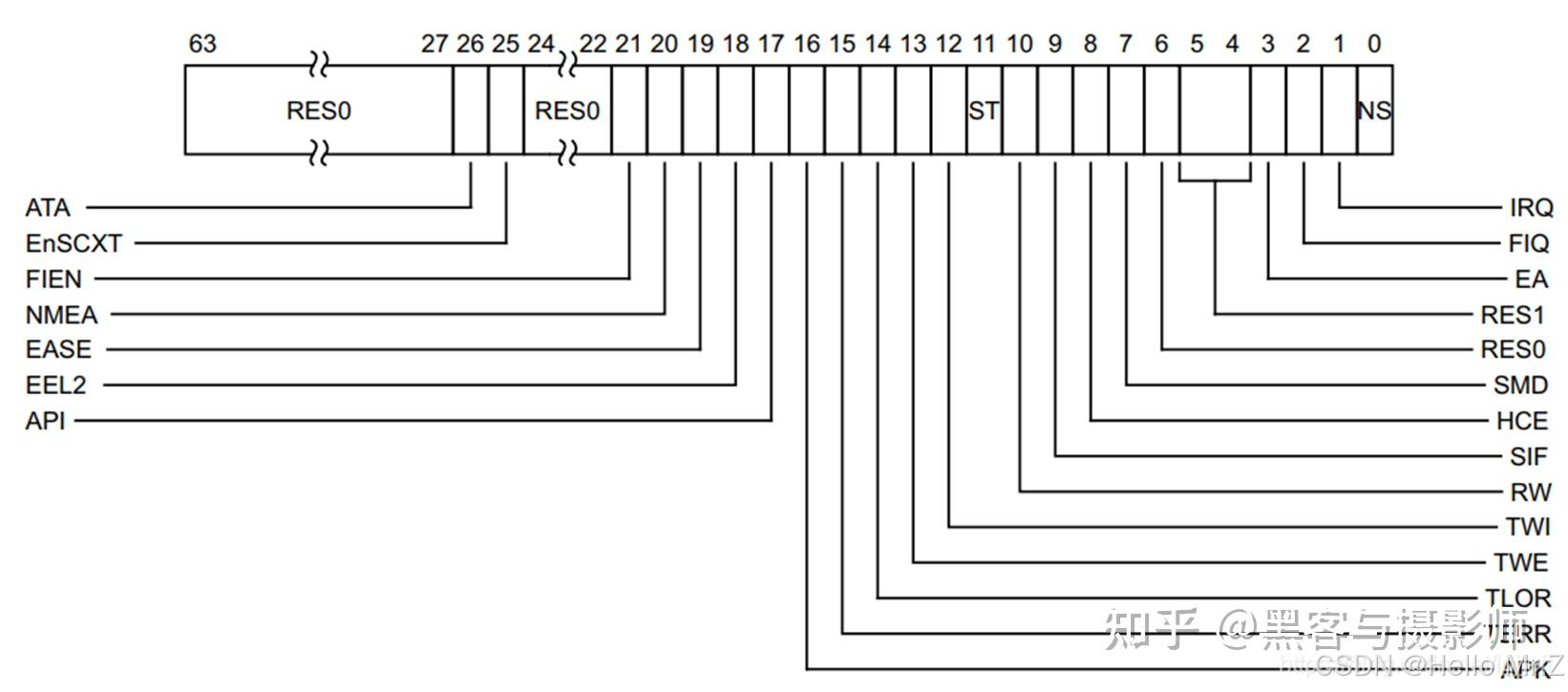

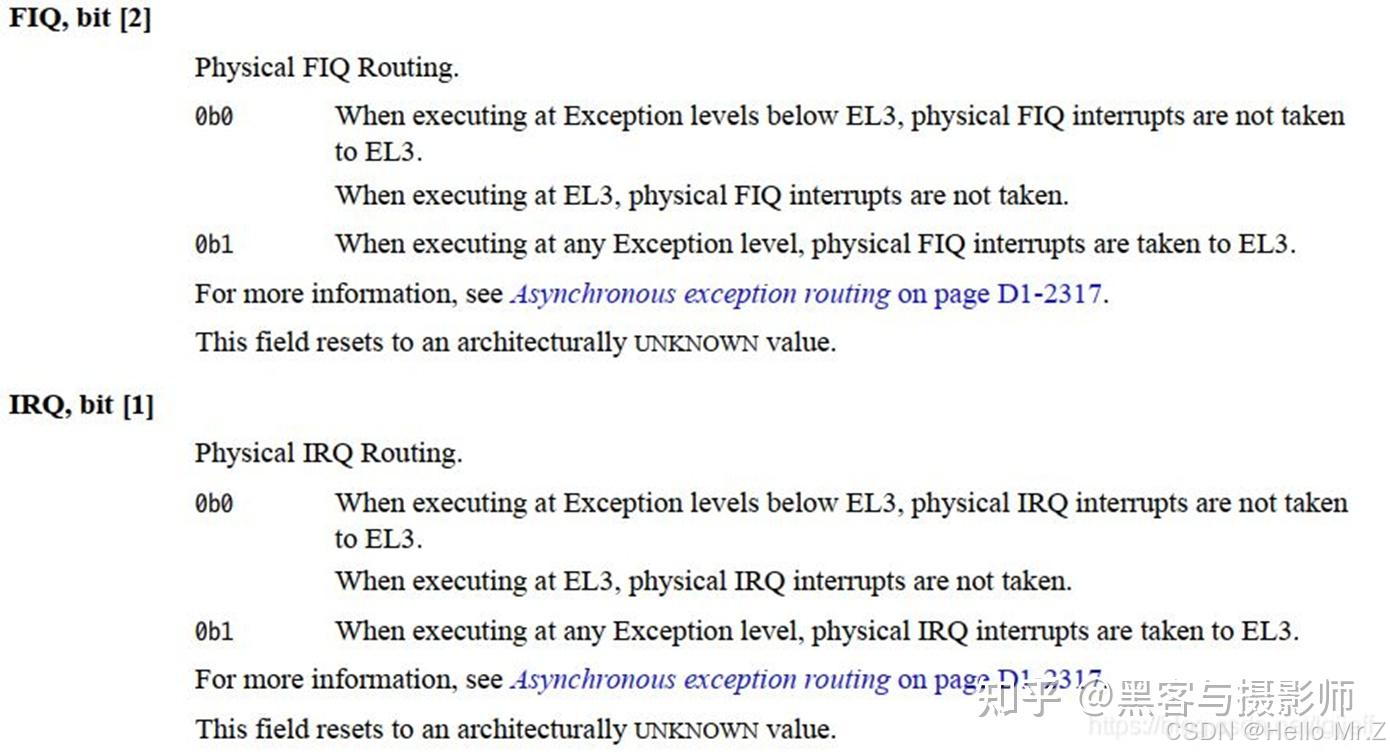

有了IRQ和FIQ,其具体在CPU哪级异常执行,由SCR_EL3寄存器决定,如下所示:

3、FIQ与IRQ区别

1、对FIQ你必须进快处理中断请求,并离开这个模式;

2、IRQ可以被FIQ所中断,但FIQ不能被IRQ所中断,在处理FIQ时必须要关闭中断;

3、FIQ的优先级比IRQ高;

ARMv8里已经没有区别

4、FIQ模式下,比IRQ模式多了几个独立的寄存器;

ARMv8里IRQ/FIQ不会进行硬件压栈,所以在ARMv8里没区别。

5、FIQ的中断向量地址不同;

6、IRQ和FIQ的响应延迟有区别

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

308

308

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?