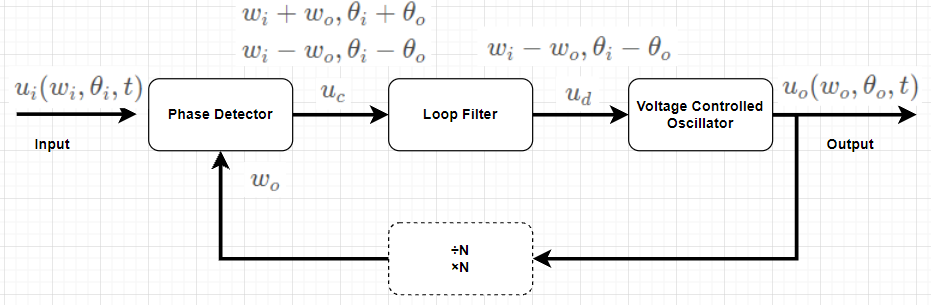

功能

- 输出一个和输入信号同频、同相位(或有固定相位差)的信号

组成

- w o ÷ N = w i w_o \div N=w_i wo÷N=wi

- w o × N = w i w_o \times N=w_i wo×N=wi

- 负反馈是分频器(÷N)时,PLL为倍频电路

- 负反馈是倍频器(×N)时,PLL为分频电路

鉴相器(PD,Phase Detector)

- 比较输入和反馈信号的相位,输出一个和两个信号相位差相关的信号

正弦波鉴相器 - 模拟乘法器

u

i

=

U

i

s

i

n

[

w

i

t

+

θ

i

(

t

)

]

=

U

i

s

i

n

ϕ

i

u_i=U_isin[w_it+\theta_i(t)]=U_isin{\phi_i}

ui=Uisin[wit+θi(t)]=Uisinϕi

u

o

=

U

o

c

o

s

[

w

o

t

+

θ

o

(

t

)

]

=

U

o

c

o

s

ϕ

o

u_o=U_ocos[w_ot+\theta_o(t)]=U_ocos{\phi_o}

uo=Uocos[wot+θo(t)]=Uocosϕo

u

c

=

A

m

u

i

u

o

=

1

2

A

m

u

i

u

o

{

s

i

n

[

(

w

i

+

w

o

)

t

+

θ

i

(

t

)

+

θ

o

(

t

)

]

+

s

i

n

[

(

w

i

−

w

o

)

t

+

θ

i

(

t

)

−

θ

o

(

t

)

]

}

u_c=A_mu_iu_o={1 \over 2}A_mu_iu_o\{sin[(w_i+w_o)t+\theta_i(t)+\theta_o(t)]+sin[(w_i-w_o)t+\theta_i(t)-\theta_o(t)]\}

uc=Amuiuo=21Amuiuo{sin[(wi+wo)t+θi(t)+θo(t)]+sin[(wi−wo)t+θi(t)−θo(t)]}

u

c

=

K

d

{

s

i

n

[

(

w

i

+

w

o

)

t

+

θ

i

(

t

)

+

θ

o

(

t

)

]

+

s

i

n

[

(

w

i

−

w

o

)

t

+

θ

i

(

t

)

−

θ

o

(

t

)

]

}

u_c=K_d\{sin[(w_i+w_o)t+\theta_i(t)+\theta_o(t)]+sin[(w_i-w_o)t+\theta_i(t)-\theta_o(t)]\}

uc=Kd{sin[(wi+wo)t+θi(t)+θo(t)]+sin[(wi−wo)t+θi(t)−θo(t)]}

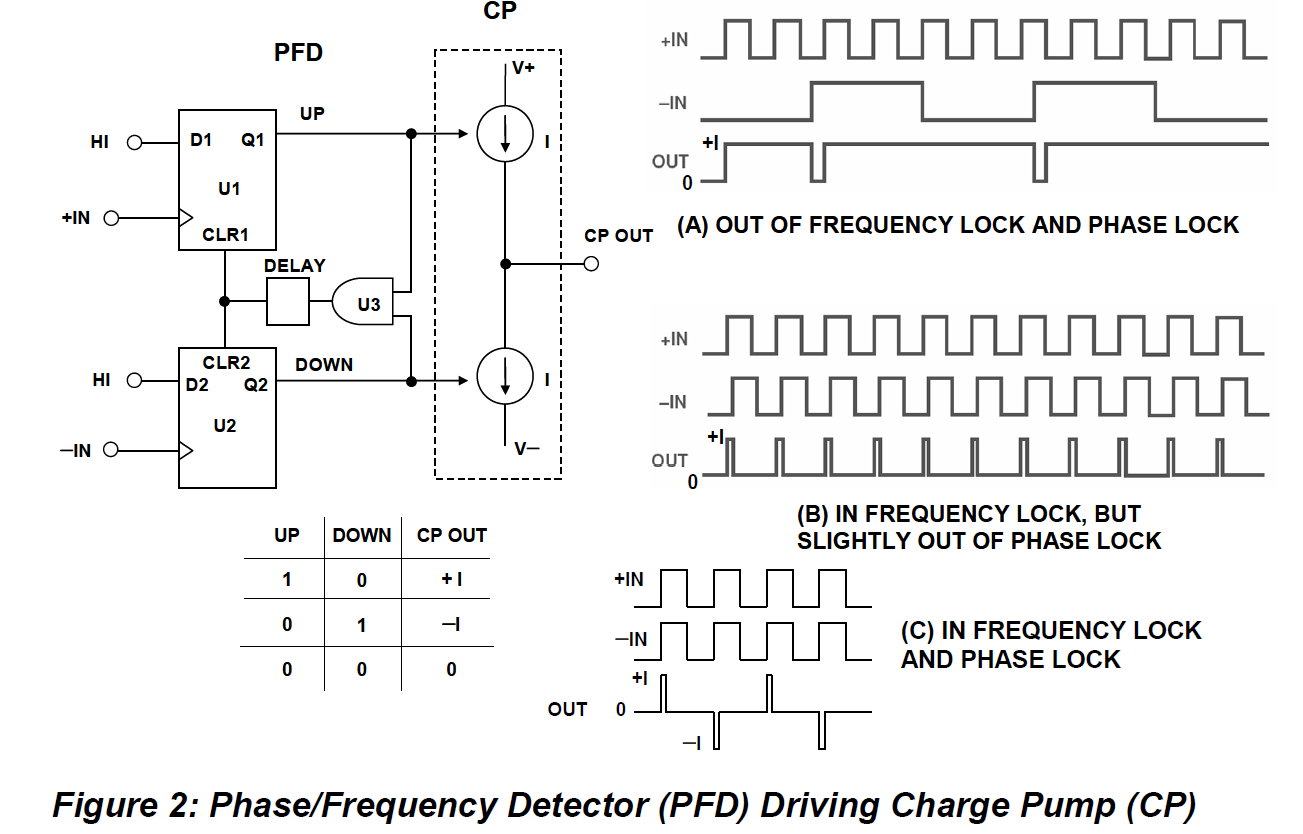

数字鉴相器

- w + I N > w − I N w_{+IN}>w_{-IN} w+IN>w−IN, O U T OUT OUT高电平比较多,CP充电,VCO调大 w − I N w_{-IN} w−IN

- w + I N < w − I N w_{+IN}<w_{-IN} w+IN<w−IN, O U T OUT OUT低电平比较多,CP放电,VCO调小 w − I N w_{-IN} w−IN

- 频率、相位锁定后,保持平衡

环路滤波器(LF,Loop Filter)

u

c

=

K

d

{

s

i

n

[

(

w

i

+

w

o

)

t

+

θ

i

(

t

)

+

θ

o

(

t

)

]

+

s

i

n

[

(

w

i

−

w

o

)

t

+

θ

i

(

t

)

−

θ

o

(

t

)

]

}

u_c=K_d\{sin[(w_i+w_o)t+\theta_i(t)+\theta_o(t)]+sin[(w_i-w_o)t+\theta_i(t)-\theta_o(t)]\}

uc=Kd{sin[(wi+wo)t+θi(t)+θo(t)]+sin[(wi−wo)t+θi(t)−θo(t)]}

u

d

=

K

d

s

i

n

[

(

w

i

−

w

o

)

t

+

θ

i

(

t

)

−

θ

o

(

t

)

]

u_d=K_dsin[(w_i-w_o)t+\theta_i(t)-\theta_o(t)]

ud=Kdsin[(wi−wo)t+θi(t)−θo(t)]

- 高频窄带滤波器,只让输入信号频率附近的频率通过

- 比如滤除 ( w i + w o ) (w_i+w_o) (wi+wo),留下 ( w i − w o ) (w_i-w_o) (wi−wo)

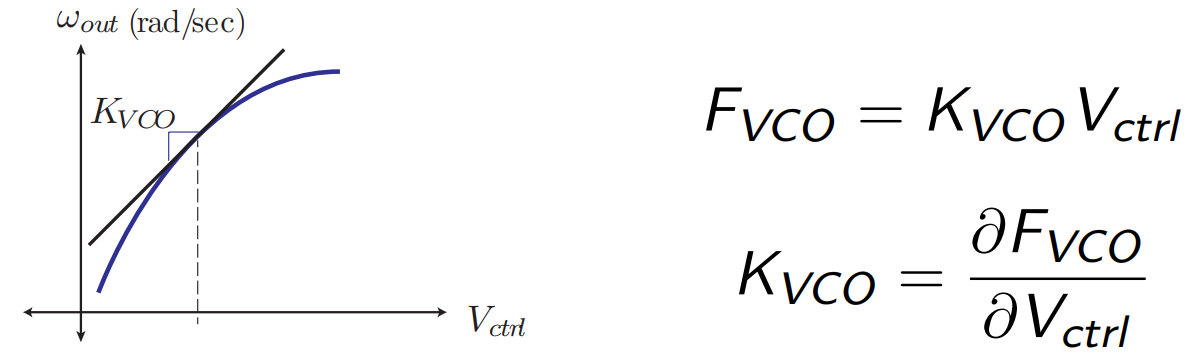

压控振荡器(VCO,Voltage Controlled Oscillator)

u

d

=

K

d

s

i

n

[

(

w

i

−

w

o

)

t

+

θ

i

(

t

)

−

θ

o

(

t

)

]

u_d=K_dsin[(w_i-w_o)t+\theta_i(t)-\theta_o(t)]

ud=Kdsin[(wi−wo)t+θi(t)−θo(t)]

- 根据输入电压调节输出频率

- w i 和 w o w_i和w_o wi和wo比较接近

- w i > w o w_i>w_o wi>wo,输出正电压,VCO调大 w o w_o wo

- w i < w o w_i<w_o wi<wo,输出正电压,VCO调小 w o w_o wo

- 最终 w i = w o w_i=w_o wi=wo, θ i ( t ) − θ o ( t ) \theta_i(t)-\theta_o(t) θi(t)−θo(t)保持固定相位差

- 根据输入电压调节输出频率

应用

时钟恢复(Clock Recovery)

- 一些高速串行数据流发送时没有时钟,接收方要产生一个大致的频率,然后与数据流对齐相位

倾斜校正(Deskewing)

- 当时钟和数据并行传输用于采样数据时,时钟因为在接收采样前被放大,会与数据产生skew,可在接收端使用PLL进行相位对齐

时钟生成

- PLL可将低频的参考时钟(50、100MHz)倍频为处理器时钟(GHz)

频谱展宽(Spread spectrum)

- 电子系统会发射一些噪声信号,这些噪声的频谱通常分布在以工作频率为中心的一个尖峰中,通过PLL可以将信号能量展开到较宽的频谱范围,从而有效降低噪声

检测相位调制信号(AM, Amplitude Modulated)

频率合成

Phase-locked loop

Fundamentals of Phase Locked Loops (PLLs)

锁相环(PLL)及应用

2020

2020

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?