Lab9 V6.0

版本控制

| 版本 | 描述 |

|---|---|

| V0 | Lab3 |

| V1.0 | Lab3 相对V0变化: 修改了文件名,各阶段以_stage结尾(因为if是关键词,所以module名不能叫if,遂改为if_stage,为了统一命名,将所有module后缀加上_stage) 删除了imm_sign信号(默认对立即数进行有符号数扩展) 由于对sw指令进行了重新理解:无论如何都是需要将rt_data传递给EXE阶段,故将部分译码逻辑进行后移至EXE阶段,避免id_to_exe_data总线过于庞大 将ins_shmat剔除出id_to_exe_data,因为imm包括ins_shamt 对信号进行重命名(例如在ID阶段有个信号叫rf_we,最终要传递给WB阶段,那么在EXE阶段,该信号叫作exe_rf_we,同理mem_rf_we,wb_rf_we),不然都叫rf_we,Debug的时候太痛苦了。 |

| V2.0 | Lab4 相对V1.0的变化 引入`ifdef-`else-`endif来实现相对V1.0的代码增量 增加了旁路控制,减少流水线阻塞(因为增加了旁路,所以修改了ID、EXE、MEM的接口) 修改了ready_go命令,用于控制流水线的阻塞 |

| V3.0 | Lab6(加载的是func_lab6的.coe文件,而不是func_lab5的,因为没有func_lab5这个东西) 相对V2.0的变化:电路细节变化详见:“CPU设计实战电路图”,图中Lab6的变化均以红色背景的方框框起来,并以黄色背景的“Lab6复用/新增信号”标注。本lab6.docx中,新增及修改的信号以红色标注。 删掉了ALU.v的接口,将alu_shamt合并至data_1,方便对新加指令sllv、srlv、srav的数据通路的复用 增加了ID.v中的alu_add的“或门”的输入 扩充了id_to_exe_data总线数据, 因为alu_op扩充了新的指令 添加了imm_zero_ext信号 修改了ins_R、ins_J、ins_I,因为增加了新的指令 乘法器和除法器调用vivado的IP,其周期参数化可配置设计 乘法和除法结果存放的寄存器HI/LO放在WB.v中 增加了sfr.v,用于特殊寄存器的存储 增加了mul_div.v,用于处理乘法和除法。增加了mul.v用于处理乘法,增加了divu.v用于处理无符号除法,增加了divs.v用于处理有符号除法 修改了id_to_exe_data,添加了新信号:imm_zero_ext_en 修改了id_to_exe_data,扩充了alu_op的位宽,并将alu_op调整至id_to_exe_data的最高位,方便未来扩充指令 |

| V4.0 | Lab7 修改了alu_op的位宽 新增了两个bus:lw_bus、sw_bus,同时将mem_rd整合至lw_bus,将mem_we整合至sw_bus 扩大了id_to_exe_data lw_bus传递至MEM阶段结束,sw_bus传递至EXE阶段结束 修改了旁路,之前都是lw的旁路,这里将其扩充了lb、lbu、lh、lhu、lwl、lwr |

| V5.0 | Lab8 (对应第7章任务一):添加syscall例外支持 增加MTC0、MFC0、ERET指令 增加CP0寄存器Status、Cause、EPC 增加SYSCALL指令 新建SSR.v(即system registers),是ID.v的子模块 为ID、EXE、MEM、WB级增加了flush信号,用于将数据清零 |

| V6.0 | 添加break指令断点例外 添加地址错、整数溢出、保留指令例外 增加CP0寄存器Count、Compare、BadVAddr 增加时钟中断 增加6个硬中断 增加2个软件中断 |

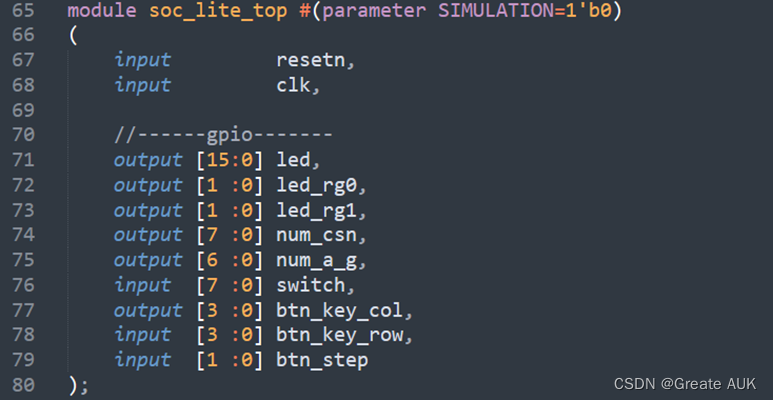

Top顶层

接口信号

MYCPU_TOP.v(TOP)

| 名称 | 宽度 | 方向 | 描述 |

|---|---|---|---|

| 时钟与复位 | |||

| clk | 1 | I | 时钟信号,来自clk_pll的输出时钟 |

| resetn | 1 | I | 复位信号,低电平同步复位 |

| 取指端访存接口 | |||

| inst_sram_en | 1 | O | 指令RAM使能信号,高电平有效 |

| inst_sram_wen | 4 | O | 指令RAM字节写使能信号,高电平有效 |

| inst_sram_addr | 32 | O | 指令RMA读写地址,字节寻址 |

| inst_sram_wdata | 32 | O | 指令RAM写数据 |

| inst_sram_rdata | 32 | I | 指令RAM读数据 |

| 数据端访存接口 | |||

| data_sram_en | 1 | O | 数据RAM使能信号,高电平有效 |

| data_sram_wen | 4 | O | 数据RAM字节写使能信号,高电平有效 |

| data_sram_addr | 32 | O | 数据RAM读写地址,字节寻址 |

| data_sram_wdata | 32 | O | 数据RAM写数据 |

| data_sram_rdata | 32 | I | 数据RAM读数据 |

| debug信号,供验证平台使用 | |||

| debug_wb_pc | 32 | O | 写回级(多周期最后一级)的PC,需要myCPU里将PC一路传递到写回级 |

| debug_wb_rf_wen | 4 | O | 写回级写寄存器堆(regfiles)的写使能,为字节使能,如果myCPU写regfiles为单字节写使能,则将写使能扩展成4位即可 |

| debug_wb_rf_wnum | 5 | O | 写回级写regfiles的目的寄存器号 |

| debug_wb_rf_wdata | 32 | O | 写回级写regfiles的写数据 |

接口时序

略(MIPS经典五级流水线)

代码结构

MYCPU_TOP.v

|____IF.v

|____ID.v

|____RF.v(2个读端口,1个写端口)

|____SFR.v(1个读端口,2个写端口)

|____SSR.v

|____EXE.v

|____ALU.v

|____MUL_DIV.v(专门处理乘法和除法)

|____MUL.v

|____DIVU.v

|____DIVS.v

|____MEM.v

|____WB.v

|____MYCPU.h

DATA_RAM.v

IF.v(修改为IF_STAGE,因为会与关键词if冲突)

接口信号

| 名称 | 宽度 | 方向 | 描述 |

|---|---|---|---|

| 时钟与复位 | |||

| clk | 1 | I | 时钟信号,来自clk_pll的输出时钟 |

| resetn | 1 | I | 复位信号,低电平同步复位 |

| 与TOP | |||

| inst_sram_en | 1 | O | RAM使能信号,高电平有效 |

| inst_sram_wen | 4 | O | RAM字节写使能信号,高电平有效 |

| inst_sram_addr | 32 | O | RMA读写地址,字节寻址 |

| inst_sram_wdata | 32 | O | RAM写数据 |

| inst_sram_rdata | 32 | I | RAM读数据 |

| 与ID | |||

| id_to_if_allowin | 1 | I | pipe allowin |

| if_to_id_vld | 1 | O | pipe valid |

| if_to_id_data | 64 | O | pipe data(instruction 32-bits, pc 32-bits) |

| jump_bus | 33 | I | branch instructions(enable 1bit,address 32-bits) |

接口时序

ID.v

接口信号

| 名称 | 宽度 | 方向 | 描述 |

|---|---|---|---|

| 时钟与复位 | |||

| clk | 1 | I | 时钟信号,来自clk_pll的输出时钟 |

| resetn | 1 | I | 复位信号,低电平同步复位 |

| 与IF | |||

| id_to_if_allowin | 1 | O | pipe allowin |

| if_to_id_vld | 1 | I | pipe valid |

| if_to_id_data | 64 | I | pipe data(instruction 32-bits, pc 32-bits) |

| jump_bus | 33 | O | branch instructions(enable 1bit,address 32-bits) |

| 与EXE | |||

| id_flush | 1 | I | 将id_data给清零 |

| exe_front_flush | 1 | O | 将exe_data给清零 |

| id_flush | 1 | I | 将id_data给清零 |

| exe_to_id_allowin | 1 | I | pipe allowin |

| id_to_exe_vld | 1 | O | pipe valid |

| id_to_exe_data | 169 | O | {alu_op:21, shamt_is_shamt:1, imm_zero_ext_en:1, ins_R:1, ins_I:1, imm:16, mem_rd:1, mem_we:1, rf_we:1, rf_dst_addr:5, rt_data:32, rs_sfr_data_2:32, pc:32} 5:id_ctr_op:{ 4:ov_ins_pre 3:err_reverve 2:c0_has_int 1:break 0:syscall } , alu_op:22, shamt_is_shamt:1, imm_zero_ext_en:1, ins_R:1, ins_I:1, imm:16, lwx_bus_less2:8, swx_bus:9(增加了ins_sw), rf_we:4, rf_dst_addr:5, rt_data:32, rs_sfr_data_2:32, pc:32} |

| exe_bypass_bus | 38 | I | {exe_rf_we:1, exe_rf_dst_addr:5, exe_rf_data:32} |

| exe_to_id_sfr_bus | 76 | I | [75] exe_sfr_we1 [74:70] exe_sfr_w_addr1 [69:38] exe_sfr_data1 [37] exe_sfr_we2 [36:32] exe_sfr_w_addr2 [31:0] exe_sfr_data2 |

| lwx_bus_less2 将其合并至id_to_exe_data中 | 10 | O | lwx类总线: ins_lb: 1, ins_lbu: 1, ins_lh: 1, ins_lhu: 1, ins_lwl: 1, ins_lwr: 1, ins_lw: 1, rs_low2: 2 mem_rd: 1 |

| swx_bus 将其合并至id_to_exe_data中 | 9 | O | swx类总线: ins_sw:1 ins_sb: 1, ins_sh: 1, ins_swl: 1, ins_swr: 1, mem_we[3:0]: 4 |

| mul_div_busy | 1 | I | 正在进行乘法或除法运算 |

| 与MEM | |||

| mem_bypass_bus | 38 | I | {mem_rf_we:1, mem_rf_dst_addr:5, mem_rf_data:32} |

| 与WB | |||

| wb_to_rf_bus | 41 | I | {rf_we:4, rf_addr:5, rf_data:32} |

| wb_exc_bus | 48 | I | 详见:3.4节 pc:32 c0_op:4 c0_int:6 c0_excode:5 exc:1 |

接口信号(RF.v)

| 名称 | 宽度 | 方向 | 描述 |

|---|---|---|---|

| 时钟与复位 | |||

| clk | 1 | I | 时钟信号,来自clk_pll的输出时钟 |

| 与ID内部信号 | |||

| rf_r_addr1 | 5 | I | RF读地址1 |

| rf_r_data1 | 32 | O | RF读数据1 |

| rf_r_addr2 | 5 | I | RF读地址2 |

| rf_r_data2 | 32 | O | RF读数据2 |

| rf_wen1 | 4 | I | RF写使能1 |

| rf_w_addr1 | 5 | I | RF写地址1 |

| rf_w_data1 | 32 | O | RF写数据1 |

接口信号(SFR)

当写入同一地址时,以sfr_we_1优先

| 名称 | 宽度 | 方向 | 描述 |

|---|---|---|---|

| 时钟与复位 | |||

| clk | 1 | I | 时钟信号,来自clk_pll的输出时钟 |

| resetn | 1 | I | 复位信号,低电平同步复位 |

| 与ID内部信号 | |||

| sfr_r_addr1 | 5 | I | SFR读地址1 |

| sfr_r_data1 | 32 | O | SFR读数据1 |

| sfr_we_1 | 1 | I | SFR写使能1 |

| sfr_w_addr1 | 5 | I | SFR写地址1 |

| sfr_w_data1 | 32 | I | SFR写数据1 |

| sfr_we_2 | 1 | I | SFR写使能2 |

| sfr_w_addr2 | 5 | I | SFR写地址2 |

| sfr_w_data2 | 32 | I | SFR写数据2 |

接口信号(SSR)

| 名称 | 宽度 | 方向 | 描述 |

|---|---|---|---|

| 时钟与复位 | |||

| clk | 1 | I | 时钟信号,来自clk_pll的输出时钟 |

| resetn | 1 | I | 复位信号,低电平同步复位 |

| 与ID内部信号 | |||

| c0_op | 4 | I | 3:保留着,先置为0 2:wb_bd:branch delay slot(本Lab8版本可以恒置为0) 1:wb_exc:由WB传回来的例外 0:syscall |

| c0_eret | 1 | I | eret |

| c0_int | 6 | I | 中断 |

| c0_excode | 5 | I | 由WB传回来的excode |

| c0_wb_pc | 32 | I | 由WB传回来的PC值 |

| c0_we | 1 | I | SSR写使能(1:写,0:读) |

| c0_addr | 8 | I | SSR写/读地址 [7:5]:c0_sel [5:0]:c0_id |

| c0_wdata | 32 | I | SSR写数据 |

| c0_rdata | 32 | O | SSR读数据 |

| c0_has_int | 1 | O | 发生中断 |

接口时序

电路设计

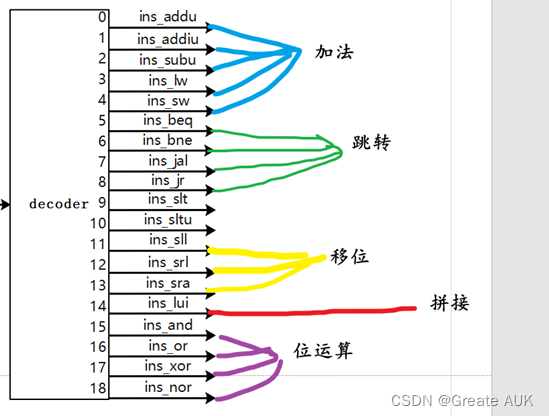

图3-4-1 译码电路分组(注:黄线少画了两条)

根据附录——MIPS指令。由于跳转指令不传递给EXE阶段,直接传递给IF阶段,且为纯组合逻辑输出,有可能成为关键路径,故对跳转指令单独处理。除了跳转指令外,涉及加法(减法归为加法)的指令如图3-4-1所示,即ins_addu、ins_addiu、ins_subu、ins_lw、ins_sw。

对于图3-4-1的拼接运算,可以当作移位运算执行。

EXE.v

接口信号

| 名称 | 宽度 | 方向 | 描述 |

|---|---|---|---|

| 时钟与复位 | |||

| clk | 1 | I | 时钟信号,来自clk_pll的输出时钟 |

| resetn | 1 | I | 复位信号,低电平同步复位 |

| 与TOP(外接的DATA_RAM) | |||

| data_sram_en | 1 | O | 数据RAM使能信号,高电平有效 |

| data_sram_wen | 4 | O | 数据RAM字节写使能信号,高电平有效(4个比特,应该代表32 = 4 bytes) |

| data_sram_addr | 32 | O | 数据RAM读写地址,字节寻址 |

| data_sram_wdata | 32 | O | 数据RAM写数据 |

| 与ID | |||

| id_flush | 1 | O | 将id_data给清零 |

| exe_front_flush | 1 | I | 将exe_data给清零 |

| exe_to_id_allowin | 1 | O | pipe allowin |

| id_to_exe_vld | 1 | I | pipe valid |

| id_to_exe_data | 169 | I | {alu_op:21, shamt_is_shamt:1, imm_zero_ext_en:1, ins_R:1, ins_I:1, imm:16, mem_rd:1, mem_we:1, rf_we:1, rf_dst_addr:5, rt_data:32, rs_sfr_data_2:32, pc:32} 5:exe_ctr_op:{ 4:ov_ins_pre 3:err_reverve 2:c0_has_int 1:break 0:syscall } , alu_op:22, shamt_is_shamt:1, imm_zero_ext_en:1, ins_R:1, ins_I:1, imm:16, lwx_bus_less2:8, swx_bus:9(增加了ins_sw), rf_we:4, rf_dst_addr:5, rt_data:32, rs_sfr_data_2:32, pc:32} |

| exe_bypass_bus | 41 | O | {exe_rf_we:4, exe_rf_dst_addr:5, exe_rf_data:32} |

| exe_to_id_sfr_bus | 76 | O | [75] exe_sfr_we1 [74:70] exe_sfr_w_addr1 [69:38] exe_sfr_data1 [37] exe_sfr_we2 [36:32] exe_sfr_w_addr2 [31:0] exe_sfr_data2 |

| mul_div_busy | 1 | O | 正在进行乘法或除法运算 |

| lwx_bus 将其合并至id_to_exe_data中 | 10 | I | lwx类总线: ins_lb: 1, ins_lbu: 1, ins_lh: 1, ins_lhu: 1, ins_lwl: 1, ins_lwr: 1, ins_lw: 1, rs_low2: 2 mem_rd: 1 |

| swx_bus 将其合并至id_to_exe_data中 | 9 | I | swx类总线: ins_sw:1, ins_sb: 1, ins_sh: 1, ins_swl: 1, ins_swr: 1, mem_we[3:0]: 4 |

| 与MEM | |||

| mem_front_flush | 1 | O | 将mem_data给清零 |

| exe_flush | 1 | I | 将exe_data给清零 |

| id_flush | 1 | O | 将id_data给清零 |

| mem_to_id_allowin | 1 | I | pipe allowin |

| exe_to_mem_vld | 1 | O | pipe valid |

| exe_to_mem_data | 99 | O | {mem_rd:1, rf_we:1, rf_dst_addr:5, pc:32(其实可以删掉pc,这里是debug显示用的,可以叫debug_pc), exe_result:32} {exe_exc_bus:16, lwx_bus: 10, rf_we:4, rf_dst_addr:5, pc:32(其实可以删掉pc,这里是debug显示用的,可以叫debug_pc), exe_result:32} |

| lwx_bus 将其合并至id_to_exe_data中 | 10 | O | lwx类总线: ins_lb: 1, ins_lbu: 1, ins_lh: 1, ins_lhu: 1, ins_lwl: 1, ins_lwr: 1, ins_lw: 1, rs_low2: 2 mem_rd: 1 |

| exe_exc_bus (归于exe_to_mem_data) | 16 | O | 详见:3.4节 c0_op:4 c0_int:6 c0_excode:5 exc:1 |

接口信号(ALU.v)

暂时不需要时钟和复位,纯组合逻辑

| 名称 | 宽度 | 方向 | 描述 |

|---|---|---|---|

| 时钟与复位 | |||

| clk | 1 | I | 时钟信号,来自clk_pll的输出时钟 |

| resetn | 1 | I | 复位信号,低电平同步复位 |

| 与ID内部信号 | |||

| alu_shamt | 6 | I | ALU移位(R-指令的shamt部分) |

| alu_op | 19 | I | ALU操作(加、减、乘除、位运算) |

| alu_add_ov | 1 | O | 加法/减法溢出 |

| alu_din1 | 32 | I | ALU输入1 |

| alu_din2 | 32 | I | ALU输入2 |

| alu_out | 32 | O | ALU输出 |

| mul_div_busy | 1 | O | 正在进行乘法或除法运算 |

接口信号(MUL_DIV.v)

| 名称 | 宽度 | 方向 | 描述 |

|---|---|---|---|

| 时钟与复位 | |||

| clk | 1 | I | 时钟信号,来自clk_pll的输出时钟 |

| resetn | 1 | I | 复位信号,低电平同步复位 |

| 与ALU内部信号 | |||

| alu_mult | 1 | I | 有符号乘 |

| alu_multu | 1 | I | 无符号乘 |

| alu_div | 1 | I | 有符号除 |

| alu_divu | 1 | I | 无符号除 |

| alu_mthi | 1 | I | 将寄存器 rs 的值写入到 HI 寄存器中 |

| alu_mtlo | 1 | I | 将寄存器 rs 的值写入到LO寄存器中 |

| alu_din1 | 32 | I | ALU输入1 |

| alu_din2 | 32 | I | ALU输入2 |

| exe_to_id_sfr_bus | 76 | O | [75] exe_sfr_we1 [74:70] exe_sfr_w_addr1 [69:38] exe_sfr_data1 [37] exe_sfr_we2 [36:32] exe_sfr_w_addr2 [31:0] exe_sfr_data2 |

| mul_div_busy | 1 | O | 正在进行乘法或除法运算 |

接口信号MUL.v

| 名称 | 宽度 | 方向 | 描述 |

|---|---|---|---|

| 时钟与复位 | |||

| clk | 1 | I | 时钟信号,来自clk_pll的输出时钟 |

| resetn | 1 | I | 复位信号,低电平同步复位 |

| 与ALU内部信号 | |||

| mul_din_vld | 1 | I | 数据有效信号 |

| mul_din1 | 33 | I | 乘数1 |

| mul_din2 | 33 | I | 乘数2 |

| mul_result_hi | 32 | O | 乘法高32位 |

| mul_result_lo | 32 | O | 乘法低32位 |

接口信号DIVU.v

| 名称 | 宽度 | 方向 | 描述 |

|---|---|---|---|

| 时钟与复位 | |||

| clk | 1 | I | 时钟信号,来自clk_pll的输出时钟 |

| resetn | 1 | I | 复位信号,低电平同步复位 |

| 与ALU内部信号 | |||

| divu_din_vld | 1 | I | 数据有效信号 |

| divu_din1 | 33 | I | 被除数 |

| divu_din2 | 33 | I | 除数 |

| divu_hi | 32 | O | 结果高32位 |

| divu_lo | 32 | O | 结果低32位 |

接口信号DIVS.v

| 名称 | 宽度 | 方向 | 描述 |

|---|---|---|---|

| 时钟与复位 | |||

| clk | 1 | I | 时钟信号,来自clk_pll的输出时钟 |

| resetn | 1 | I | 复位信号,低电平同步复位 |

| 与ALU内部信号 | |||

| divs_din_vld | 1 | I | 数据有效信号 |

| divs_din1 | 33 | I | 被除数 |

| divs_din2 | 33 | I | 除数 |

| divs_hi | 32 | O | 结果高32位 |

| divs_lo | 32 | O | 结果低32位 |

接口时序

MEM.v

接口信号

| 名称 | 宽度 | 方向 | 描述 |

|---|---|---|---|

| 时钟与复位 | |||

| clk | 1 | I | 时钟信号,来自clk_pll的输出时钟 |

| resetn | 1 | I | 复位信号,低电平同步复位 |

| 与TOP(外接的DATA_RAM) | |||

| data_sram_rdata | 32 | I | 数据RAM读数据 |

| 与EXE | |||

| mem_front_flush | 1 | I | 将mem_data给清零 |

| exe_flush | 1 | O | 将exe_data给清零 |

| mem_to_exe_allowin | 1 | O | pipe allowin |

| exe_to_mem_vld | 1 | I | pipe valid |

| exe_to_mem_data | 99 | I | {mem_rd:1, rf_we:1, rf_dst_addr:5, pc:32(其实可以删掉pc,这里是debug显示用的,可以叫debug_pc), exe_result:32} {exe_exc_bus:16, lwx_bus: 10, rf_we:4, rf_dst_addr:5, pc:32(其实可以删掉pc,这里是debug显示用的,可以叫debug_pc), exe_result:32} |

| lwx_bus 将其合并至id_to_exe_data中 | 10 | I | lwx类总线: ins_lb: 1, ins_lbu: 1, ins_lh: 1, ins_lhu: 1, ins_lwl: 1, ins_lwr: 1, ins_lw: 1, rs_low2: 2 mem_rd: 1 |

| exe_exc_bus (归为exe_to_mem_data) | 16 | I | 详见:3.4节 c0_op:4 c0_int:6 c0_excode:5 exc:1 |

| 与WB | |||

| mem_flush | 1 | I | 将mem_data给清零 |

| wb_front_flush | 1 | O | 将wb_data给清零 |

| wb_to_mem_allowin | 1 | I | pipe allowin |

| mem_to_wb_vld | 1 | O | pipe valid |

| mem_to_wb_data | 89 | O | {mem_exc_bus:16, rf_we:4, rf_dst_addr:5, mem_result:32, pc:32(其实可以删掉pc,这里是debug显示用的,可以叫debug_pc)} |

| mem_exc_bus (归为mem_to_wb_data) | 16 | O | 详见:3.4节 c0_op:4 c0_int:6 c0_excode:5 exc:1 |

| 与ID | |||

| mem_bypass_bus | 38 | O | {mem_rf_we:4, mem_rf_dst_addr:5, mem_rf_data:32} |

| wb_exc_bus | 16 | O | 详见:3.4节 c0_op:4 c0_int:6 c0_excode:5 exc:1 |

WB.v

接口信号

| 名称 | 宽度 | 方向 | 描述 |

|---|---|---|---|

| 时钟与复位 | |||

| clk | 1 | I | 时钟信号,来自clk_pll的输出时钟 |

| resetn | 1 | I | 复位信号,低电平同步复位 |

| 与TOP | |||

| debug_wb_pc | 32 | O | 写回级(多周期最后一级)的PC,需要myCPU里将PC一路传递到写回级(与原书保持一致) |

| debug_wb_rf_wen | 4 | O | 写回级写寄存器堆(regfiles)的写使能,为字节使能,如果myCPU写regfiles为单字节写使能,则将写使能扩展成4位即可(与原书保持一致) |

| debug_wb_rf_wnum | 5 | O | 写回级写regfiles的目的寄存器号(与原书保持一致) |

| debug_wb_rf_wdata | 32 | O | 写回级写regfiles的写数据(与原书保持一致) |

| 与MEM | |||

| mem_flush | 1 | O | 将mem_data给清零 |

| wb_front_flush | 1 | I | 将wb_data给清零 |

| wb_to_mem_allowin | 1 | O | pipe allowin |

| mem_to_wb_vld | 1 | I | pipe valid |

| mem_to_wb_data | 89 | I | { mem_exc_bus:16, rf_we:4, rf_dst_addr:5, mem_result:32, pc:32(其实可以删掉pc,这里是debug显示用的,可以叫debug_pc)} |

| mem_exc_bus (归于mem_to_wb_data) | 16 | I | 详见:3.4节 c0_op:4 c0_int:6 c0_excode:5 exc:1 |

| 与ID | |||

| wb_to_rf_bus | 41 | O | {rf_we:4, rf_addr:5, rf_data:32} |

| wb_exc_bus | 48 | O | 详见:3.4节 pc:32 c0_op:4 c0_int:6 c0_excode:5 exc:1 |

接口时序

附录——参考

附录——原书指令

| 指令 | sel_nextpc | inst_ram_wen | inst_ram_wen | sel_alu_src1 | sel_alu_src2 | alu_op | data_ram_en | data_ram_wen | rf_we | sel_rf_dst | sel_rf_res |

|---|---|---|---|---|---|---|---|---|---|---|---|

| ADDU | 0001 | 1 | 0 | 001 | 001 | 000000000001 | 0 | 0 | 1 | 001 | 0 |

| ADDIU | 0001 | 1 | 0 | 001 | 010 | 000000000001 | 0 | 0 | 1 | 010 | 0 |

| SUBU | 0001 | 1 | 0 | 001 | 001 | 000000000010 | 0 | 0 | 1 | 001 | 0 |

| LW | 0001 | 1 | 0 | 001 | 010 | 000000000001 | 1 | 0 | 1 | 010 | 1 |

| SW | 0001 | 1 | 0 | 001 | 010 | 000000000001 | 1 | 1 | 0 | 000 | 0 |

| BEQ | 0010 | 1 | 0 | 000 | 000 | 000000000000 | 0 | 0 | 0 | 000 | 0 |

| BNE | 0010 | 1 | 0 | 000 | 000 | 000000000000 | 0 | 0 | 0 | 000 | 0 |

| JAL | 0100 | 1 | 0 | 010 | 100 | 000000000001 | 0 | 0 | 1 | 100 | 0 |

| JR | 1000 | 1 | 0 | 000 | 000 | 000000000000 | 0 | 0 | 0 | 000 | 0 |

| SLT | 0001 | 1 | 0 | 001 | 001 | 000000000100 | 0 | 0 | 1 | 001 | 0 |

| SLTU | 0001 | 1 | 0 | 001 | 001 | 000000001000 | 0 | 0 | 1 | 001 | 0 |

| SLL | 0001 | 1 | 0 | 100 | 001 | 000100000000 | 0 | 0 | 1 | 001 | 0 |

| SRL | 0001 | 1 | 0 | 100 | 001 | 001000000000 | 0 | 0 | 1 | 001 | 0 |

| SRA | 0001 | 1 | 0 | 100 | 001 | 010000000000 | 0 | 0 | 1 | 001 | 0 |

| LUI | 0001 | 1 | 0 | 000 | 010 | 100000000000 | 0 | 0 | 1 | 010 | 0 |

| AND | 0001 | 1 | 0 | 001 | 001 | 000000010000 | 0 | 0 | 1 | 001 | 0 |

| OR | 0001 | 1 | 0 | 001 | 001 | 000001000000 | 0 | 0 | 1 | 001 | 0 |

| XOR | 0001 | 1 | 0 | 001 | 001 | 000010000000 | 0 | 0 | 1 | 001 | 0 |

| NOR | 0001 | 1 | 0 | 001 | 001 | 000000100000 | 0 | 0 | 1 | 001 | 0 |

LAB9——后记

前述

发现有些寄存器是Lab9的,但是已经在Lab8写过了,那就算Lab8的吧,不再修改了。

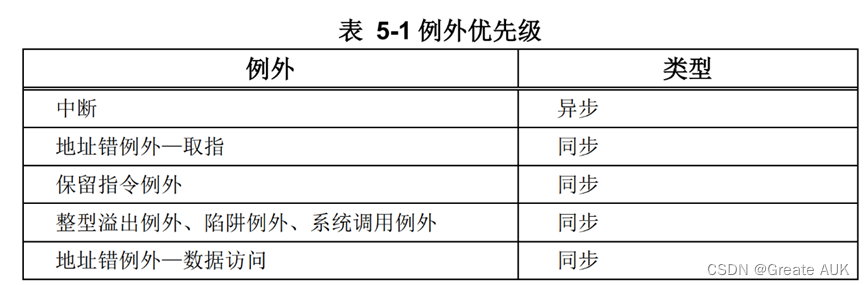

中断优先级

Lab8只有syscall这一个例外,因此不需要考虑中断的优先级,但是Lab9增加许多例外,因此是需要考虑中断的优先级的,即:当一条指令同时触发多个例外时的优先级:

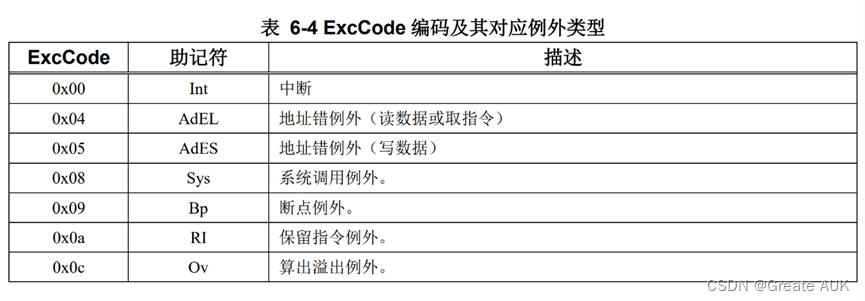

ExcCode编码

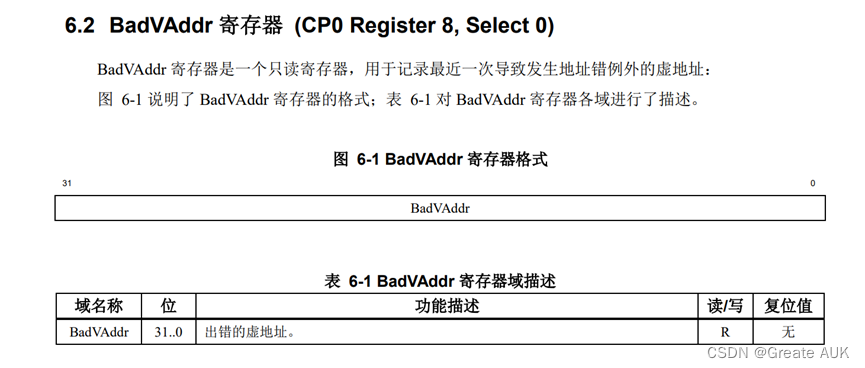

BadVAddr

原书解释:“BadVAddr寄存器整体只有一个域,其更新来源只有一个,即报地址错例外的时候将导致出错的虚地址写入该寄存器。这里要注意以下几点:首先记录的是虚地址;其次如果是地址错例外,出错的虚地址就是PC;最后,如果导致地址出错的原因是地址非对齐,那BadVAddr的低两位要严格地更新为非对齐地址的低两位。不要为了省几个触发器而把各级流水级缓存中保存的PC的最低两位强行转为0。”

需要注意的是BadVAddr寄存器是对软件是只读不可写的。

本人不理解原书第7章的P179页对BadVAddr的Verilog代码的描述,为什么只有ADEL,而没有ADES,大家都是地址错误啊,此处存疑。

- BadVAddr涉及的指令有:lw/lb/lbu/lh/lhu/sw/sb/sh

| 指令 | ||

|---|---|---|

| ADEL | ADES | |

| lw | sw | 4的整数倍 |

| lh | sh | 2的整数倍 |

| lhu |

- 经本人遍历load/store想着指令,得出以下结论:BadVAddr不涉及:lb/lbu/sb/lwr/lwl/swr/swl

count 与 compare

比较简单,按书上的来。

中断

-

原本我对中断处理毫无头绪,后发现原书P169有言:“has_int = ((Cause.IP[7:0] & Status.IM[7:0]) != 8’h00) && Status.IE1’b1 && Status.EXL1’b0;”于是本人直接抄此代码

-

原书:“简单解释一下,就是外部的中断通过处理器核的引脚设置Cause寄存器中对应的中断状态位,当这个中断状态位自身对应的使能位有效且全局使能位也有效,那么CPU内部就认为接收到中断。显然,这里CPU并不在意到底接收到的是一个外部中断还是多个外部中断。当确实同时接收到多个中断时,后续的处理交给软件上的中断处理函数进行。”

-

有人has_int之后,之前将has_int引到ID阶段,把has_int当作指令处理,即类似syscall指令进行处理,这样就清晰多了。

-

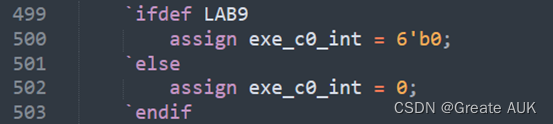

硬件中断是软件只读不可写的,那怎么处理Cause寄存器中的6个bits的硬件中断呢?观察顶层:

好像可以和btn或switch进行相连,本人不确定如何处理,暂时将其置为全零:

-

-

-

整数溢出

| 指令 | |||

|---|---|---|---|

| ADD | 有例外 | ADDIU | 无例外 |

| ADDI | |||

| SUB | SUBU | 无例外 |

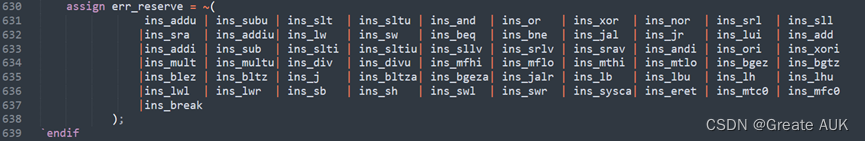

保留指令例外

-

原书:“当执行一条未实现的指令时,触发保留指令例外”

-

本人直接这样处理了:

-

本文详细介绍了CPU设计中的Lab9,涵盖了五级流水线的各个阶段,包括IF、ID、EXE、MEM和WB。讨论了接口信号、时序设计以及特殊指令处理,如跳转指令和乘法除法单元。还提到了中断优先级、ExcCode编码、BadVAddr寄存器的工作原理以及中断处理机制。

本文详细介绍了CPU设计中的Lab9,涵盖了五级流水线的各个阶段,包括IF、ID、EXE、MEM和WB。讨论了接口信号、时序设计以及特殊指令处理,如跳转指令和乘法除法单元。还提到了中断优先级、ExcCode编码、BadVAddr寄存器的工作原理以及中断处理机制。

139

139

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?