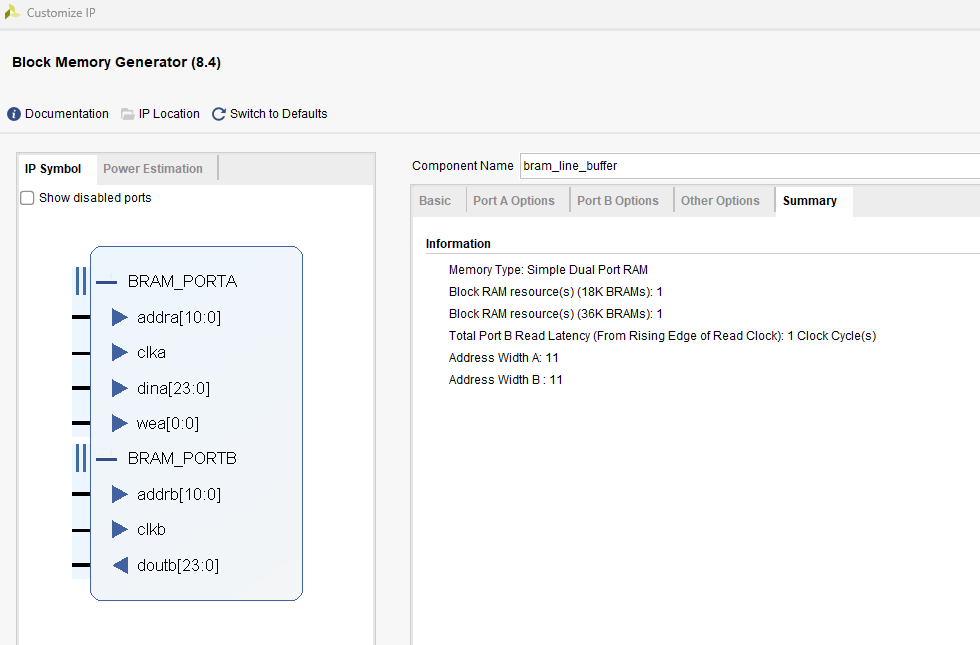

利用bram形成双缓冲,如下图配置所示:

wr_flag 表明 buffer0写 还是 buffer1写 rd_flag 表明 buffer0读 还是 buffer1读

通过写入逻辑控制(结合wr_finish) 写哪个buffer ;写地址 进而控制ip的写使能

通过状态缓存来跳转buffer的写和读

通过读取逻辑(结合rd_finish) 读哪个buffer ;读地址

最后通过时序控制,调整输出数据及数据有效对齐

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Description: 水平镜像

//////////////////////////////////////////////////////////////////////////////////

module image_horizion_flip(

input wire clk,

input wire reset,

input wire [10:0] img_width,

input wire val

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1034

1034

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?