基于时钟重定时的低功耗逐次逼近型模数转换器设计

一、引言

高性能芯片的发明在实际的超大规模集成电路设计中非常重要。在芯片产业中,模拟器件在光学系统、高速存储器、传感器、无线系统和高速微处理器中发挥着关键作用。将自然信号转换为数字信号需要在电路放大、增益、功耗、速度和精度等多个参数之间进行权衡。本文采用低功耗设计方法来实现模拟电路设计。电流镜、放大器和电压参考电路是模拟设计中的一些常见基本模块。模拟混合信号电路中的另一个关键组件是模数转换器(ADC)和数模转换器(DAC)。在先进的电子设备中,低功耗高分辨率的模数转换器(ADC)设备是关键部件之一。实现 ADC的一般框图包括采样保持电路、比较器和数模转换器(DAC)等。模数转换器和数模转换器广泛应用于音频放大器、视频编码器、显示电子设备、数据采集系统、校准、软件无线电、电机控制等领域。本文利用时钟重定时技术设计了低功耗重构的数模转换器和模数转换器。

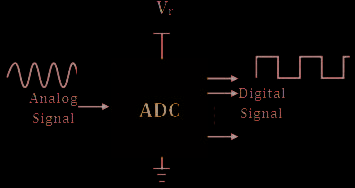

模数信号转换模块的通用符号表示如图1所示。它将模拟信号转换为数字信号,在功耗和速度之间进行权衡 [18]。市场上针对不同应用的常用模数转换器类型,根据速度和分辨率的选择进行分类,如下所示

本文提出了一种低功耗时钟重定时逐次逼近寄存器(SAR)ADC的设计。该架构相较于现有设计具有高能效和紧凑型设计的特点。

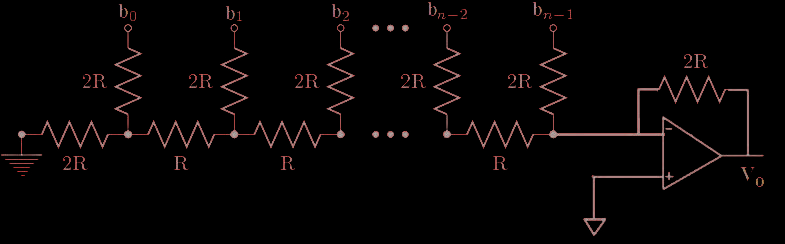

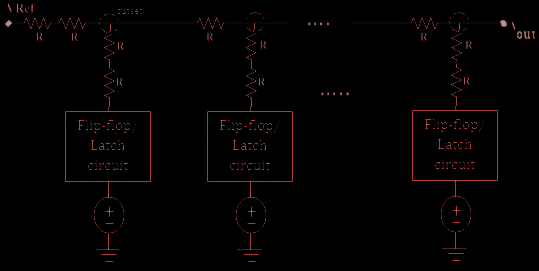

逐次逼近型模数转换器的整体线性度由DAC电路决定。R‐2R电阻网络[14],[18]在逐次逼近型ADC架构中被使用,最初由Bernard M. Gordon实现。采用0.13 μmCMOS工艺技术设计了9位低功耗低压SAR ADC,该设计使用金属氧化物半导体电容器(MOSCAP‐DAC)[16]。本文提出的 SAR‐ADC容差相比现有设计有所改进。N位R‐2R梯形DAC的原理图如图3所示,其需要2:1比例电阻和其参考电压表示为 Vref。当二进制位为1时,开关连接到 Vref;当二进制位为0时,开关连接到地。在公式(2)中bi(i = 1,2,…N)是N位数字输入位,而bN2−N表示输入位的Nth节点。通用N位R‐2R DAC的输出电压由公式(1)描述。

$$

Vo=(b12^{-1}+ b22^{-2}+ b32^{-3}+…+ bN2^{-N})Vref \quad (1)

$$

$$

Vo= Vref \sum_{i=1}^{N-1} \frac{bi}{2^i} \quad (2)

$$

为了提高DAC和ADC的性能水平,许多研究人员提出了不同的架构。碳化硅(SiC) DAC架构[2]在不同温度水平下进行了分析。本文采用8位R‐2R梯形DAC架构对积分非线性(INL)和微分非线性(DNL)值进行了仿真。在高温条件下,SiC DAC表现出更优的性能,因此适用于深井钻探、航空和太空探索应用。基于SiC DAC的逐次逼近寄存器 ADC被设计用于内置自测试应用[3],本文旨在提供一种低成本设计方案。该逐次逼近型模数转换器(SAR ADC)采用新型采样与切换方法[4]进行设计。所提出的电容切换方法在切换过程中突出了两个优点:一个源于采样后阶段,另一个源于最高有效位判定之后。本文成果显示,相较于传统二进制加权DAC,该方案实现了切换能量和面积减小。

针对6位5GS/s 4路交织3位/周期的SAR ADC架构被设计[7],相比现有设计节省了1/3rd硬件部分。为降低设计复杂度,采用了分数型DAC阵列切换方案进行切换控制。实验结果证明,主时钟控制的自举开关方案以及边界检测码覆盖机制具有低功耗和高能效特性。为了改善DAC的整体线性度,提出了一种10位电阻‐浮置电阻串数模转换器(RFR‐DAC)架构[9]。该架构中为液晶显示器(LCD)驱动应用采用了两种不同的电压选择方案。电流舵型数模转换器(DAC)的校准问题已被解决[10],结果通过两个完全校准的温度计码阵列,在不牺牲动态特性的前提下,实现了固有精度水平的提升和高分辨率静态校准水平的实现。采用失配电荷补偿方案设计基于开关电容循环的DAC[13],以减少由电容失配引起的DAC误差。其中一位研究人员使用电流补偿技术,采用(4+12)位分段电压模式方法设计了R‐2R数模转换器[17],结果使设计功耗比原有方案降低了1/5th。

传统方法。在这种方法中,参考电流和低分辨率辅助数模转换器由计算模块以简单的方式进行控制。

在我们之前的一项工作中,提出了积之和项重定时算法用于设计数字应用。架构方程组被简化为积之和方程,并应用割集来插入触发器。提出的重定时方法应用于FIR和 IIR滤波器设计,与现有设计相比降低了功耗。在本提出的工作中,使用时钟重定时设计了模拟混合信号(AMS)设计中的SAR ADC架构,从而实现了低功耗。第二节将简要描述模拟电路重定时的要求。该节还将回顾AMS设计中 NAND门的功耗来源及原理图设计分析。第三和第四节将介绍使用提出的方法设计R‐2R数模转换器和逐次逼近型模数转换器。第五节讨论结果分析,以确定原理图级功耗、分辨率和采样率参数。第六节总结了提出的设计方法。

II. 重新定时低功耗模拟电路

开关功耗、短路功耗和漏电功耗是低功耗单元中最主要的功耗来源 [1]。CMOS电路中三种功耗来源在公式(3)中表示。为了降低CMOS电路设计中的主要功耗来源,必须采用不同的功耗优化技术。在许多设计中,超过 70%的功耗来自于导线和晶体管栅极的充放电,因此降低开关功耗可使模拟器件更加可靠。

$$

P= PSwitching+ PShort−circuit+ PLeakage \quad (3)

$$

其中开关功耗为

$$

Ps= \frac{1}{2} \alpha C_L V_{DD}^2 f \quad (4)

$$

在公式(4)中,f表示时钟频率,VDD表示电源电压,CL是输出负载电容,α是门的开关活动性。利用这一基本方程可形成低功耗重新定时方程,并重点阐述了重新定时原理图的重构。

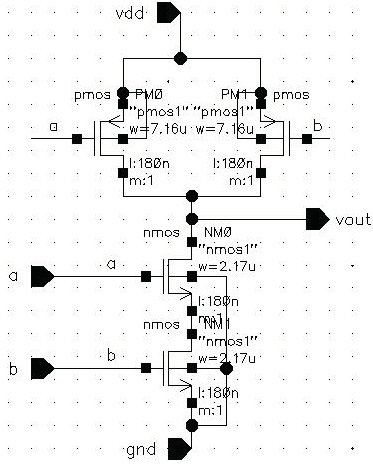

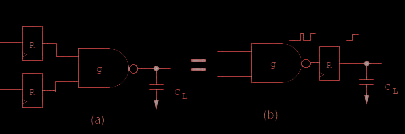

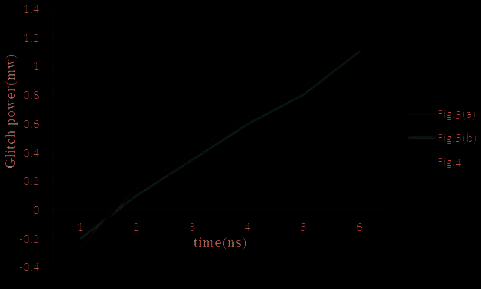

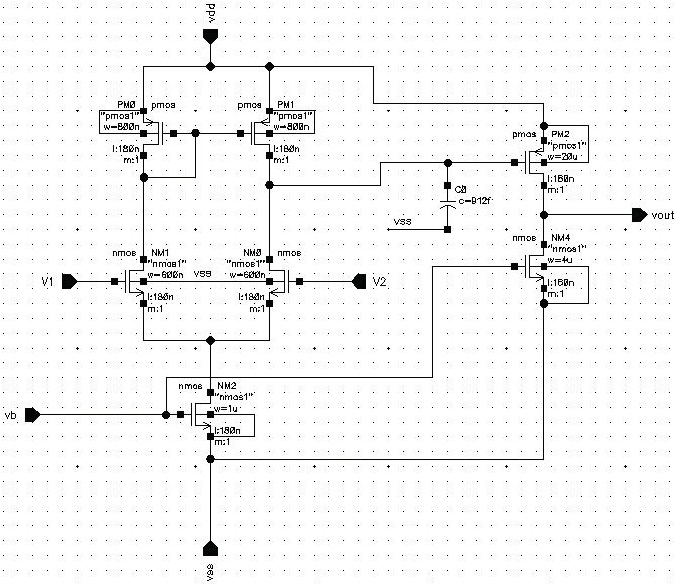

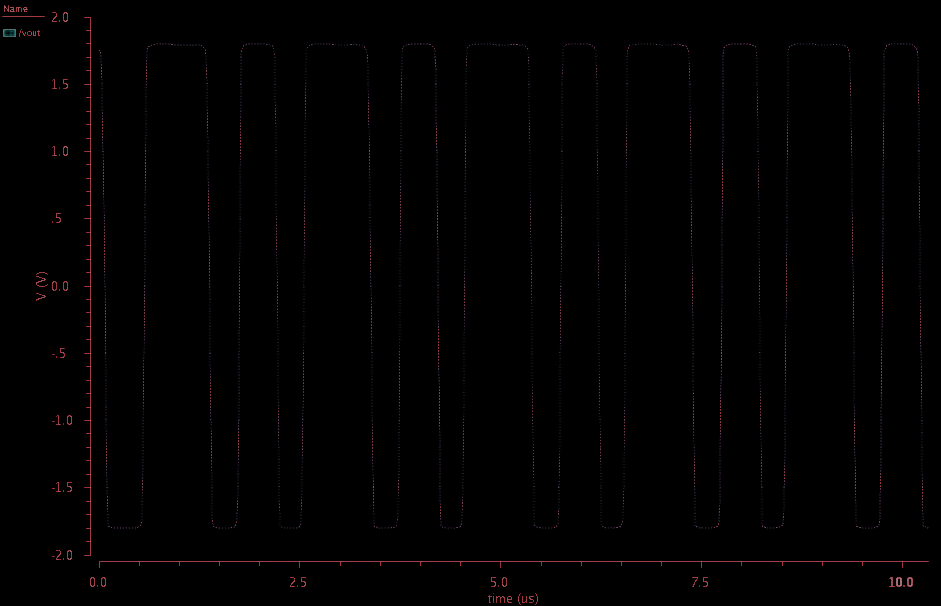

2输入与非门的晶体管级原理图如图4所示,包含两个 P沟道MOS管和N沟道MOS管。P沟道MOS管的源极连接到电源电压 VDD,N沟道MOS管的源极连接到地gnd。仅当两个输入都为高电平时,输出才为低电平;在其他所有情况下,输出均为高电平。输出端的平均开关活动性以及由于开关功耗引起的负载电容由公式(4)表示。在输入跳变期间,有时可能会在输出端产生一些毛刺。本文利用重新定时概念对毛刺功耗进行了分析。使用Virtuoso工具设计了与非门原理图,并生成其瞬态波形。在传统与非门原理图上应用时钟重定时技术,并在与非逻辑的输出端添加触发器(R),如图.5(b)所示。通过Spectre仿真器进行的功耗分析证明了平均

开关功耗小于图4,因此由于时钟置位,额外的触发器实际上降低了功耗。由C. Leiserson. F. Rose首次提出在不损害设计功能的前提下重新定位触发器的概念[5],[6]。该相同概念已被采用以改善 SAR‐ADC的电路性能。在重新定位触发器后,电路中的功耗发生了变化。三种情况(图4、图5(a)和图5(b))下的毛刺功耗均绘制于图6中。结果分析表明,基于触发器的门电路比传统门电路消耗更少的功耗。

III. 提出的设计R‐2R数模转换器的方法

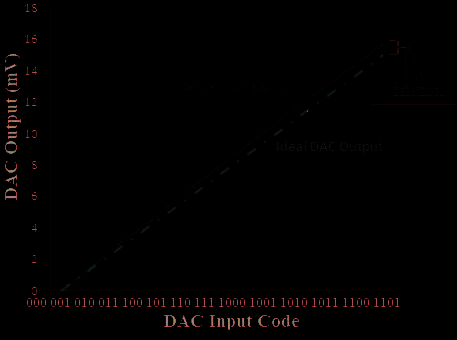

通过找出最长的关键路径,然后重新定位触发器以降低功耗,这是提出的工作的核心思想。割集重定时的概念在[5],[6]中提出,并被继承用于设计双时钟重定时 R‐2R梯形网络。所提出的设计采用负反馈运算放大器来设计DAC结构。电阻梯形输入线连接到运算放大器的同相输入端,并以公共参考地结束。将触发器放置在运算放大器的同相线上,以重新设计10位R‐2R数模转换器原理图,如

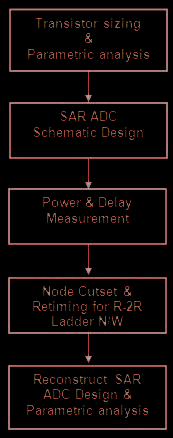

图.7。然后将触发器重新定位到10个不同的输入脉冲上,以改善R‐2R数模转换器的性能。经过重新定时后,如图.8所示,获得的非线性传输特性相比传统特性有所改善。所提出的架构仿真结果表明,在积分非线性(INL)、差分非线性(DNL)和分辨率方面均优于先前提出的结构。时钟重定时 SAR ADC的设计流程如图.10所示。该流程从晶体管尺寸调整特性参数分析开始,随后进行SAR ADC原理图设计和功耗分析,以量化功耗和延迟。将节点割集应用于R‐2R梯形网络,插入触发器并重构R‐2R梯形网络,从而设计SAR ADC。

IV. 使用所提出的R‐2R DAC架构的SAR ADC设计与实现

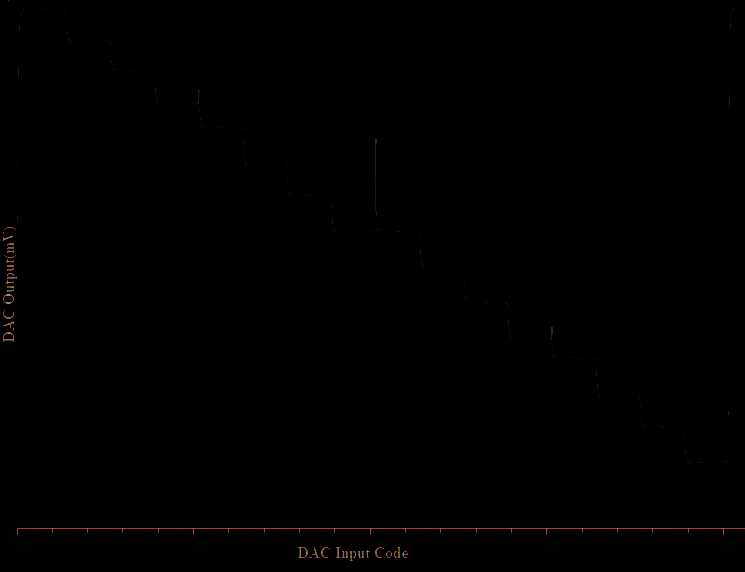

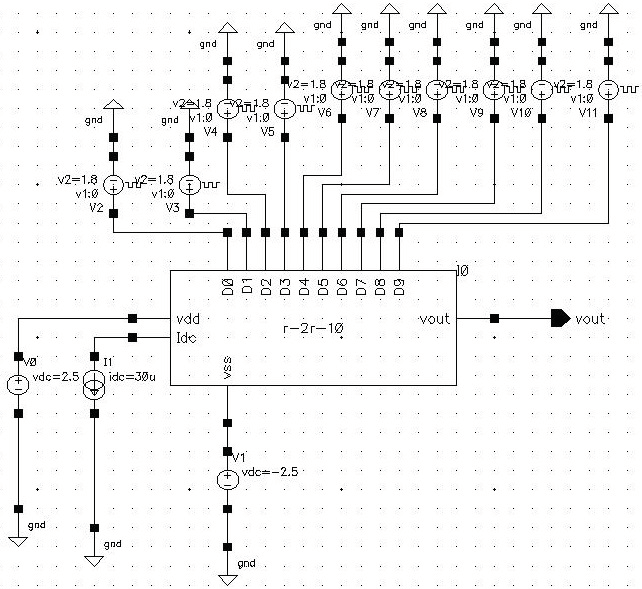

重定时R‐2R DAC、重定时比较器、运算放大器、采样/保持电路和触发器是设计时钟重定时SAR‐ADC所需的组成部分。反相输入端连接至采样保持电路以提供模拟信号,同相输入端连接至时变DAC输出端。与传统比较器相比,重定时时钟比较器的原理图在图12的瞬态波形中显示出更精确的结果。比较器输出为SAR电路提供正确的时钟值。许多研究人员提出了不同的架构来实现DAC和ADC 的设计。本文中,割集被应用于R‐2R网络的每个节点,每组可形成连通图。割集重定时[12]不会改变电路功能,但会影响割集中边的权重。在图13中由虚线指示的每个割集上添加延迟,并进行重新定时以提高设计的性能水平。每个2R电阻路径的节点连接到不同的时钟触发器。每位的分辨率通过重定时技术进行调节。所提出的N位割集R‐2R梯形网络与多时钟相位以及DAC测试原理图分别如图13和图14所示。

图15展示了重新定时SAR‐ADC架构的实际实现。在转换周期过程中,模拟输入信号被送入采样保持(S/H)电路以保持信号恒定。比较器模块将D/A转换器输出信号与S/H信号进行比较。当D/A转换器输出小于或大于S/H信号时,得到的最高有效位(MSB)为0或1,并存储在逐次逼近寄存器(SAR)中。完整的转换过程通过SAR使用二分搜索算法完成。由SAR生成的数字输入在内部DAC中被转换为模拟等效信号。在提出的工作中,内部DAC由不同时钟触发的触发器组成,用于将数字信号转换为模拟信号。内部转换过程由不同时钟速度控制。

仿真结果表明,所提出的逐次逼近型模数转换器与现有的逐次逼近型模数转换器设计相比具有低功耗特性。

五、结果与讨论

该提出的工作的主要贡献在于重定时DAC和比较器。采用多相时钟来设计SAR‐ADC原理图,如图15所示。R‐2R数模转换器的参考电压连接到重定时时钟的上升沿。所有触发器均放置在D₀, D₁, … Dₙ处,以获得更好的性能结果。然后将触发器移至设计中的高扇出位置,以最小化功耗。重定时 DAC的瞬态分析如图8和图9所示。对于8位和10位 SAR‐ADC的分辨率,测量结果如表II所示。时序元件(例如触发器(FFs)或锁存器等)放置在SAR ADC原理图的输出端,并通过在所有输入的多个相位上重新布置触发器实现重定时。毛刺引起的功耗在零延迟和实际延迟模型下均进行了计算。为了实现低功耗,在原理图设计中大量移动了触发器。

使用Spectre EDA工具进行结果分析,所获得的所提出的R‐2R DAC的DNL和INL值优于[19]。本文研究人员专注于采用0.18μm CMOS技术的 3+5分段DAC,且在[20]中设计了多bit Σ−Δ DAC,并从便携式数字音频应用中获得了低功耗低成本实验结果。所提出的重定时模拟DAC设计相比[19,20]功耗更低,且比[19]功耗降低43.7%。重定时比较器在存在模拟输入信号的情况下,提供了更好的采样和放大性能。比较器输出判决后紧跟时钟重定时。利用所提出的技术,在瞬态波形中去除了尖峰失真。异步SAR‐ADC设计方法已实现8、10和12位分辨率,适用于生物医学传感器。所提出的设计尺寸方法工具命名为基于混合的异步SAR‐ADC尺寸设计工具(HaSAST),用于自动晶体管尺寸调整。表I显示了所提出的研究设计与现有研究设计的采样率和功耗情况。异步SAR‐ADC的 [8]信噪失真比(SNDR)和功耗结果在表II中进行了比较。

表I. 10位分辨率逐次逼近型模数转换器输出的比较结果

| 参考文献 | [11] | [21] | [15] | 提出的工作 |

|---|---|---|---|---|

| 架构 | SAR | 流水线型 | SAR | 重新定时 |

| 电源电压(伏特) | 1.0 | 1.0 | 1.2 | 1.8 |

| 采样率(每秒采样数) | 240 | 200 | 280 | 250 |

| 功耗(毫瓦) | 0.68 | 5.37 | 2 | 0.267 |

表II. SAR ADC输出的比较结果

| 参考文献 | [8] | [8] | 提出的工作 | 提出的工作 |

|---|---|---|---|---|

| 分辨率(位) | 8 | 10 | 8 | 10 |

| 信噪失真比(分贝) | 49.7 | 52.1 | 53.2 | 59.3 |

| 峰值DNL (最低有效位) | 0.29 | 1.41 | 0.21 | 1.12 |

| 峰值INL(最低有效位) | 0.24 | 2.81 | 0.22 | 2.41 |

| 功耗(μW) | 328 | 328 | 267 | 267 |

VI. 结论

本文提出了一种新的实用方法,通过在模拟原理图中应用重定时技术来实现低功耗。该方法为任何模拟设计提供了一种性能更优的解决方案。文中分析了逐次逼近型模数转换器(SAR ADC)性能的实际实现。为了满足低功耗模数转换器的要求,在电路线路的多个相位上对时钟进行重新定时。因此,在不产生模拟到数字信号转换失配的情况下降低了功耗。所提出的R‐2R数模转换器的仿真结果表明,与现有设计相比增益误差有所降低。未来的工作中还可以采用预充电重定时电路来实现逐次逼近型模数转换器。

2617

2617

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?