一,源码下载

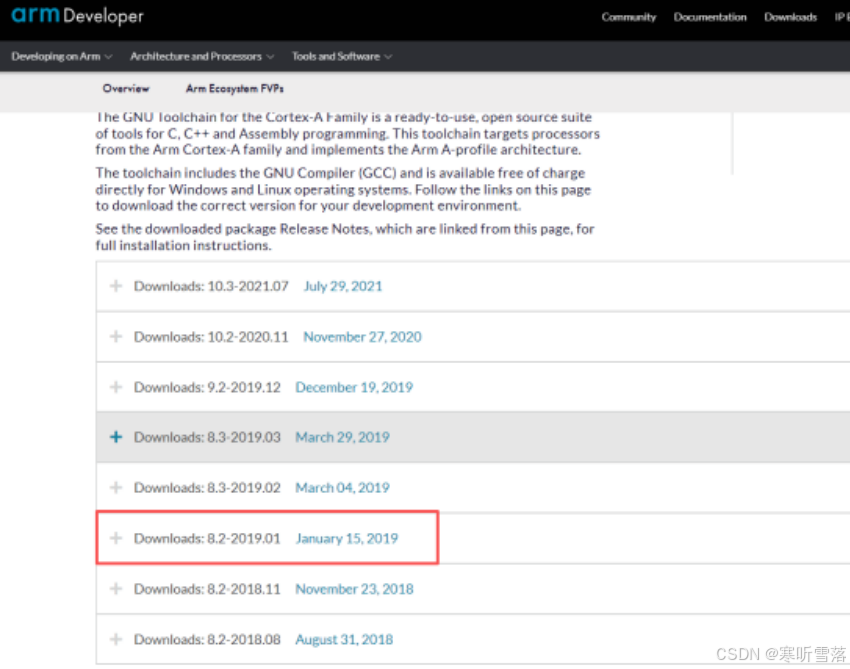

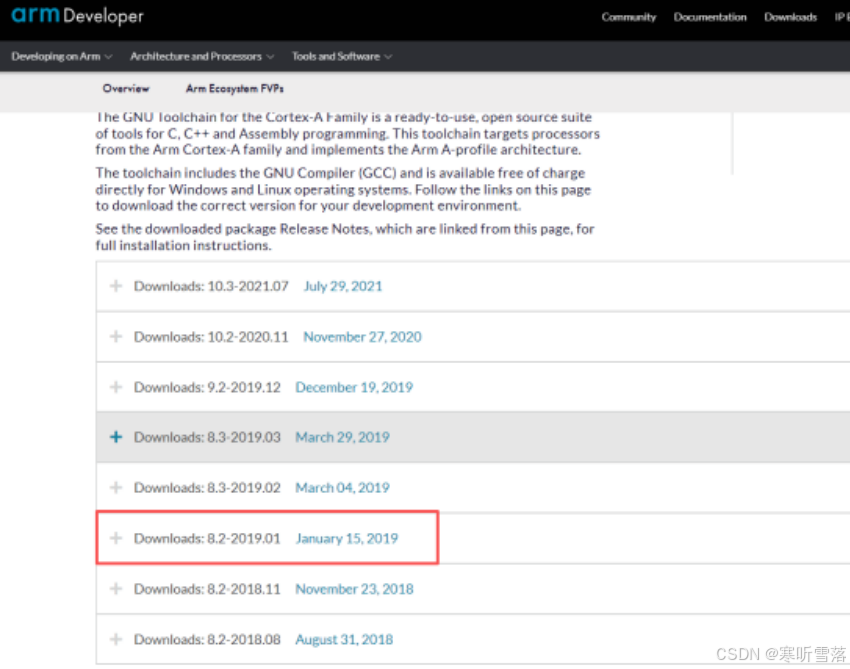

在如下网址下载编译链:

Downloads | GNU-A Downloads – Arm Developer

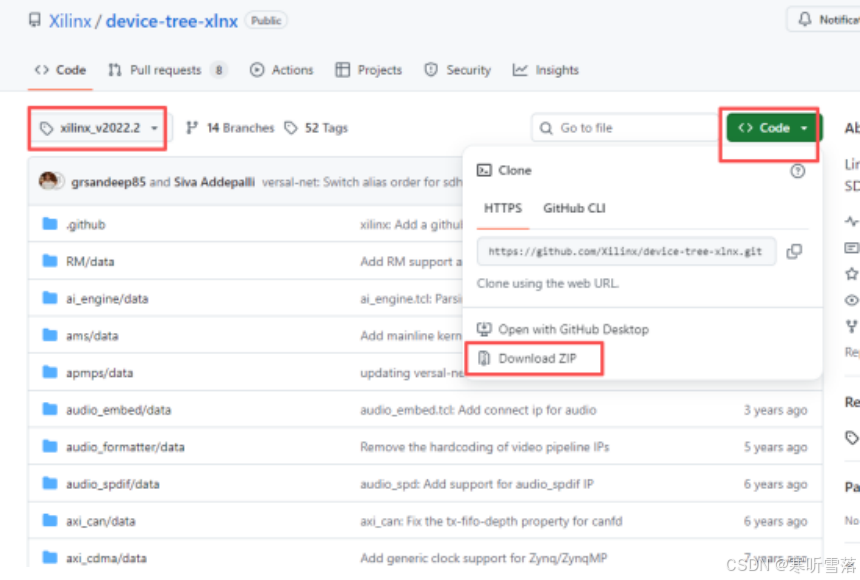

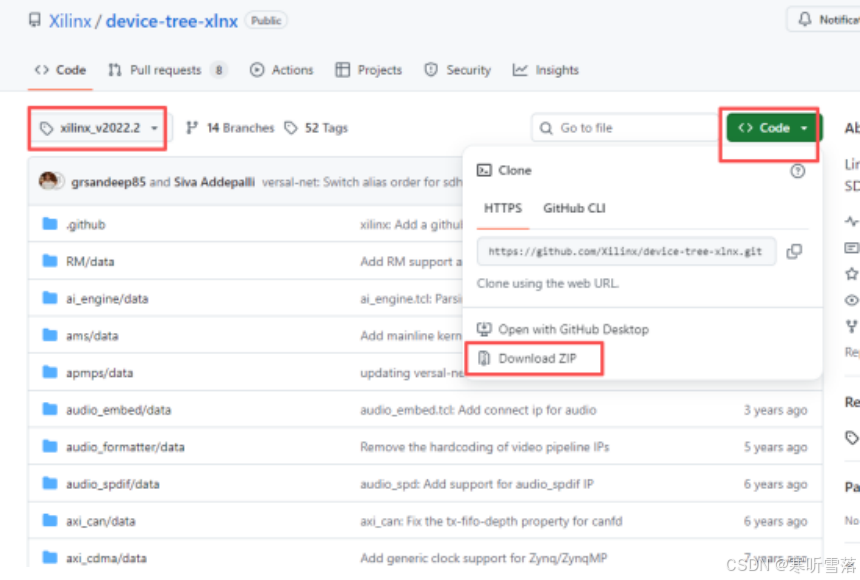

在如下网址下载设备树源码,选择这个分支:

GitHub - Xilinx/device-tree-xlnx at xilinx_v2022.2

在如下网址下载

uboot

源码,选择如下分支 :

Vivado TCL脚本:快速编译FPGA IP核与Block Design

Vivado TCL脚本:快速编译FPGA IP核与Block Design

本文介绍了如何利用TCL语言在Vivado中进行FPGA设计,包括设置环境变量、启动Vivado的不同方式以及基本TCL语法。重点讲述了通过TCL脚本编译生成IP核和block design工程的步骤,以zedboard为例,详细解析了配置2017.4版本在Linux下HDMI输出显示的流程,并提供了相关库的源码加载方法。

本文介绍了如何利用TCL语言在Vivado中进行FPGA设计,包括设置环境变量、启动Vivado的不同方式以及基本TCL语法。重点讲述了通过TCL脚本编译生成IP核和block design工程的步骤,以zedboard为例,详细解析了配置2017.4版本在Linux下HDMI输出显示的流程,并提供了相关库的源码加载方法。

一,源码下载

1745

1745